PRELIMINARY

# VF1 FPGA Family

# FEATURES AND BENEFITS

- ◆ The industry's first Variable-Grain-Architecture™ enables high-density, high-performance designs for a wide range of applications

- Architecture adapts to logic to enable synthesis-friendly, high-performance designs

- From three to six parallel inputs with all possible input combinations decoded in a single level

of high-speed logic

- Up to 32 parallel input functions with a subset of input combinations decoded in only two logic levels

- Available in four sizes with 12K, 20K, 25K, and 36K gates

- ◆ Variable-Length-Interconnect<sup>™</sup> delivers predictable performance and First-Time-Fit<sup>™</sup> layouts

- High-speed direct connectivity minimizes connection lengths for maximum performance

Variable-length connections span from two logic blocks to the entire chip, including I/Os

Result is optimal length resource for every net

- Flexible on-chip clocking options deliver up to 250MHz performance

- Four low-skew global clocks minimize clock variations within the chip

- Two on-chip phase-locked loops (PLLS) synchronize on-chip clocks with the system clock

- PLLs provide 1x, 2x, and 3x frequency multiplication for on-chip clock synthesis

- Clocks generated on-chip may be used as global clocks

- ♦ Vantis' hierarchical design methodology and DesignDirect<sup>™</sup> software provide Ease-of-Success<sup>™</sup> and First-Time-Fit

- DesignDirect software supports Verilog and VHDL hardware description languages (HDLs) for design flexibility

- Integrates easily with a variety of third-party front-end design entry, simulation, and synthesis tools

- Easy-to-learn mapping and layout software coupled with fast run times and superior quality

of results contribute to maximum productivity

- Vantis design software ensures First-Time-Fit results by examining a design prior to the placeand-route phase and determining whether or not it will fit into the chosen VF1™ FPGA

- Pin-locking feature ensures that I/O pin assignments will not change when moving a design from one VF1 FPGA size to another or when making design changes

- When making design changes or shifting density, special routing logic enables pin-locking with minimal performance degradation

- Allows shifting to higher or lower density FPGA without making changes to board layout

- ◆ Zero-power Edge Connect lines allow easy implementation of NOR functions on input lines

- Eight Edge Connect lines-two per side of the chip

- Input pins may be connected to these lines to implement NOR functions

- NOR functions consume zero power

- High-speed embedded dual-port memory simplifies the implementation of on-chip FIFOs and RAM

- Needs fewer bits than single-port architectures to implement FIFOs and register stacks

- Minimizes access time for both read and write cycles

- Over 6K bits of embedded SRAM in the largest VF1 FPGA device in 32x4 configurable blocks

- Specific configurations may be defined by the user

- Flexible I/O buffers allow interfacing to a wide variety of systems

- I/O buffers are compatible with both 3.3V and 5V I/O levels

- Programmable slew rates reduce output signal over/under shoot

- Three-state control for I/O bus interconnections allow multiplexing on long interconnect lines

- PCI-compatible I/Os, coupled with optional 33MHz and 66MHz PCI buffers, allow easy interfacing to PCI buses

- In-system programming via the built-in JTAG boundary scan port

- Allows VF1 FPGAs to be programmed after mounting on a printed-circuit board

- Reduces the need for on-board SPROM

- When coupled with pin-locking, allows design changes to be made and loaded without removing the device from the board

- Outperforms systems implemented with competitive reprogrammable FPGAs by 67% to 100%

- High-performance registered I/O improves chip speed

- On-chip phase-locked loops with the ability to double or triple input clocks, up to 200 MHz, allows the Vantis FPGA to run up to three times faster than the system clock

- Embedded memory has 5ns read/write access time for fast loads and stores

- Pipelined logic capable of 250 MHz operation supports the development of high-performance systems

| Features               | VF1012 | VF1020 | VF1025 | VF1036 |

|------------------------|--------|--------|--------|--------|

| Typical gates          | 12,000 | 20,000 | 25,000 | 36,000 |

| Array size (VGB)       | 14x14  | 18x18  | 20x20  | 24x24  |

| Logic flip-flops       | 784    | 1296   | 1600   | 2304   |

| DPSRAM blocks (32x4)   | 28     | 36     | 40     | 48     |

| Total RAM bits         | 3584   | 4608   | 5120   | 6144   |

| Clock pins             | 4      | 4      | 4      | 4      |

| Maximum I/Os           | 168    | 216    | 240    | 288    |

| Maximum I/O flip-flops | 336    | 432    | 480    | 576    |

Table 1. Available Devices in the VF1 Family

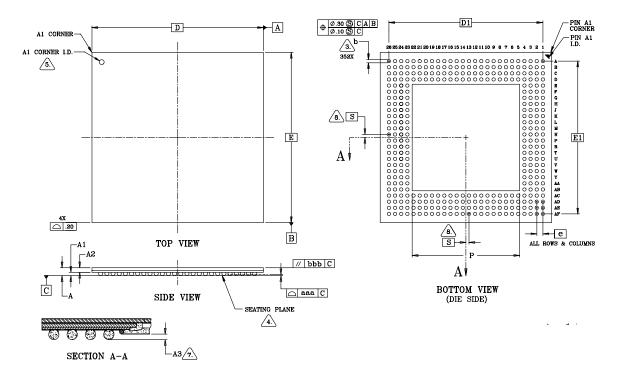

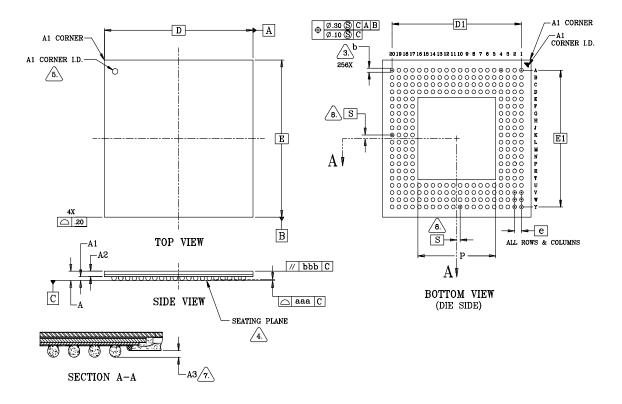

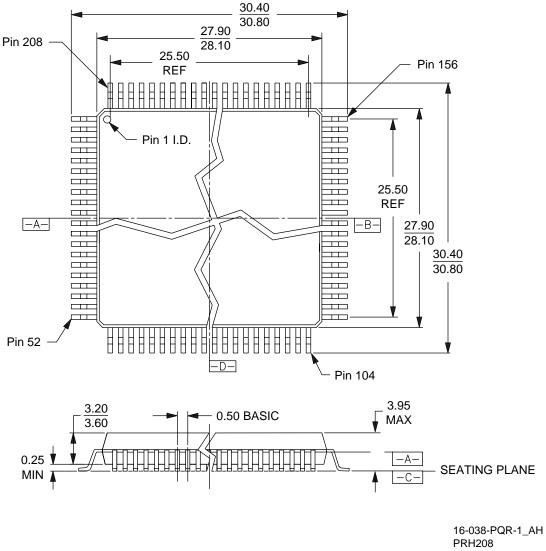

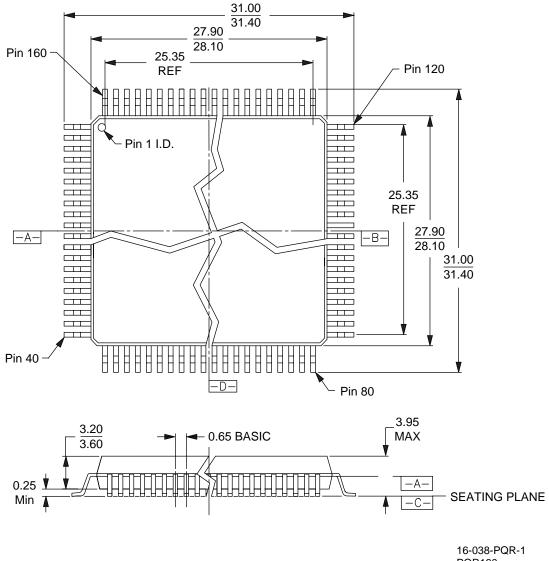

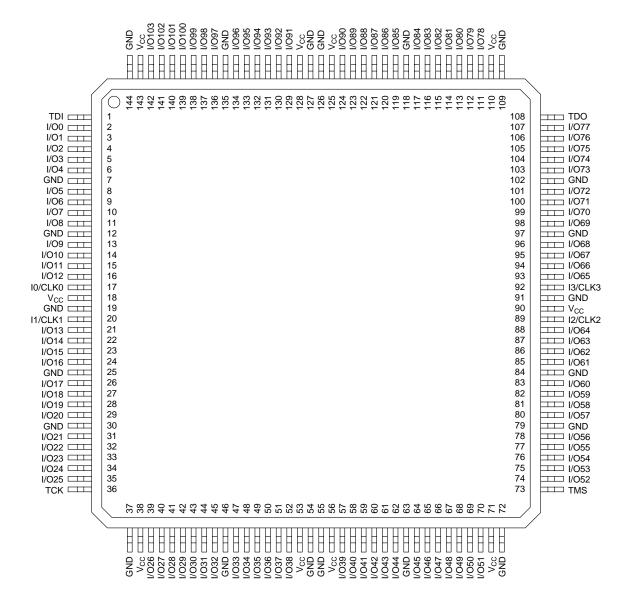

#### Table 2. Package Types and Total I/O Pins (including clock pins)

| Packages | VF1012 | VF1020 | VF1025 | VF1036 |

|----------|--------|--------|--------|--------|

| 352 BGA  |        |        | 244    | 292    |

| 256 BGA  | 172    | 208    | 208    | 208    |

| 208 PQFP | 168    | 168    | 168    | 168    |

| 160 PQFP | 128    | 128    |        |        |

| 144 TQFP | 112    |        |        |        |

# **OPERATIONAL DESCRIPTION**

The Vantis VF1 FPGA family offers FPGA designers a level of performance that was once available only to ASIC gate array designers. The VF1's Variable-Grain-Architecture minimizes the logic and interconnect resources needed to implement high-performance, complex functions. It supports logic configurations with three to six logic inputs with all possible input combinations decoded in a single LUT (look-up table) level. It also supports configurations with up to thirty-two partially-decoded parallel inputs that use only two LUT levels.

Coupled with high-performance Variable-Length-Interconnect (VLI) and from 3.6K to 6.1K bits of embedded dual-port SRAM, the Variable-Grain-Architecture delivers the best performance in the FPGA industry in a cost-effective solution that virtually guarantees design success.

Superior performance coupled with densities from 12K to 36K logic gates makes the Vantis VF1 family the best choice for high-performance, complex FPGA-based designs. Designers who create high-performance, high-density designs typically employ a design methodology based on hardware description languages (HDLs) such as Verilog or VHDL to speed the design process and manage complexity. The Vantis design methodology employs third-party HDL design tools coupled with Vantis' physical mapping and layout software.

The VF1 overview that follows describes a new, sophisticated FPGA architecture that includes a rich set of building blocks and interconnect resources. The VF1 family is manufactured in a state-of-the-art deep-submicron 0.18-micron ( $L_{effective}$ ) process technology for high performance and small die size. It uses four layers of metal interconnect to further enhance performance, reduce die size, and lower cost.

### Variable-Grain-Architecture

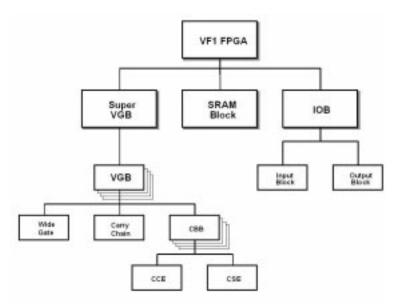

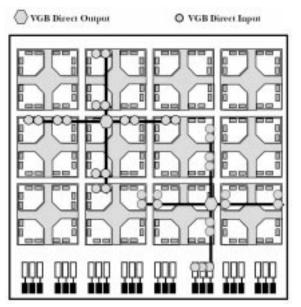

The VF1 FPGA family employs a new variable-granularity architecture that allows virtually any level of logic complexity to be implemented using minimum chip resources. It comprises three levels of logic hierarchy (Figure 1):

**Top Level: Super Variable-Grain-Block (Super VGB), SRAM, and I/O Block (IOB).** The highest level building block in the VF1 architecture is the Super VGB. It is a symmetrical structure, made up of four VGBs, that can be combined to create complex, high-performance functions using local building blocks and local interconnect resources. Supporting Super VGBs at the top level are dualport embedded SRAM and input/output blocks.

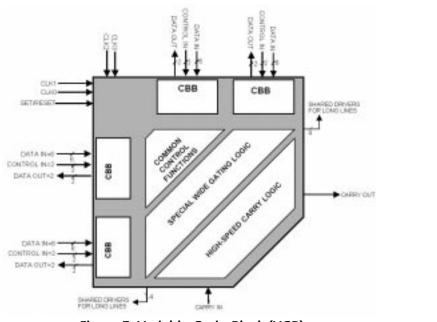

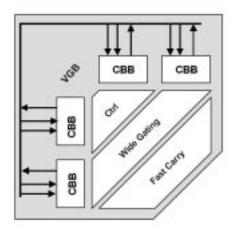

**Second Level: Variable-Grain-Block (VGB).** The next level, the VGB, includes four CBBs, logic to combine two or more CBBs to implement wide logic functions. Wide-gating logic supports complex functions with up to sixteen parallel inputs within a single VGB. The VGB also includes high-speed carry logic to build high-performance arithmetic functions and common control logic.

**Configurable Building Blocks (CBB).** The CBB is the lowest level building block. It includes six logic inputs, two 8-bit look-up tables (LUTs) to define logic functions, a flip-flop to save results, selectable outputs, and interconnections to other FPGA resources. A single CBB can implement two 3-input functions or one 4-input function using only the logic within the CBB.

VF1ds-002

Figure 1. VF1 Family Architecture Hierarchy

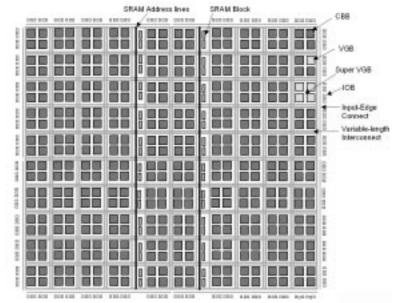

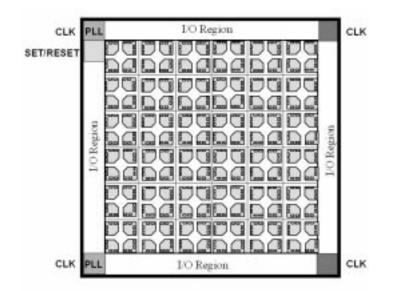

A VF1 FPGA (Figure 1) is arranged in a matrix of Super VGBs, separated by routing channels made up of interconnect resources called Variable-Length-Interconnect. Figure 2 shows the architecture of the VF1025 FPGA. The VF1025 consists of a 20x20 matrix of VGBs with two columns of embedded SRAM running vertically near the center of the device. Each column of SRAM is supported by dedicated SRAM address lines.

There are three IOBs for each row and column of VGBs on each side of the chip. The VF1025, therefore, has 60 IOBs per side, giving a total of 240 IOBs for the device. Two input Edge Connect lines on each side of the device (eight lines total) may be connected to their adjacent IOBs to implement an input NOR function. The Edge Connect lines consume no power, even when implemented as a NOR function

#### PRELIMINARY

A VGB in a VF1 FPGA corresponds roughly to one of the coarse-grained logic blocks found in competitive FPGA products—but a VGB is much more flexible. Its four CBBs can work independently as fine-grained elements to implement simple logic functions while using minimum resources, or they can be combined within the VGB and with other VGBs to handle very complex functions.

The following sections describe the VF1 architecture, starting at the CBB level and moving up the hierarchy.

### CBB

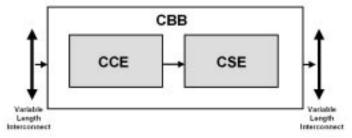

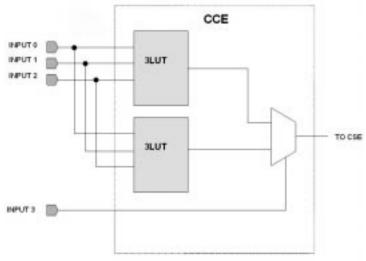

A CBB consists of two parts: a configurable combinatorial element (CCE) and a configurable sequential element (CSE) (Figure 3). In general terms, the CCE receives logic inputs and generates outputs. The CSE stores and routes the outputs.

Figure 3. Configurable Building Block (CBB)

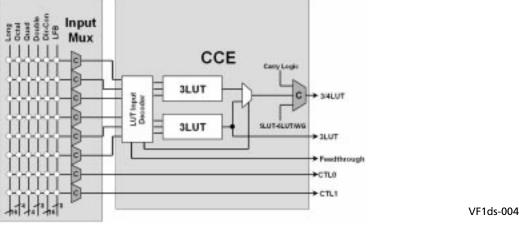

A CCE (Figure 4) contains two 8-bit, three-input look-up tables (3LUTs). The CCE receives inputs via VF1 Variable-Length-Interconnect routing resources, direct connections from adjacent VGBs, and local feedback within the VGB. (Inputs are covered in more detail later.) A LUT input decoder routes the inputs to the LUTs. The LUT input decoder spans all four CBBs in a VGB to enable the combining of CBBs to create five- and six-input functions. These wider functions are described later.

Bit patterns loaded into the LUTs define the output generated by each input combination.

Figure 4. Configurable Combinatorial Element (CCE)

#### Note:

A C in a mux block indicates that the block's function is set by the VF1 configuration bitstream and is not a logical block that can be controlled dynamically

The two 3LUTs may generate individual outputs (Figure 4), or they may be combined into a 16-bit 4LUT that decodes four inputs (Figure 5). If the 3LUTs operate independently, one output follows the Feedthrough route to the CBB output while the other goes to the following CSE via the 3/4LUT path shown in Figure 4.

The Feedthrough line coming from the Input Switch is a special high-speed path that allows longline routing resources to be routed from one line to another without going through a long-line switch matrix. The Feedthrough path provides better performance than the switch matrix path. This is covered in the *VGB Interconnect* section.

Figure 5. Four-Input CCE Configuration

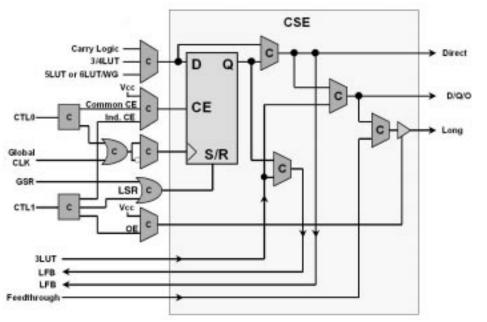

The CSE (Figure 6) receives the outputs from the CCE via the top mux on the left (along with Carry Logic, CCE, and Wide Gating inputs) and the Feedthrough line on the bottom left. The top mux output may be stored in the CSE register or it may bypass the register and go directly to an output via a second mux. The output of the second mux goes to a direct connect line that connects to other VGBs and IOBs, and to a local feedback (LFB) line that connects to other CBBs within the same VGB.

The Feedthrough line from the lower 3LUT can be routed to VLI resources and to a second LFB line.

Figure 6. Configurable Sequential Element (CSE)

CSE register control signals consist of a clock enable (CE), a clock, and a direct set/reset. The register clock enable may be a common enable, a separately generated independent enable, or it may be tied to  $V_{cc}$ .

Both the register clock (CLK) and the set/reset signal (S/R) may be configured to meet specific design requirements. The polarity of the clock can be selected by configuring the mux that precedes the clock input to the register. The set/reset source may be configured as either local (LSR) or global (GSR). If a local set/reset is selected, it applies to all the registers in one VGB.

The Feedthrough line can be routed to a long interconnect line via a dedicated driver. The driver can be enabled by either being tied to  $V_{cc}$  or by a locally-generated output enable (OE). This function allows a signal from a long interconnect line to enter a Super VGB via a CBB input, bypass CBB logic, and connect directly to a shared Super VGB long-line driver. The long-line driver connects the signal to another long interconnect line. This is an alternative to using a switch at an intersection of long lines. It adds additional drive to the signal, allows the signal to be connected to lines that are parallel to the original line as well as perpendicular, and may have less delay than a switch at a line intersection.

### VGB

The second level in the VF1 FPGA family hierarchy is the Variable-Grain-Block, or VGB (Figure 7). A VGB contains four CBBs plus common control functions, wide gating logic, and high-speed carry logic.

A VGB is a very flexible structure that can be combined in a variety of ways to create very simple or very complex logic structures. A VGB can be viewed as a fine-grained architecture when each CBB is used to implement a separate logic function. It becomes a coarse-grained architecture when the entire VGB is dedicated to a single function.

Figure 7. Variable-Grain-Block (VGB)

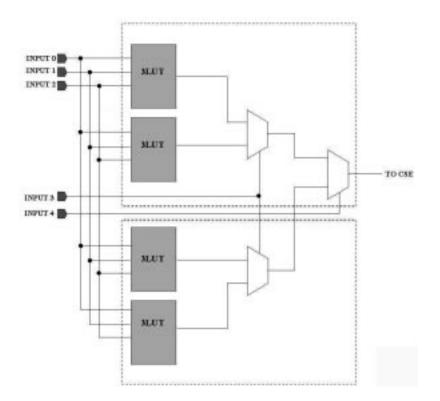

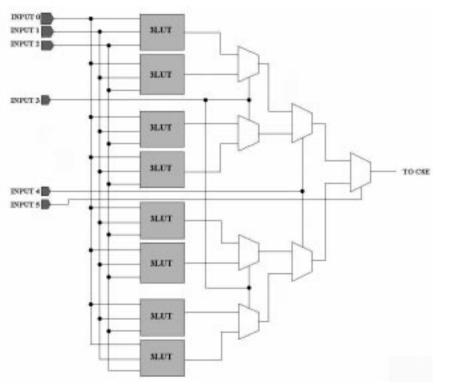

Just as the LUTs within a single CBB can be combined to create complex functions, the CBBs within a VGB can be combined. By combining the four 8-bit 3LUTs in two CBBs into a single 32-bit 5LUT, all possible combinations of five logic inputs can be decoded (Figure 8). By combining all four CBBs in a VGB into a single 64-bit 6LUT, all possible combinations of six inputs can be decoded (Figure 9). The combined output becomes an input to one of the CSEs (Figure 6, upper-left mux).

VF1 FPGA Family

Figure 8. Five-Input Function Using Two CBBs

Figure 9. Six-Input Function Using Four CBBs in One VGB

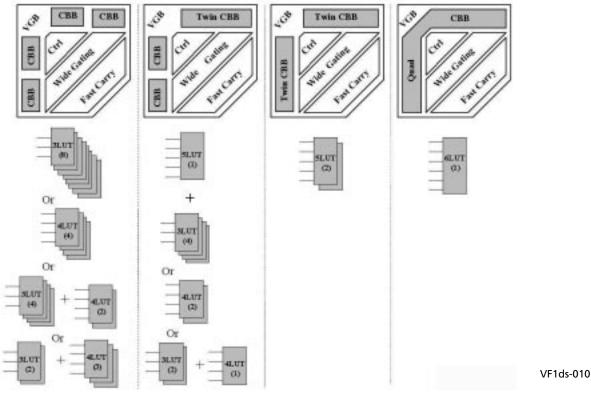

Figure 10 shows some of the possible fully-decoded combinations that can be implemented in a single VGB. The left VGB in Figure 10 shows some combinations that are possible without combining CBBs. A single VGB can implement eight three-input functions, or four four-input functions, or four three-input functions plus two four-input functions. Other combinations are also possible.

Figure 10. Examples of Logic Configurations in One VGB

The second VGB in Figure 10 shows some possible combinations when two CBBs are combined while two CBBs function independently. The combined CBBs form a 5LUT that implements a five-input function, while the independent CBBs implement various combinations of three- and four-input functions. The third VGB is configured for two five-input functions, and the fourth is configured for a single six-input function.

In many cases, however, an application does not require the decoding of every possible combination of a set of inputs. In these cases, configuring CBBs in combinations other than those described above can save device resources. For example, two CBBs may be configured as separate 4-input elements with their outputs multiplexed to decode an 8-input function using only two CBBs. Since each CBB decodes 16 combinations of four inputs, this configuration decodes 32 possible combinations of eight inputs.

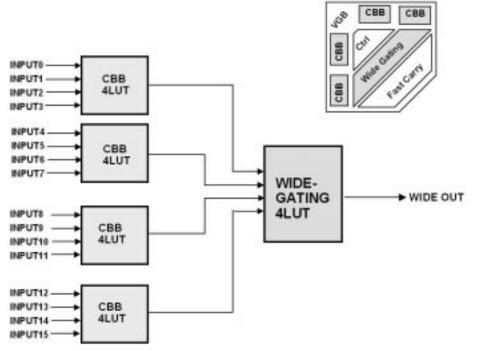

Special wide-gating logic that is part of the VGB architecture is used to implement configurations up to 32 inputs in only two logic levels. The wide gating logic includes a dedicated 4LUT that is used to combine CBBs into functions with up to sixteen inputs using all four CBBs in one VGB (Figure 11). In this example, each CBB within a VGB is configured to fully decode four inputs.

Each of the four CBBs generates an output that becomes an input to the 4LUT in the wide gating logic. The 4LUT fully decodes the four inputs from the CBBs.

Figure 11. Decoding 16-Input Function Using Wide Gating Logic

The configuration in Figure 11 does not decode all 65,536 possible combinations of sixteen inputs. Instead, it decodes sixteen combinations of four inputs in each CBB for a total of 64 possible combinations. The wide-gating 16-bit LUT decodes sixteen possible combinations. The circuit, therefore, decodes 1024 combinations (16\*64). For most logic functions this is quite adequate, and it is accomplished using only the high-speed, short-intraconnect logic contained in a single VGB.

### Super VGB

The third hierarchical level is the Super VGB (Figure 12). It consists of four mirrored VGBs with four sets of shared long-connect multiplexers/drivers. The symmetrical arrangement of the Super VGB improves logic density and minimizes interconnect length for implementing complex functions. Inputs can come from any direction on the chip and outputs can go in any direction. Compared to architectures that force logic paths to flow in one general direction, this Super VGB symmetry shortens signal paths and thus improves both performance and density.

Figure 12. Super VGB Architecture

VF1ds-012

Each Super VGB has four sets of shared drivers, each set pointing in a different direction on the chip. These drivers allow a Super VGB to connect to the VLI lines (see *Interconnecting VGBs*) that provide general signal routing throughout the chip. Each set of shared drivers contains four individual drivers for a total of sixteen drivers in each Super VGB.

In addition to general interconnection of VGBs to long interconnect lines, the shared drivers are used to implement logic functions with up to 32 parallel inputs. Two 16-input functions (Figure 11) can be multiplexed using a shared driver, thus providing a 32-input function that decodes 2,048 possible conditions.

### Interconnect Resources

In today's deep-submicron technologies, interconnect length often has a greater impact on device performance than gate or logic-block delays. The Vantis VF1 family minimizes most interconnect delays by providing multiple levels of interconnect resources that often allow complex functions to be implemented completely within a VGB or Super VGB. These complex functions, however, must be connected to other VGBs and to I/O blocks, therefore longer routing resources are needed.

The VF1 architecture provides three levels of high-performance interconnect resources:

- Local feedback allows CBB outputs to feed back to the inputs of all CBBs within the same VGB.

- Inter-VGB Direct connect routes the outputs of every CBB in every VGB to the inputs of eight nearby VGBs and to IOBs.

- **Variable-Length-Interconnect** resources provide programmable interconnects that may span two VGBs, four VGBs, eight VGBs, and the entire FPGA.

These interconnect resources provide highly efficient routes for making component connections while maintaining maximum performance levels. In addition to maximizing performance, the VF1 family interconnect methodology allows Vantis' optimization, mapping, and place-and-route software tools to achieve First-Time-Fit results. It also simplifies pin locking and density shifting when moving from one VF1 FPGA to another within the same package type.

### Local Feedback

The earlier description of CBBs shows how local feedback lines (LFBs) are routed back from the CBB outputs toward the CBB inputs. These LFBs are then routed to the inputs of every CBB in the same VGB (Figure 13). Local feedback provides a very powerful, high-performance routing resource that works entirely within the VGB and uses no general routing resources.

Figure 13. Local Feedback

### Inter-VGB Direct Connect

Every CBB in every VGB has a direct-connect output that connects it to the inputs of two CBBs in eight other nearby VGBs (Figure 14). The direct connect routing shown in the upper left portion of Figure 14 shows how direct-connect lines are routed when the output CBB is not near the edge of the VF1 FPGA. The routing shown in the lower right shows how a direct-connect output connects to three IOBs when the output CBB is near the edge of the device.

VF1ds-014

Figure 14. Inter-VGB Direct Connect

Only two direct-connect routes are shown in Figure 14, but every CBB in every VGB has the same direct-connect routing resources. The direct-connect capability allows VGBs that are adjacent to each other to be combined in very powerful logic structures without using slower general routing resources.

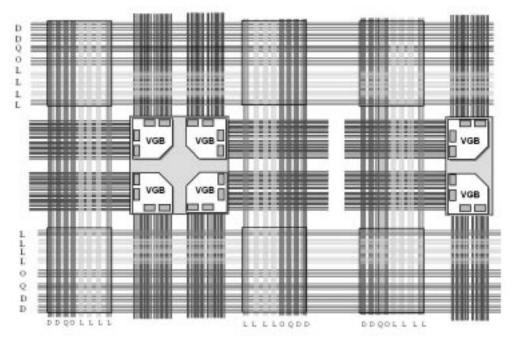

#### Variable-Length-Interconnect Resources

The VF1 family provides four types of Variable-Length-Interconnect resources that run in channels between Super VGBs, both horizontally and vertically (Figure 15). Two groups of interconnects run within each channel. Each group of interconnects includes the following:

- **Long Connect:** 16 lines run from edge to edge on the chip, both vertically and horizontally.

- Octal Connect: 4 lines span 8 VGBs both horizontally and vertically.

- Quad Connect: 4 lines span 4 VGBs (two Super VGBs) both horizontally and vertically.

- **Double (or Twin) Connect:** 8 lines span 2 VGBs both horizontally and vertically.

VF1ds-015

Figure 15. Variable-Length Interconnect Resources

The sixteen long-connect lines can be used to implement three-state buses, whereas octal, quad, and double connect lines cannot. CBBs can connect directly to octal, quad, and double connect lines, but cannot connect directly to long lines. A VGB output connects to a long line resource by using a shared long-line driver in a Super VGB.

VLI lines change direction by connecting with other VLI lines at switch matrixes located at the intersections of the horizontal and vertical groups of lines. Long lines, however, can bypass the switch matrix by using a CBB Feedthrough line, as described in the CBB section.

VF1 FPGA Family

### Interconnect Performance Considerations

Short connections deliver better performance than long connections. Interconnect resources, in order of performance, are:

- ◆ Local feedback within a single VGB

- Direct-connect lines between VGBs and from VGBs to IOBs

- Dual lines that span two VGBs

- Quad lines that span four VGBs

- ◆ Octal lines that span eight VGBs

- ◆ Long lines that span the entire VF1 FPGA

Vantis' DesignDirect software selects routing resources and calculates timing for both routing and logic delays. Designers can control routing indirectly by specifying timing constraints that must be met by the DesignDirect tools.

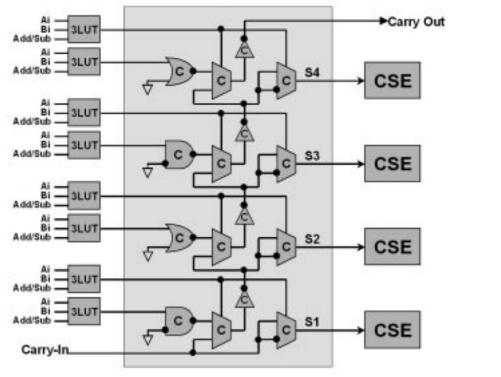

### **Carry Logic**

Every VGB includes high-speed carry logic that facilitates the implementation of arithmetic circuits such as adders, subtracters, bit shifters, up/down counters, and comparators. To improve arithmetic speed, the carry chain within a VGB is placed between the CCEs and the CSEs within each CBB (Figure 16).

Figure 16. Carry Routing Within a VGB

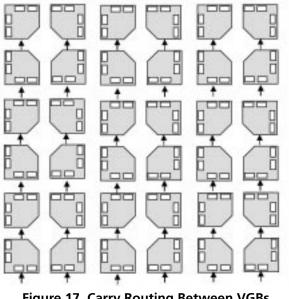

A VGB receives a carry input from a preceding VGB in the arithmetic chain, and generates a carry for the following VGB (Figure 17). The carry chain between VGBs starts with the bottom VGB in a column and proceeds vertically through the column. Each column of VGBs has its own carry chain.

Figure 17. Carry Routing Between VGBs

### **Embedded Memory**

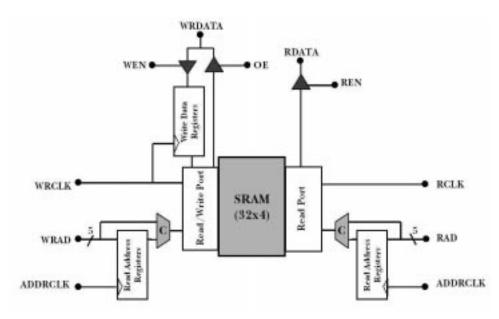

Every VF1 FPGA family member includes embedded memory configured as 32x4 dual-port SRAM blocks (Figure 2). The dual-port configuration (one read/write port and one read port) allows an application to read from the read port while it is reading from or writing to the read/write port. This allows applications such as FIFOs and register stacks to run much faster, and requires only half as many memory bits to implement as a single-port RAM would require.

Specific memory structures are created by the Vantis DesignDirect software and are implemented by the configuration bitstream. In addition, initial memory contents can be loaded at configuration time.

Figure 18. VF1 Dual-Port SRAM

VF1ds-017

The embedded memory is implemented as two columns of memory blocks that run the full length of the FPGA device (Figure 2). Two columns of Super VGBs (four columns of VGBs) run between the memory columns, and additional columns of Super VGBs are outside the memory columns. This configuration minimizes the distance between Super VGBs and embedded memory, thus allowing shorter interconnects and faster memory access. It also simplifies density shifting and pin locking features. Table 3 lists the memory capacity of each VF1 FPGA family member.

|                        | VF1012  | VF1020  | VF1025  | VF1036  |

|------------------------|---------|---------|---------|---------|

| VGB Array Size         | 14 x 14 | 18 x 18 | 20 x 20 | 24 x 24 |

| Embedded Memory Blocks | 28      | 36      | 40      | 48      |

| Total Memory Bits      | 3584    | 4608    | 5120    | 6144    |

| Table 3. VF1 Embedded Memory Capacity | able 3. VF1 Embedded | Memory Capacity |

|---------------------------------------|----------------------|-----------------|

|---------------------------------------|----------------------|-----------------|

#### Note:

For a detailed description of memory access modes and timing, refer to the "VF1 Dual-Port SRAM Architecture and Timing" Technical Note.

One port of each SRAM block is a read/write port and the other is a read-only port (Figure 18). The read/write port on the left of Figure 18 consists of a write/read address input (WRAD) that may be stored in Read Address Registers, or may bypass the registers and go directly to the Read/Write Port. For write operations, the write address is stored in the Read/Write Port and write data is stored in the Write Data Registers.

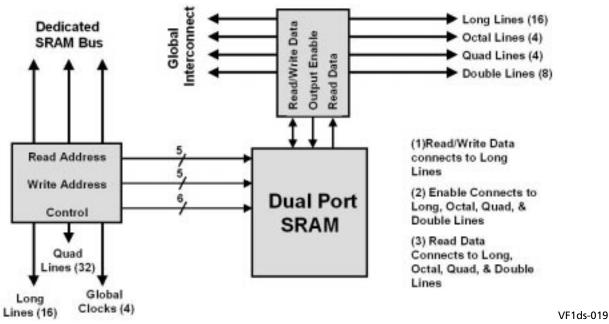

Figure 19. VF1 Dual-port SRAM Routing Resources

Memory read and write addresses come from dedicated SRAM address buses (Figure 19). There are five read address lines, five write address lines, and six control lines (including global clocks) connected to each 32x4 memory block. The SRAM address bus is driven by VLI quad and long lines. Read/write data for the read/write port connect to VLI long lines. Read data from the read port and output enable lines connect to any VLI resources.

The VF1 embedded memory supports six single- and dual-port synchronous and asynchronous read and synchronous write operations. All single-port operations use the read/write port. The read-only port is used for dual-port operations. All write operations are synchronous. Read operations may be synchronous or asynchronous.

In dual-port operations, it is possible to read from the read port at the same time that the read/ write port is performing a read or write. It is also possible to access the same address simultaneously. If the read/write port writes to an address at the same time that the read port reads the address, the read port will read the old contents of the address until the next clock cycle, at which time the contents of the address will change to the new data.

The mode diagrams that follow represent memory behavior and not physical memory implementation. The modes are:

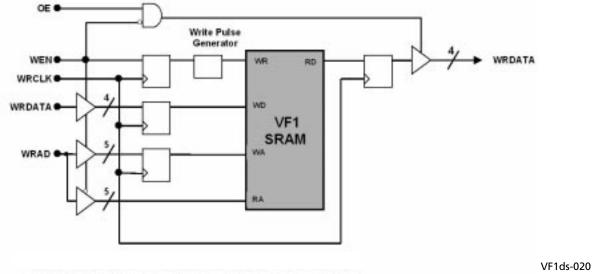

- **Single-port synchronous read/write (Figure 20).** Both read and write operations are synchronized by WRCLK. Synchronous read operations register read data on the output.

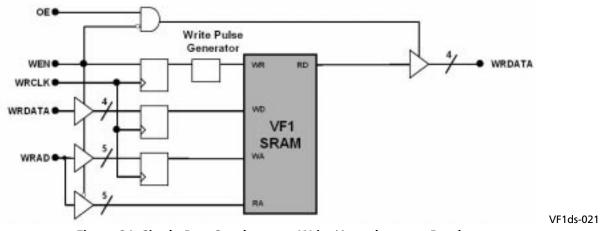

- **Single-port synchronous write/asynchronous read (Figure 21).** This operation is identical to the synchronous read/write except that read data is not registered on the output.

- Single-port synchronous write/asynchronous read, registered read address (Figure 22). The read address is registered prior to the read/write port using a separate clock (AD-DRCLK), rather than the WRCLK that is used for write and synchronous read operations.

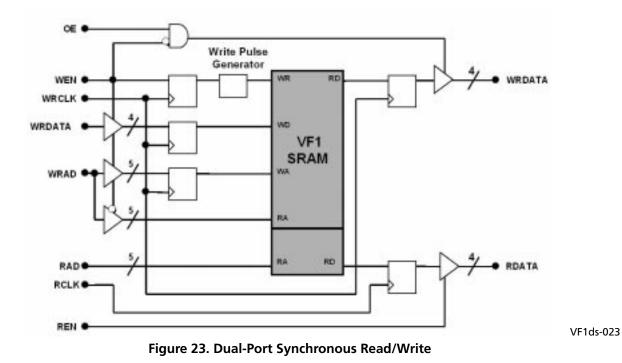

- **Dual-port synchronous read/write (Figure 23).** This function adds a second read port to the single-port synchronous read/write operation. The read port functions identically to the read operations in the read/write port.

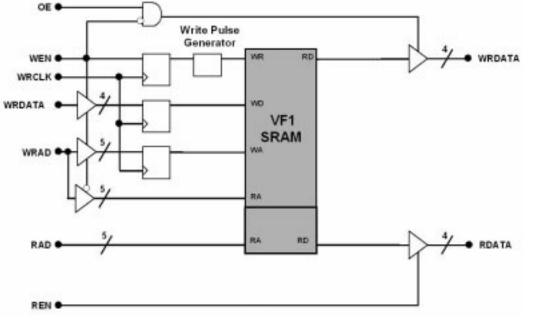

- **Dual-port synchronous write/asynchronous read (Figure 24).** In this mode the read port performs asynchronous reads while the read/write port performs synchronous writes or asynchronous reads.

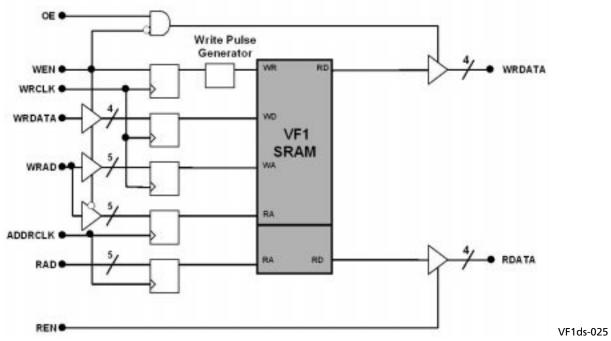

- Dual-port synchronous write/asynchronous read, registered read address (Figure 25). The read port performs registered address read operations.

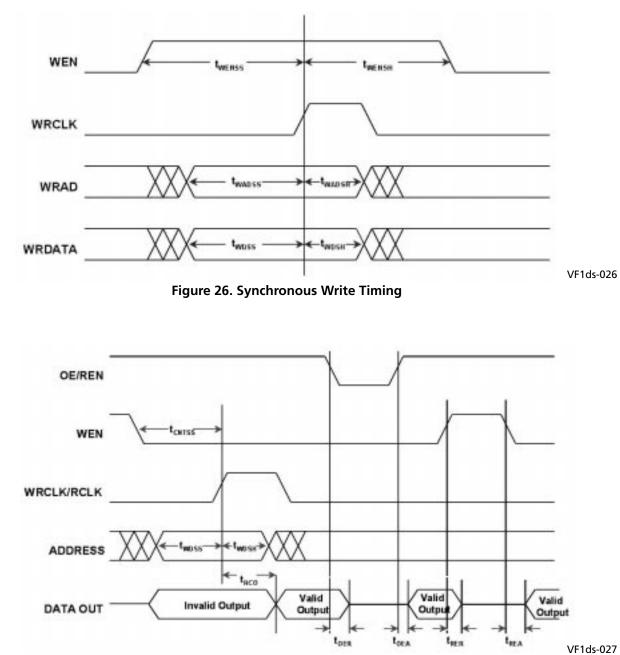

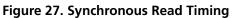

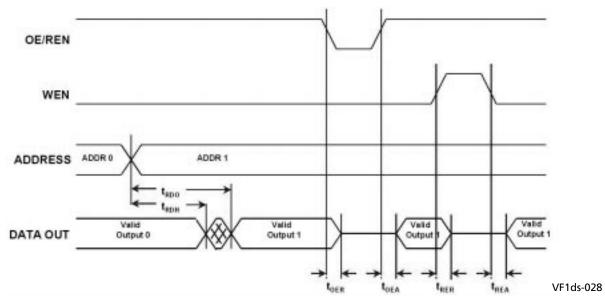

The timing diagrams in Figures 26-29 show the timing relationships for each mode. Write timing applies to the read/write port only, and read timing is identical for each port.

### Note:

More detailed descriptions of these memory modes, plus detailed timing diagrams of each mode, are found in the "VF1 Dual-Port SRAM Architecture and Timing" Technical Note.

Figure 20. Single-Port Synchronous Read/Write

#### Note:

Diagram only represents behavior and not physical implementation

Figure 21. Single-Port Synchronous Write/Asynchronous Read

Figure 22. Single-Port Synchronous Write/Asynchronous Read, Registered Read Address

VF1 FPGA Family

Figure 24. Dual-Port Synchronous Write/Asynchronous Read

Figure 28. Asynchronous Read Timing

Figure 29. Asynchronous Read Timing with Registered Read Address

### Input/Output Blocks

Input/output blocks (IOBs) provide an interface between the internal logic functions of the VF1 FPGA and the remainder of the system in which the device is installed. IOBs support input and output functions, and interface the VF1 FPGA to both 3.3V and 5V I/O levels.

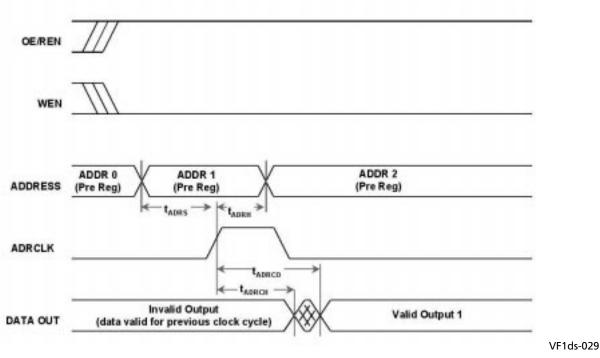

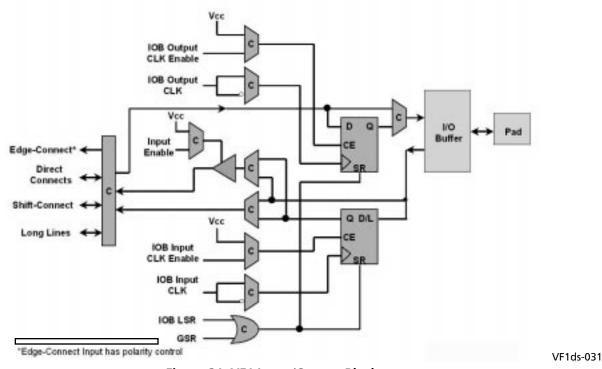

IOB regions lie on all four sides of the FPGA (Figure 2). Each programmable IOB includes a pad, input logic, and output logic (Figure 30). The input and output sections function separately from each other, sharing only the I/O pad and common Set/Reset logic. The common Set/Reset signal is either the VF1 Global Set/Reset, or a local set/reset.

Separate input and output enable signals allow an IOB to function as both an input pin and an output pin in a design.

Figure 30. VF1 Input/Output Block (IOB)

Figure 31 gives a more detailed view of the programmable IOB. Both the input and output sections share a common set/reset signal. The set/reset may be locally-generated (LSR), or it may be the VF1 global signal (GSR). The input and output sections use separate clocks and separate clock enables.

The IOB input section includes an input buffer, input register/latch, and programmable logic to connect the input to appropriate interconnect lines. The input signal may either be registered or bypass the register. When the register is used, a delay may be inserted between the input pad and the register (Figure 32) to ensure zero hold time for the register when using an external clock. The delay is not used when an on-chip PLL generates the clock (refer to the PLL description later in this document).

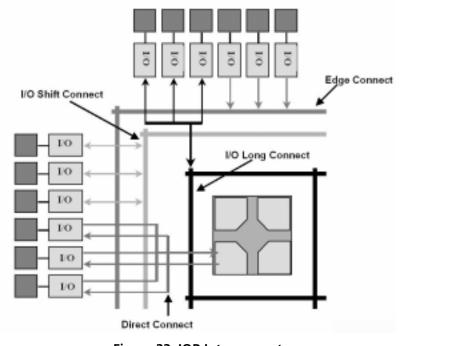

Input signals may be routed to long lines, to shift-connect lines, to edge-connect lines, or directly to VGBs via direct connect lines. The long-line connections may be permanently enabled by tying to  $V_{cc}$ , disabled by tying to GND, or dynamically controlled via a locally-generated signal. Other connections are established when the VF1 FPGA is configured. Connections are described in more detail following the IOB output description.

Figure 31. VF1 Input/Output Block

#### Note:

Edge-Connect input has polarity control

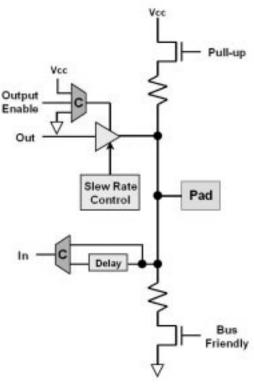

The IOB output section includes programmable interconnections from the VF1 logic, an output register, and an output buffer with programmable slew rate control (Figures 31 and 32). Output data may come from direct connect lines, long lines, or shift-connect lines. The output may be permanently enabled or disabled by tying to  $V_{cc}$  or GND, or controlled dynamically by a locally-generated enable signal.

### Figure 32. VF1 I/O Buffer

The VF1 I/O buffer (Figure 32) offers designers a wide selection of programmable capabilities:

- ◆ Three-state control capability for interfacing to buses

- **Programmable pull-up resistor** for a weak high bias

- ◆ **Programmable Bus-Friendly**<sup>™</sup> **architecture** to hold the last output value when the IOB goes into high-impedance mode

- Output slew rate control to reduce ringing

- Programmable input delay allows zero hold time from external clock

- IEEE 1149.1 boundary scan capability to simplify board testing

Figure 33. IOB Interconnect

IOBs may connect to long lines, shift-connect lines, direct-connect lines, and Edge Connect lines (Figure 33). Long-line connections allow any VGB anywhere in the VF1 FPGA to be connected to IOBs. Long-line connections are made to routing resources that are perpendicular to the edge of the device where the IOB is located. Each IOB may connect to two long-line channels.

Shift-connect lines give the VF1 FPGA family a very powerful pin-locking capability when a design moves a design to either a higher or lower density VF1 FPGA. Shift-connect lines expand an IOBs long-line connection span from two channels to four, making it much more efficient to lock pin assignments when shifting from one device density to another.

Direct-connect lines connect IOBs directly with VGBs that are near the edge of the VF1 FPGA. These are the fastest connections between logic elements and I/O elements.

Edge Connect lines apply to inputs only. An IOB input section may be configured to connect to an Edge Connect line as well as another data line. The Edge Connect lines (two per side of the VF1 FPGA) are used to implement input NOR functions on IOB inputs.

### **Global Interconnect and PLL**

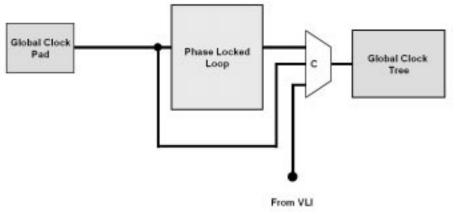

Global signals in the VF1 family include four global clocks and a global set/reset function (Figure 34). The Set/Reset signal input is at one corner of the VF1 FPGA. The four global clock inputs are distributed with one CLK input at each corner. Two of the global clocks may be applied to embedded phase-locked loop (PLL) circuits for clock deskewing and frequency multiplication.

Figure 34. VF1 Global Interconnect

All four global clocks have individual clock trees that distribute them throughout the VF1 FPGA (Figure 35). These clock trees cannot be subdivided. Clocks associated with PLLs may either bypass the PLL circuit or may be applied to the PLL with the PLL output applied to the clock tree. In addition, clocks may be generated within the VF1 FPGA and distributed using the global clock tree (the VLI input in Figure 35).

Maximum input frequency on any clock pin is 250 MHz. Operation at the maximum frequency requires certain design considerations. Refer to Vantis applications notes for guidelines on high-frequency designs.

Figure 35. Global Clocks and PLL

VF1ds-035

### PLL

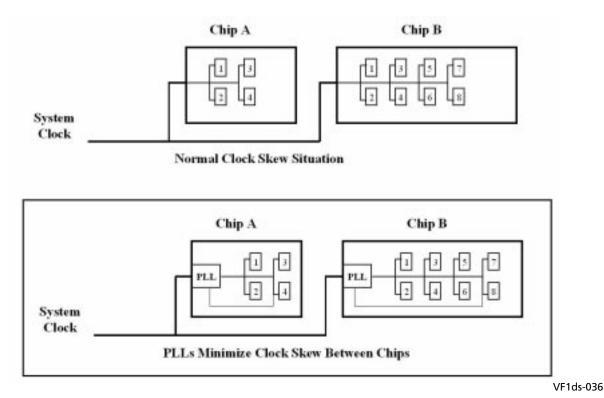

The embedded analog PLL circuits can be used to deskew clocks from one chip to another and to synthesize on-chip clocks using an external reference frequency (usually an external clock input).

Figure 36. Deskewing Clocks with PLLs

Clock skew from one chip to another robs a system of much of its performance by delaying the generation of reliable outputs from larger chips. When a system clock is applied to two chips of different sizes (Figure 36), the clock will propagate through the chips at different rates. For example, the clock will reach flip-flop 4 in Chip A (Figure 36, upper diagrams) much sooner than it reaches flip-flop 8 in Chip B. Process and environmental variables also contribute to clock skew within a chip.

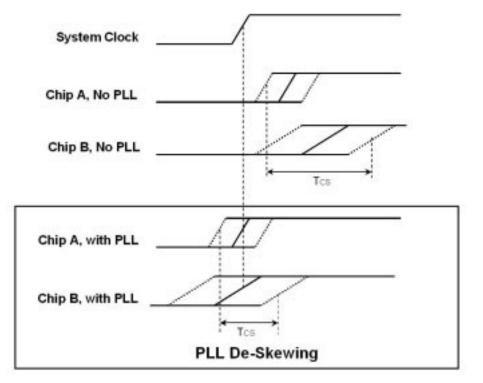

The waveforms (Figure 37, upper waveforms) show the results of skew in the two chips. The dotted lines in the chip waveforms show when the system clock reaches the first flip-flop in the chip and when it reaches the last. The solid line shows when the clock reaches the mid-point along each chip's clock trunk.

A PLL can "shift" the reference clock within a chip and reduce the time that it takes for the chip to generate its output. The PLL works by monitoring the reference clock and the clock signal at the end of the chip's clock trunk (Figure 36, lower diagrams). It then shifts the clock phase so that the shifted clock pulse reaches the end of each chip at the same time that the system clock reaches the chip input. The PLL effectively synthesizes a new clock at the same frequency as the system clock, but slightly shifted in phase (Figure 37, lower waveforms).

Figure 37. PLL Waveforms for Deskewing Clocks

| Symbol                 | Parameter                                                                                 | Min | Max | Unit | Output Frequency |

|------------------------|-------------------------------------------------------------------------------------------|-----|-----|------|------------------|

| t <sub>RISE</sub>      | Input clock rise time                                                                     |     | 5   | ns   |                  |

| t <sub>FALL</sub>      | Input fall time                                                                           |     | 5   | ns   |                  |

| t <sub>INDUTY</sub>    |                                                                                           | 40  | 60  | %    |                  |

| F <sub>CLK1</sub>      | Input Clock Frequency with multiplication factor of 1                                     | 30  | 150 | MHz  | 30 to 150 MHz    |

| F <sub>CLK2</sub>      | Input Clock Frequency with multiplication factor of 2                                     | 16  | 100 | MHz  | 32 to 200 MHz    |

| F <sub>CLK3</sub>      | Input Clock Frequency with multiplication factor of 3                                     | 16  | 66  | MHz  | 48 to 198 MHz    |

| t <sub>INCLKSTB</sub>  | Input Clock Stability (between adjacent clocks)                                           |     | 100 | ps   |                  |

| t <sub>LOCK</sub>      | Time for PLL to acquire lock                                                              |     | 30  | μs   |                  |

| t <sub>TOTJITTER</sub> | Total jitter on PLL output (both accumulated and phase-to-phase measures as peak-to-peak) |     | 500 | ps   |                  |

| t <sub>OUTDUTY</sub>   | Duty cycle for PLL output                                                                 | 40  | 60  | %    |                  |

The PLL can also be used to synthesize on-chip clocks that are multiples of the system clock frequency, up to a maximum of 200MHz. For example, if the system clock operates at 66MHz, the on-chip PLL can double the clock to 132MHz or triple it to 198MHz. If the system clock runs at 100 MHz, the PLL can double it to 200 MHz for use within the VF1 FPGA.

Table 4 lists the PLL operating conditions.

As shown in Table 4 (see  $t_{LOCK}$  signal), the PLL will acquire a lock on the reference clock within 30 µs, but it may acquire a lock much sooner. A LOCK status signal goes high when a lock is

acquired, so it is possible either to wait 30 µs or to test the LOCK signal to assure that the PLL has acquired a lock.

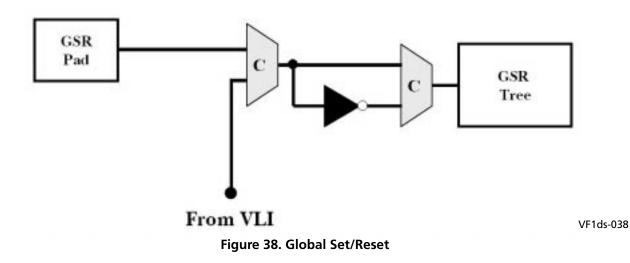

### Global Set/Reset

The VF1 global set/reset signal (Figure 38) may be generated externally and applied to the VF1 FPGA via the Global Set/Reset input pin, or it may be generated within the VF1 FPGA. In addition, the polarity of the set/reset signal may be selected. Both of these conditions are determined at configuration time.

### **Design Methodology**

Complex systems with greater than 10K gates require a sophisticated software-based design methodology. While a schematic-based methodology may be adequate for smaller designs, and sometimes for portions of larger designs, a hardware-description language (HDL) is more appropriate for developing complex designs.

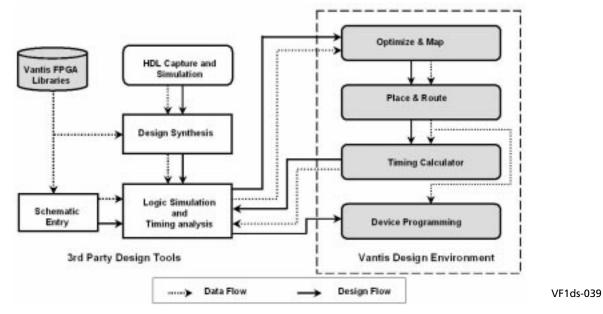

The Vantis design flow consists of two parts (Figure 39):

- **Design development** using third-party front-end development tools. These tools provide design entry, simulation, synthesis, and timing analysis. Designs are transferred from these tools to the Vantis tools in an EDIF file format. Some third-party tools can provide timing constraint files for use by the Vantis tools.

- Design implementation using Vantis physical design tools. These technology-specific tools provide optimization, mapping, timing calculation, and device programming. The output is a JEDEC bit-stream file for programming VF1 FPGAs via the JTAG port or the dedicated programming port.

The Vantis tools include a design manager, graphical user interface, and a logic editor and viewer. The logic editor and viewer enable viewing and moving logic elements down to the VGB level.

Figure 39. Vantis Design Methodology

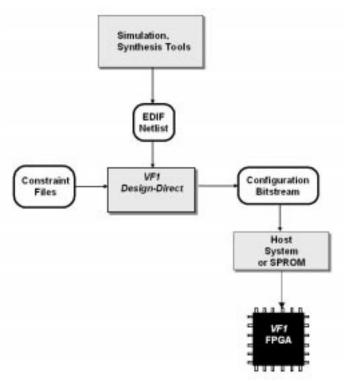

Vantis design environment tools are timing driven, using timing constraint files that are provided by the third-party front-end tools (Figure 40). The Vantis tools generate timing files that can be fed back to the front-end tools for further simulation and timing analysis. The output of the design process is a configuration bitstream that is loaded a VF1 FPGA during configuration.

Figure 40. DesignDirect Inputs and Outputs

Detailed descriptions of the Vantis design methodology and tools are found in the *Design Methodology Users Manual* on the software CD-ROM.

### **JTAG Compatibility**

VF1 family FPGA products are fully compliant with JTAG 1149.1. They implement the following standard JTAG instructions:

- ♦ BYPASS

- ◆ SAMPLE/PRELOAD

- ♦ EXTEST

- ♦ HIGHZ

- ♦ USERCODE

- ♦ IDCODE

- ♦ INTEST

In addition, they implement three non-standard instructions that are used for configuring the VF1 FPGAs through the JTAG port. These instructions are described in the *Configuration modes* section that follows.

### **Configuration Modes**

The VF1 family of devices consists of SRAM-based reprogrammable FPGAs that are configured, or programmed, every time they are powered up. Configuration is the process of loading configuration data into the device from either a companion SPROM or a host system (Figure 41).

The configuration data defines the device's functionality. In addition to power-up configuration, VF1 FPGAs can be reconfigured during operation (in-system programming) if the host system decides to change the device's functionality.

The following is a general description of each configuration mode. Detailed descriptions of all modes and timing are contained in the *VF1 Configuration Guide* Technical Note. The Vantis *VCM SPROM* data sheet describes the companion SPROM.

Host System or SPROM

Figure 41. Configuring a VF1 FPGA

VF1

**FPGA**

- **Master serial mode.** The VF1 automatically loads its configuration data from an external serial PROM.

- ◆ **Slave serial mode.** When two or more VF1 FPGAs in a system are loaded from the same PROM, the first device loaded is loaded in Master serial mode and subsequent devices are loaded in Slave serial mode. In this mode, the master device provides the CCLK signal to slave devices.

- Asynchronous peripheral mode. A host device provides configuration data a byte at a time in parallel to the VF1 FPGA. The VF1 FPGA serializes the data internally for loading.

- **Synchronous peripheral mode.** A host device provides the load clock to the VF1 FPGA and provides byte-wide configuration data on every eighth clock pulse.

- ◆ **JTAG mode.** The VF1 FPGA configuration data is loaded via the JTAG boundary scan circuitry. A host, such as a microprocessor, controls loading and provides configuration data.

Configuration modes are selected by the three mode pins, M0-M2, as shown in Table 5.

| Modes are described briefly below. The Technical Note VF1 Configuration Guide provides |  |

|----------------------------------------------------------------------------------------|--|

| comprehensive guidelines.                                                              |  |

With the exception of the pins directly involved in configuration, all VF1 I/O pins are in three-state mode during configuration. Following configuration the state of the I/O pins is determined by the configuration pattern. Table 5 lists the pins that are used by the various configuration modes.

**Configuration Mode** M2 M1 M0 0 0 Master Serial 0 Slave Serial 1 1 1 Synchronous Peripheral 0 1 1 Asynchronous Peripheral 1 0 1 0 0 JTAG 1

Table 5. Configuration Mode Selection Pins

| Master Serial | Slave Serial | Synchronous<br>Peripheral | Asynchronous<br>Peripheral | JTAG         | User Operation |

|---------------|--------------|---------------------------|----------------------------|--------------|----------------|

| M0 (I)        | M0 (I)       | M0 (I)                    | M0 (I)                     | M0 (I)       | (I/O)/RTRIG    |

| M1 (I)        | M1 (I)       | M1 (I)                    | M1 (I)                     | M1 (1)       | (I/O)/RDO      |

| M2 (I)        | M2 (I)       | M2 (I)                    | M2 (I)                     | M2 (I)       | (I/O)          |

| /PROGRAM (I)  | /PROGRAM (I) | /PROGRAM (I)              | /PROGRAM (I)               | /PROGRAM (I) | /PROGRAM (I)   |

| /INIT (OD)    | /INIT (OD)   | /INIT (OD)                | /INIT (OD)                 | /INIT (OD)   | (1/0)          |

| DONE (OD)     | DONE (OD)    | DONE (OD)                 | DONE (OD)                  | DONE (OD)    | DONE (OD)      |

| HDC (0)       | HLC (0)      | HLC (0)                   | HLC (0)                    |              | (I/0)          |

| /LDC (0)      | /LDC (0)     | /LDC (0)                  | /LDC (0)                   |              | (I/0)          |

| CCLK (O)      | CCLK (I)     | CCLK (I)                  | CCLK (O)                   |              | CCLK (I)       |

| TDI (I)       | TDI (I)      | TDI (I)                   | TDI (I)                    | TDI (I)      | TDI (I)        |

| TCLK (I)      | TCLK (I)     | TCLK (I)                  | TCLK (I)                   | TCLK (I)     | TCLK (I)       |

| TMS (I)       | TMS (I)      | TMS (I)                   | TMS (I)                    | TMS (I)      | TMS (I)        |

| TDO (0)       | TD0 (0)      | TD0 (0)                   | TD0 (0)                    | TD0 (0)      | TD0 (0)        |

| DOUT (0)      | DOUT (0)     | DOUT (0)                  | DOUT (0)                   |              | (I/0)          |

| DINO (I)      | DINO (I)     | DINO (I)                  | DINO (I)                   |              | (I/0)          |

|               |              | DIN1 (I)                  | DIN1 (I)                   |              | (I/0)          |

|               |              | DIN2 (I)                  | DIN2 (I)                   |              | (I/0)          |

|               |              | DIN3 (I)                  | DIN3 (I)                   |              | (I/0)          |

|               |              | DIN4 (I)                  | DIN4 (I)                   |              | (I/0)          |

|               |              | DIN5 (I)                  | DIN5 (I)                   |              | (I/0)          |

|               |              | DIN6 (I)                  | DIN6 (I)                   |              | (1/0)          |

|               |              | DIN7 (I)                  | DIN7 (I)                   |              | (I/0)          |

|               |              | RDY/(/BUSY)(0)            | RDY/(/BUSY)(0)             |              | (I/O)          |

|               |              |                           | /CS0 (I)                   |              | (I/O)          |

|               |              |                           | CS1 (I)                    |              | (1/0)          |

|               |              |                           | /WS (I)                    |              | (1/0)          |

|               |              |                           | /RS (I)                    |              | (1/0)          |

## Table 6. Pins Used in Configuration Modes

#### Notes:

I = Input O = Output OD = Open Drain I/O = Input/Output

Functions of the configuration mode signals are described below. Refer to the individual mode descriptions that follow for timing relationships of these signals.

| M0/RTRIG<br>M1/RDO<br>M2 | Three multiplexed I/O pins that select the configuration mode. During configuration, these pins are input pins and are sampled right after initialization to determine the configuration mode. In normal mode, M0 and M1 can be used as RTRIG and RDO for non-JTAG read-back.                                                                                                                                                                                                                                                                                                                      |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| /PROGRAM                 | A dedicated input pin that initiates configuration. A low level clears the configuration memory and puts the device into a WAIT state. The MODE pins are sampled. A low-to-high transition clears the configuration memory once more and starts the configuration process. If this pin is high during power up, the device will skip the WAIT state after clearing the configuration memory and will go directly into configuration mode.                                                                                                                                                          |

| /INIT                    | A multiplexed I/O pin that indicates initialization status. During device configuration /INIT is an open-drain status pin that can also be used to reset the serial EPROM for a Master device. A low /INIT when /PROGRAM is high indicates initialization is not complete and the device is not ready to receive data for configuration. Tying all the /INIT pins from different devices together ensures the Master device does not start configuration until all slave devices are initialized. For non-JTAG configuration modes, holding the /INIT pin low externally will delay configuration. |

| DONE                     | A dedicated open drain pin that signals when configuration is done. A low output indicates the device is in configuration. A high output indicates configuration is done and all the I/Os will be enabled. For non-JTAG configuration modes, enabling of all the I/Os in different devices can be synchronized by tying all the DONE pins together.                                                                                                                                                                                                                                                |

| HDC                      | A multiplexed I/O status pin that is Low During Configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| /LDC                     | A multiplexed I/O status pin that is Low During Configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CCLK                     | A dedicated I/O pin for configuration clock input or output. In the Master mode, this pin is the clock output from an internal oscillator that drives the serial EPROM and Slave VF1 FPGAs. In the Slave mode and Synchronous Peripheral mode, this pin receives a clock from the Master VF1 FPGA or from a host source.                                                                                                                                                                                                                                                                           |

| TDI, TCLK, TMS, TDO      | <b>TDI, TCLK, and TMS are dedicated input pins; TDO is a dedicated output pin.</b> These pins are used for JTAG boundary scan functions and for programming VF1 FPGAs in JTAG mode.                                                                                                                                                                                                                                                                                                                                                                                                                |

| DOUT                     | A multiplexed I/O pin to pass configuration data from the first VF1 FPGA in a chain to subsequent devices. During configuration, this is an output pin for sending DIN data to daisy-chained devices.                                                                                                                                                                                                                                                                                                                                                                                              |

| DIN0-7                   | Seven multiplexed I/O pins for byte-wide data input. During Synchronous and Asynchronous Peripheral modes, these input pins receive parallel configuration data.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RDY/(/BUSY)              | <b>A multiplexed I/O Ready or Busy status pin.</b> This pin indicates when it is appropriate to write another byte of data into the VF1 FPGA during Peripheral mode configuration. In Asynchronous peripheral mode, the pin is high (RDY) when the VF1 is ready to receive data, and it is low (/BUSY) when the VF1 is processing the last byte it received. In Synchronous peripheral mode, the signal is normally low and goes high for one CCLK period to acknowledge the receipt of a byte of configuration data.                                                                              |

| /CS0, CS1, /WS, /RS      | <b>Multiplexed I/O pins.</b> These four inputs are used in Asynchronous Peripheral mode. The chip is selected when /CS0 is low and CS1 is high. While the chip is selected, a low on /WS loads the data on DIN [0:7] into the internal data register. A low on /RS changes DIN7 into a status pin that outputs the same signal as the RDY/(/BUSY) pin.                                                                                                                                                                                                                                             |

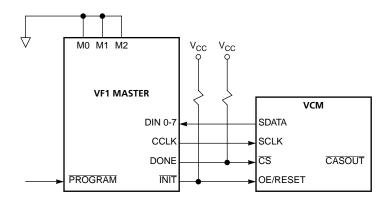

Figure 42. Master Serial Mode

#### Master Serial Mode

In Master serial mode, configuration data is loaded automatically from a serial PROM into the VF1 FPGA (Figure 42). On power-up, or when a PROGRAM command is received, both the /INIT signal and the DONE signal from the VF1 FPGA go low, generating /CE and /RESET signals to the serial EEPROM.

The /INIT signal goes high, enabling the output of the EEPROM. The VF1 FPGA generates the configuration clock, CCLK, and applies it to the EEPROM. CCLK clocks the configuration data out of the EEPROM and clocks it into the VF1 FPGA.

If two or more EEPROMs are required to hold the configuration data, the first EEPROM pulls its /CASOUT signal low when it has loaded its last data bit, enabling the second EEPROM to provide subsequent configuration data. The loading continues until the VF1 FPGA is fully configured at which time DONE goes high, halting the configuration process.

Configuration can also be initiated by the /PROGRAM command.

Both /INIT and DONE are open-collector drivers that require external pull-up resistors.

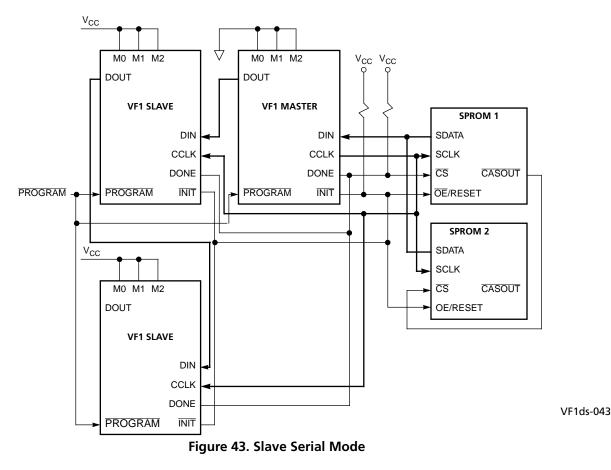

#### Slave Serial Mode

Slave serial mode is normally used when two or more VF1 FPGAs are configured in a daisy chain (Figure 43). In Figure 43 first VF1 FPGA in the chain is configured as a Master and all following devices are slaves. Two SPROMs are shown to illustrate how they may be cascaded to provide adequate storage for multiple configuration bitstreams. The Master VF1 FPGA generates the CCLK configuration clock for all devices in the chain as well as for the SPROMs.

Configuration starts and proceeds the same as in Master serial mode until the Master device is loaded. At that point, the Master transmits subsequent configuration data out on its DOUT pin. That data goes to the DIN pin of the second device. When that device is loaded, it transmits subsequent data on its DOUT pin to the third device. This process continues until all VF1 FPGAs in the chain have been configured.

Figure 43 shows VF1 slave-mode devices following a master-mode device. This is not the only case in which slave-mode configuration is used. It may also be used following VF1 FPGAs configured in Synchronous or Asynchronous peripheral modes, or when a host system configures a VF1 FPGA directly in serial mode.

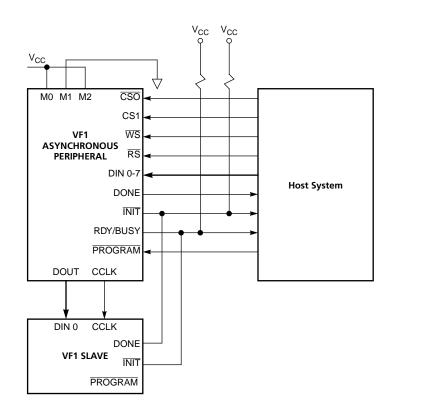

#### Asynchronous Peripheral Mode

Asynchronous Peripheral mode is used to load one or more VF1 FPGAs with byte-wide data from a microprocessor bus (Figure 44). The VF1 FPGA serializes each byte internally, so this mode offers no speed advantage over serial modes. Data transfer is made on the trailing edge of the logical AND of signals /WS and /CS0 being low and /RS and /CS1 being high. Chip select signals can be cycled or maintained at a static level during the configuration process. Each byte of data is written into the VF1 FPGA's DIN [7:0] input pins.

Figure 44. Asynchronous Peripheral Mode

When two or more VF1 FPGAs are daisy-chained for configuration, the lead device loads itself first and then it presents serial configuration data on its DOUT pin. It also generates the CCLK clock signal to control shifting of data into subsequent slave-mode devices in the daisy chain.

The RDY/(/BUSY) status output indicates when another byte can be loaded from the host system. A high indicates that the VF1 FPGA is ready to receive another byte, while a low indicates that it cannot accept a byte. The length of the low signal will vary depending on the shifting status of previously loaded bytes. In addition to appearing on its status pin, the RDY/(/BUSY) signal can be multiplexed on the DIN7 pin by setting chip select pin /WR high and setting pin /RD low.

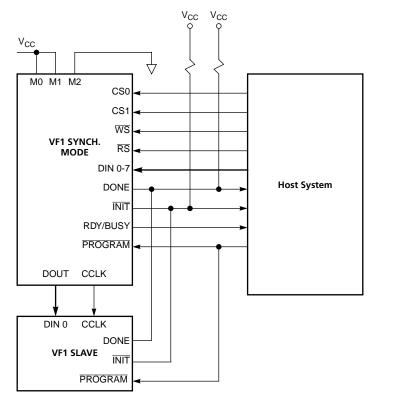

#### Synchronous Peripheral Mode

In Synchronous Peripheral mode, a host system presents byte-wide data over a microprocessor bus and controls shifting of that data by inputting a clock signal to the VF1 FPGA's CCLK pin (Figure 45). The first data byte is clocked into the VF1 FPGA on the rising edge of the second CCLK pulse after /INIT goes high. Bytes are then clocked in on every eighth CCLK pulse. In this mode, the RDY/(/BUSY) signal acknowledges the loading of the byte by going high for one CCLK period on the same clock that loaded the byte. CCLK must remain active after the last byte is loaded to complete the shifting.

Figure 45. Synchronous Peripheral Mode

Synchronous Peripheral mode can be used in daisy-chain configurations. The first VF1 FPGA in the chain loads itself, and then presents serial data on its DOUT pin for loading into the following devices in the chain. CCLK is applied in parallel to all devices from the host system. The data appears on DOUT 1.5 cycles after it is loaded in parallel, which means that DOUT changes on a falling CCLK edge and the next VF1 FPGA loads data on the next rising edge.

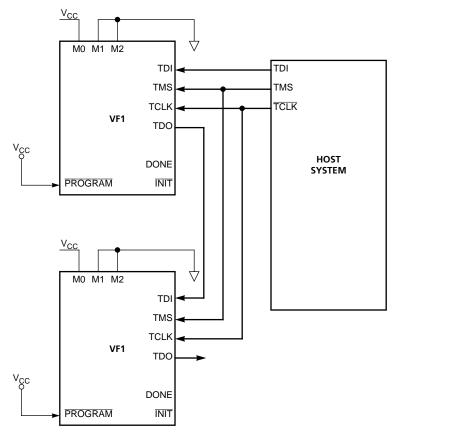

#### JTAG Mode

In JTAG mode, VF1 FPGAs are configured using the JTAG pins TCLK, TMS TDI, and TDO. Three additional JTAG instructions support JTAG configuration mode:

- ◆ **PROG\_MODE.** This instruction places the VF1 FPGA in programming mode.

- ◆ **PROGRAM.** Once the VF1 FPGA is in programming mode, this instruction shifts configuration data into the VF1 FPGA.

- **VERIFY.** After configuration this instruction is used to read back all configuration, VGB and I/O flip-flops, and embedded SRAM bits in the device.

A host system such as a microprocessor controls the configuration of the VF1 FPGA or devices and supplies configuration data. The host also provides the configuration clock.

Figure 46. JTAG Mode

If two or more VF1 FPGAs are to be configured, they are arranged in a daisy chain with all devices selected for JTAG mode configuration (Figure 46). Data is applied to the TDI pin of the first device and the TDO pin of that device is connected to the TDI pin of the next device. The TMS and TCLK signals from the host are applied to all VF1 FPGAs in parallel.

### In-System Programming

A VF1 FPGA is normally loaded with a configuration program when its host system is powered up. As described in the section above, this is often accomplished by loading the program from a separate SPROM. In the case of the Vantis VF1 family, the program may also be loaded through the JTAG port or the dedicated programming port.

The typical FPGA, however, is part of a larger system that includes a microprocessor. The system design can often be simplified by having the microprocessor, rather than a separate serial PROM, configure the VF1 FPGA. The microprocessor can configure the VF1 FPGA using host-driven Slave mode, Asynchronous Peripheral mode, Synchronous Peripheral mode, or JTAG mode. In most applications, JTAG mode will be used.

Using a host microprocessor to load the VF1 FPGA simplifies making design changes or installing ECOs after the device has been installed in a system. The new configuration program can simply be loaded into the microprocessor and then loaded into the VF1 FPGA, eliminating the need to swap PROMs or any other physical part of the system. It also allows dynamic changing of system

functionality by allowing multiple configuration programs to reside in the host system and be loaded into the VF1 FPGAs as needed.

#### **Core Program**

Vantis plans to offer high-value, reusable cores as part of its VF1 family. The first cores in this program are PCI cores that support both the 33MHz and 66MHz standards. Detailed information will be published later.

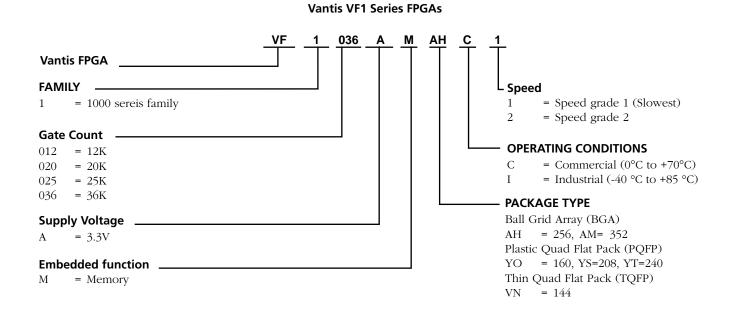

## **ORDERING INFORMATION**

# TECHNICAL SPECIFICATIONS

The following pages contain preliminary technical specifications for the VF1 family.

## **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature                                     |

|---------------------------------------------------------|

| Device Junction Temperature +120°C                      |

| Supply Voltage with Respect to<br>Ground0.5 V to +4.0 V |

| DC Input Voltage                                        |

| Static Discharge Voltage 2000 V                         |

| Latchup Current (0°C to $+70$ °C)200 mA                 |

| Note:                                                   |

Stresses above those listed under Absolute Maximum Ratings may cause permantent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability.

# **OPERATING RANGES**

| Ambient Te  | mperature ( | (T <sub>A</sub> ) Operatio | ng |                                  |

|-------------|-------------|----------------------------|----|----------------------------------|

| in Free Air |             |                            |    | $0^{\circ}$ C to $+70^{\circ}$ C |

Supply Voltage  $(V_{CC})$  with

Respect to Ground. . . . . . . . . . +3.0 V to +3.6 V

#### Note:

Operating ranges define those limits between which the functionality of the device is guaranteed.

### **DC CHARACTERISTICS**

| Parameter         | Parameter Description                                                          | Min                | Max                | Unit |

|-------------------|--------------------------------------------------------------------------------|--------------------|--------------------|------|

| V <sub>IH</sub>   | Input High Voltage                                                             | 2.0                |                    | V    |

| V <sub>IL</sub>   | Input Low Voltage                                                              |                    | 0.8                | V    |

| I <sub>IH1</sub>  | Input High Leakage Current (Vin = Max $V_{CC}$ = 3.6V)                         |                    | 10.0               | μA   |

| I <sub>IL1</sub>  | Input Low Leakage Current (Vin = 0V)                                           |                    | -10.0              | μA   |

| I <sub>IH2</sub>  | Input High Leakage Current with Pull Up (Vin = Max $V_{CC}$ =3.6V)             |                    | 10.0               | μA   |

| I <sub>IL2</sub>  | Input Low Leakage Current with Pull Up (Vin = 0V)                              |                    | -100.0             | μA   |

| I <sub>IH3</sub>  | Input High Leakage Current with Bus Friendly (Vin = Max V <sub>CC</sub> =3.6V) |                    | 10.0               | μA   |

| I <sub>IL3</sub>  | Input Low Leakage Current with Bus Friendly (Vin = 0V)                         |                    | -10.0              | μA   |

| V <sub>OH</sub>   | Output High Voltage @ $I_{OH} = -4.0$ mA (LVTTL) ( $V_{CC} = 3.0$ V)           | 2.4                |                    | V    |

|                   | Output High Voltage @ $I_{OH}$ = -500uA (LVCMOS) ( $V_{CC}$ = 3.0V)            | 0.9V <sub>CC</sub> |                    | V    |

| V <sub>OL</sub>   | Output Low Voltage @ $I_{OL} = 12.0$ mA (LVTTL) ( $V_{CC} = 3.0$ V)            |                    | 0.4                | V    |

|                   | Output Low Voltage @ $I_{OL} = 1.5$ mA (LVCMOS) ( $V_{CC} = 3.0$ V)            |                    | 0.1V <sub>CC</sub> | V    |

| I <sub>OZH1</sub> | Off State Output Leakage with Bus High                                         |                    | 10.0               | μA   |

| I <sub>OZL1</sub> | Off State Output Leakage with Bus Low                                          |                    | -10.0              | μA   |

| I <sub>OZH2</sub> | Off State Output Leakage with Bus High (Pull Up) (Note 1)                      |                    | 10.0               | μA   |

| I <sub>OZL2</sub> | Off State Output Leakage with Bus Low (Pull Up) (Note 1)                       |                    | -100.0             | μA   |

| I <sub>OZH3</sub> | Off State Output Leakage with Bus High (Bus Friendly)                          |                    | 10.0               | μA   |

| I <sub>OZL3</sub> | Off State Output Leakage with Bus Low (Bus Friendly)                           |                    | -10.0              | μA   |

| I <sub>SC</sub>   | Output Short Circuit Current (Vout = $0.5V$ ) ( $V_{CC} = Max V_{CC} = 3.6V$ ) |                    | 300.0              | mA   |

| SI <sub>CC</sub>  | Standby Supply Current (Nominal V <sub>CC</sub> )                              |                    | 6.0                | mA   |

#### Notes:

1. JTAG and dedicated configuration pins have only Pull Up option.

2. Usage of PLL adds 20mA per PLL to the dynamic  $I_{CC}$ .

## **AC CHARACTERISTICS**

The following tables contain preliminary AC timing parameters for the VF1 FPGA family. It is recommended that the timing analysis tools in Vantis' DesignDirect software be used to calculate timing for a design. However, the following tables can be used to develop approximate delays for small circuits. Interconnect delays and interconnect driver delays are not included in these tables. Timing information will be updated as final characterization is done. The latest timing information is published on the Vantis Web site (www.vantis.com).

#### Input AC Parameters

#### **IOB General Input Delays**

| Parameter          | Parameter Description                           | Test Conditions                   | -1  | -2  | Unit |

|--------------------|-------------------------------------------------|-----------------------------------|-----|-----|------|

| t <sub>IN</sub>    | IOB Standard Input Delay                        |                                   | 0.9 | 0.7 | ns   |

| t <sub>INXL</sub>  | IOB Transparent Input Latch Delay without Delay | IOB to Direct Connect to CBB 4LUT | 1.5 | 1.2 | ns   |

| t <sub>INXLD</sub> | IOB Transparent Input Latch Delay with Delay    |                                   | 6.4 | 5.3 | ns   |

| t <sub>ILLEA</sub> | Input Long Line Enable Time                     |                                   | 1.8 | 1.5 | ns   |

| t <sub>ILLER</sub> | Input Long Line Disable Time                    |                                   | 2.4 | 2.0 | ns   |

#### **IOB Input Set/Reset Delays**

| Parameter            | Parameter Description                                            | -1  | -2  | Unit |

|----------------------|------------------------------------------------------------------|-----|-----|------|

| t <sub>ISRGO</sub>   | IOB Input Register (Latch) Global Set/Reset → Interconnect Lines | 1.5 | 1.2 | ns   |

| t <sub>ISRLO</sub>   | IOB Input Register (Latch) Local Set/Reset → Interconnect Lines  | 2.4 | 2.0 | ns   |

| t <sub>ISRGREC</sub> | IOB Input Register (Latch) Global Set/Reset Recovery Time        | 0.5 | 0.4 | ns   |

| t <sub>ISRLREC</sub> | IOB Input Register (Latch) Local Set/Reset Recovery Time         | 1.0 | 0.8 | ns   |

### IOB Input Register (Latch) Global Clock (Gate) Delays

| Parameter            | Parameter Description                                                   | -1  | -2  | Unit |

|----------------------|-------------------------------------------------------------------------|-----|-----|------|

| t <sub>IRLGS</sub>   | IOB Input Register (Latch) Global Clock (Gate) Setup Time Without Delay | 0.0 | 0.0 | ns   |

| t <sub>IRLGH</sub>   | IOB Input Register (Latch) Global Clock (Gate) Hold Time Without Delay  | 0.8 | 0.6 | ns   |

| t <sub>IRLGSD</sub>  | IOB Input Register (Latch) Global Clock (Gate) Setup Time With Delay    | 5.0 | 4.1 | ns   |

| t <sub>IRLGHD</sub>  | IOB Input Register (Latch) Global Clock (Gate) Hold Time With Delay     | 0.0 | 0.0 | ns   |

| t <sub>IRLGCO</sub>  | IOB Input Register (Latch) Global Clock (Gate) → Interconnect Lines     | 1.8 | 1.5 | ns   |

| t <sub>IRLGCES</sub> | IOB Input Register (Latch) Global Clock Enable Setup Time               | 0.9 | 0.7 | ns   |

| t <sub>IRLGCEH</sub> | IOB Input Register (Latch) Global Clock Enable Hold Time                | 0.0 | 0.0 | ns   |

### IOB Input Register (Latch) Local Clock (Gate) Delays

| Parameter           | Parameter Description                                                  | -1  | -2  | Unit |

|---------------------|------------------------------------------------------------------------|-----|-----|------|

| t <sub>IRLLS</sub>  | IOB Input Register (Latch) Local Clock (Gate) Setup Time Without Delay | 0.0 | 0.0 | ns   |

| t <sub>IRLLH</sub>  | IOB Input Register (Latch) Local Clock (Gate) Hold Time Without Delay  | 1.8 | 1.5 | ns   |

| t <sub>IRLLSD</sub> | IOB Input Register (Latch) Local Clock (Gate) Setup Time With Delay    | 4.0 | 3.3 | ns   |

| t <sub>IRLLHD</sub> | IOB Input Register (Latch) Local Clock (Gate) Hold Time With Delay     | 0.0 | 0.0 | ns   |

| t <sub>IRLLCO</sub> | IOB Input Register (Latch) Local Clock (Gate) → Interconnect Lines     | 2.8 | 2.3 | ns   |

## IOB Input Register (Latch) Local Clock (Gate) Delays (Continued)

| Parameter            | Parameter Description                                    | -1  | -2  | Unit |

|----------------------|----------------------------------------------------------|-----|-----|------|

| t <sub>IRLLCES</sub> | IOB Input Register (Latch) Local Clock Enable Setup Time | 0.0 | 0.0 | ns   |

| t <sub>IRLLCEH</sub> | IOB Input Register (Latch) Local Clock Enable Hold Time  | 0.8 | 0.6 | ns   |

### **Output AC Parameters**

#### **IOB** General Output Delays

| Parameter        | Parameter Description              | Test Conditions                | -1  | -2  | Unit |

|------------------|------------------------------------|--------------------------------|-----|-----|------|

| t <sub>OUT</sub> | IOB Standard Output Delay to Pad   |                                | 4.0 | 3.3 | ns   |

| t <sub>OEA</sub> | Output Buffer Enable Time          | CBB 4LUT Direct Connect to IOB | 4.5 | 3.7 | ns   |

| t <sub>OER</sub> | Output Buffer Disable Time         |                                | 6.2 | 5.1 | ns   |

| t <sub>SLW</sub> | Output Buffer Slow Slew Rate Adder |                                | 1.8 | 1.5 | ns   |

### **IOB Output Set/Reset Delays**

| Parameter           | Parameter Description                              | -1  | -2  | Unit |

|---------------------|----------------------------------------------------|-----|-----|------|

| t <sub>ORSRGO</sub> | IOB Output Register Global Set/Reset → Pad         | 4.1 | 3.4 | ns   |

| t <sub>ORSRLO</sub> | IOB Output Register Local Set/Reset → Pad          | 5.1 | 4.2 | ns   |

| t <sub>ORGREC</sub> | IOB Output Register Global Set/Reset Recovery Time | 0.5 | 0.4 | ns   |

| t <sub>ORLREC</sub> | IOB Output Register Local Set/Reset Recovery Time  | 1.0 | 0.8 | ns   |

### **IOB Output Register Global Clock Delays**

| Parameter           | Parameter Description                              | -1  | -2  | Unit |

|---------------------|----------------------------------------------------|-----|-----|------|

| t <sub>ORGS</sub>   | IOB Output Register Global Clock Setup Time        | 0.4 | 0.3 | ns   |

| t <sub>ORGH</sub>   | IOB Output Register Global Clock Hold Time         | 0.4 | 0.3 | ns   |

| t <sub>ORGCO</sub>  | IOB Output Register Global Clock → Pad             | 4.5 | 3.7 | ns   |

| t <sub>ORGCES</sub> | IOB Output Register Global Clock Enable Setup Time | 1.0 | 0.8 | ns   |

| t <sub>ORGCEH</sub> | IOB Output Register Global Clock Enable Hold Time  | 0.0 | 0.0 | ns   |

## **IOB Output Register Local Clock Delays**

| Parameter           | Parameter Description                             | -1  | -2  | Unit |

|---------------------|---------------------------------------------------|-----|-----|------|

| t <sub>ORLS</sub>   | IOB Output Register Local Clock Setup Time        | 0.0 | 0.0 | ns   |

| t <sub>ORLH</sub>   | IOB Output Register Local Clock Hold Time         | 1.4 | 1.1 | ns   |

| t <sub>ORLCO</sub>  | IOB Output Register Local Clock → Pad             | 5.4 | 4.5 | ns   |

| t <sub>ORLCES</sub> | IOB Output Register Local Clock Enable Setup Time | 0.0 | 0.0 | ns   |

| t <sub>ORLCEH</sub> | IOB Output Register Local Clock Enable Hold Time  | 0.8 | 0.6 | ns   |

## **CBB AC Parameters**

## Combinatorial Configurable Building Block (CBB) Delays

| Parameter         | Parameter Description                    | Test Conditions                        | -1  | -2  | Unit |

|-------------------|------------------------------------------|----------------------------------------|-----|-----|------|

| t <sub>3LUT</sub> | CBB Input → LUT → CBB Output (3-LUT)     |                                        | 2.2 | 1.8 | ns   |

| t <sub>4LUT</sub> | CBB Input → LUT → CBB Output (4-LUT)     |                                        | 3.2 | 2.6 | ns   |

| t <sub>5LUT</sub> | CBB Input → LUT → CBB Output (5-LUT)     | IOB to Direct Connect to CBB to Direct | 3.6 | 3.0 | ns   |

| t <sub>6LUT</sub> | CBB Input → LUT → CBB Output (6-LUT)     | Connect to IOB                         | 5.8 | 4.8 | ns   |

| t <sub>WG</sub>   | CBB Input → LUT → CBB Output (Wide Gate) |                                        | 4.1 | 3.4 | ns   |

| t <sub>VFP</sub>  | CBB 3LUT Feedthrough                     | ]                                      | 2.1 | 1.7 | ns   |

### Registered Configurable Building Block (CBB) VGB Global Clock Delays