# INTRODUCTION

When implementing a design into a MACH<sup>®</sup> 4 device, it is often critical to understand how the placement of the design will affect the timing. The MACH 4 device has numerous paths a signal can take, each of which affects the timing in one fashion or another. To more accurately describe the different paths, the MACH 4 timing model has been enhanced<sup>1</sup>. This application note explains the new MACH 4 timing model and high-speed design techniques utilizing this timing model.

## **MACH 4 ARCHITECTURE BASICS**

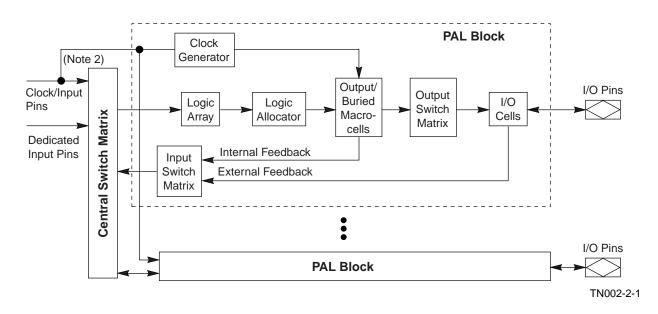

The fundamental architecture of the MACH 4 device consists of multiple optimized PAL<sup>®</sup> blocks (PAL33/34V16) interconnected by a programmable central switch matrix. The central switch matrix allows communication between PAL blocks and routes inputs to the PAL blocks. Routability is further enhanced by an input switch matrix and an output switch matrix. The input switch matrix provides input signals with multiple paths into the central switch matrix; the output switch matrix provides flexibility in assigning macrocells to I/O pins. This concept is illustrated in Figure 1. In a MACH 4 device, all signals incur the same delays, regardless of routing. Performance is design-independent and is guaranteed by Vantis' SpeedLocking<sup>™</sup> feature.

Figure 1. MACH 4 Block Diagram and PAL Block Structure

As indicated in Figure 1, any given macrocell output signal has two different feedback paths into the switch matrix. These two paths are referred to as **internal feedback** and **external feedback**.

<sup>1.</sup> The new timing model is implemented in  $\ensuremath{\mathsf{MACHXL}}^{\ensuremath{\mathbb{R}}}$  software v.6.1 and later.

<sup>2.</sup> M4-192/96 and M4-256/128 do not have clock/input pins connected to central switch matrix.

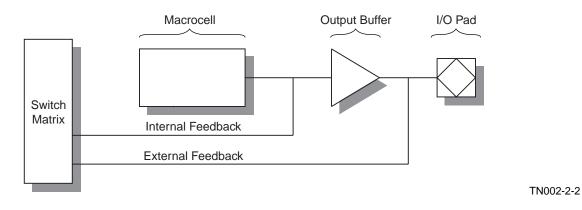

A signal uses internal feedback when it is fed back into the central switch matrix without going through the output switch matrix and the I/O cell. When a signal is fed back into the central switch matrix after having gone through the output switch matrix and the I/O cell, it is using external feedback. For simplicity, the output switch matrix and the I/O cell together are modeled as an output buffer. Both feedback types are shown below in Figure 2.

Figure 2. MACH 4 Signal Feedback Types

# **ENHANCED MACH 4 TIMING MODEL**

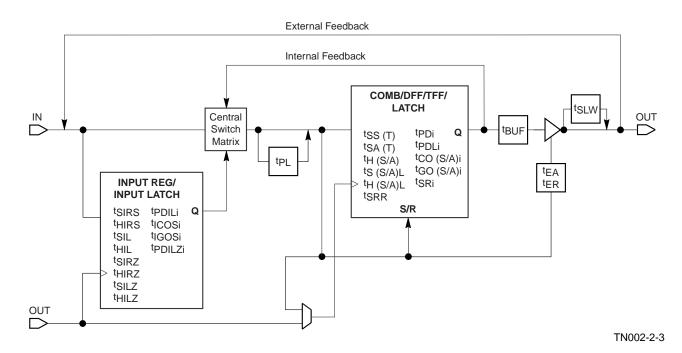

The primary focus of the MACH 4 timing model is to accurately represent the timing in a MACH 4 device while, at the same time, be easy to understand. To accomplish the accuracy, the distinction between internal and external feedback is made. To make the timing model easier to understand and use, the timing is modularized so that each logic element in the signal path will have its own parameters. In particular, the new parameters associated with the input register/latch are a result of this. A diagram representing the MACH 4 timing model is shown in Figure 3.

Figure 3. Enhanced MACH 4 Timing Model

Table 1 lists the MACH 4 timing parameters and their descriptions. To understand the new timing model and parameters, an understanding of the naming convention is necessary. An "i" has been added to all parameters that have delays that are "internal" to the device. Several parameters in both the macrocell register and the input register are affected by the change from external parameters to internal parameters. Delays for parameters that have an "i" appended to them are measured to an internal node rather than to an I/O. Table 2 describes the parameters using this convention.

| Combinatorial Delay:                | t <sub>PDi</sub>    | Internal combinatorial propagation delay           |

|-------------------------------------|---------------------|----------------------------------------------------|

| Register Delays:                    | t <sub>SS</sub>     | Synchronous clock setup time, D-type register      |

|                                     | t <sub>SST</sub>    | Synchronous clock setup time, T-type register      |

|                                     | t <sub>SA</sub>     | Asynchronous clock setup time, D-type register     |

|                                     | t <sub>SAT</sub>    | Asynchronous clock setup time, T-type register     |

|                                     | t <sub>HS</sub>     | Synchronous clock hold time                        |

|                                     | t <sub>HA</sub>     | Asynchronous clock hold time                       |

|                                     | t <sub>COSi</sub>   | Synchronous clock to internal output               |

|                                     | t <sub>COAi</sub>   | Asynchronous clock to internal output              |

| Latch Delays:                       | t <sub>SSL</sub>    | Synchronous Latch setup time                       |

|                                     | t <sub>SAL</sub>    | Asynchronous Latch setup time                      |

|                                     | t <sub>HSL</sub>    | Synchronous Latch hold time                        |

|                                     | t <sub>HAL</sub>    | Asynchronous Latch hold time                       |

|                                     | t <sub>PDLi</sub>   | Transparent latch to internal output               |

|                                     | t <sub>GOSi</sub>   | Synchronous Gate to internal output                |

|                                     | t <sub>GOAi</sub>   | Asynchronous Gate to internal output               |

| Input Register Delays:              | t <sub>SIRS</sub>   | Input register setup time                          |

|                                     | t <sub>HIRS</sub>   | Input register hold time                           |

|                                     | t <sub>ICOSi</sub>  | Input register clock to internal feedback          |

| Input Latch Delays:                 | t <sub>SIL</sub>    | Input latch setup time                             |

|                                     | t <sub>HIL</sub>    | Input latch hold time                              |

|                                     | t <sub>IGOSi</sub>  | Input latch gate to internal feedback              |

|                                     | t <sub>PDILi</sub>  | Transparent input latch to internal feedback       |

| Input Register Delays with ZHT      | t <sub>SIRZ</sub>   | Input register setup time - ZHT                    |

| Option:                             | t <sub>HIRZ</sub>   | Input register hold time - ZHT                     |

| Input Latch Delays with ZHT Option: | t <sub>SILZ</sub>   | Input latch setup time - ZHT                       |

|                                     | t <sub>HILZ</sub>   | Input latch hold time -ZHT                         |

|                                     | t <sub>PDILZi</sub> | Transparent input latch to internal feedback - ZHT |

| Table 1. | MACH 4 | Family Timin | g Parameters |

|----------|--------|--------------|--------------|

|----------|--------|--------------|--------------|

| Output Delays:           | t <sub>BUF</sub>                                                                                 | Output buffer delay                                  |

|--------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------|

|                          | t <sub>SLW</sub>                                                                                 | Slow slew rate delay adder                           |

|                          | t <sub>EA</sub>                                                                                  | Output enable time                                   |

|                          | t <sub>ER</sub>                                                                                  | Output disable time                                  |

| Power Delay:             | t <sub>PL</sub>                                                                                  | Power-down mode delay adder                          |

| Reset and Preset Delays: | Preset Delays:         t <sub>SRi</sub> Asynchronous reset or preset to internal register output |                                                      |

|                          | t <sub>SRR</sub>                                                                                 | Asynchronous reset and preset register recovery time |

#### Table 1. MACH 4 Family Timing Parameters (Continued)

#### Table 2. MACH 4 Internal/External Parameters Description

| External Parameter   | Internal Parameter    | Description                                                    |

|----------------------|-----------------------|----------------------------------------------------------------|

| t <sub>PD</sub>      | t <sub>PDi</sub>      | Input, I/O, or feedback to feedback                            |

| t <sub>COS</sub>     | t <sub>COSi</sub>     | Global clock to feedback                                       |

| t <sub>COA</sub>     | t <sub>COAi</sub>     | Product term clock to feedback                                 |

| t <sub>SR</sub>      | t <sub>SRi</sub>      | Asynchronous Reset or Preset to registered or latched feedback |

| t <sub>GO(S/A)</sub> | t <sub>GO(S/A)i</sub> | Latch gate to feedback                                         |

| t <sub>PDL</sub>     | t <sub>PDLi</sub>     | Input, I/O or feedback to feedback through transparent latch   |

|                      | t <sub>BUF</sub>      | Feedback to Output                                             |

Many of the parameters from the original timing model can be derived from the new, modularized timing parameters. In the enhanced timing model, these original parameters have been eliminated. A list of the eliminated parameters and their derivations is shown in Table 3.

| Eliminated Parameter and its Description |                                                                         | Derivation                                      |

|------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------|

| t <sub>IGOL</sub>                        | Input latch gate to output through transparent output latch             | $t_{IGOSi}$ + $t_{PDLi}$ + $t_{BUF}$            |

| t <sub>IGO</sub>                         | Input latch gate to combinatorial output                                | $t_{IGOSi}$ + $t_{PDi}$ + $t_{BUF}$             |

| t <sub>IGSA</sub>                        | Input latch gate to output latch setup using PT output latch gate       | t <sub>IGOSi</sub> + t <sub>SAL</sub>           |

| t <sub>IGSS</sub>                        | Input latch gate to output latch setup using global output latch gate   | $t_{IGOSi} + t_{SSL}$                           |

| t <sub>ICO</sub>                         | Input register clock to combinatorial output                            | $t_{\rm ICOSi}$ + $t_{\rm PDi}$ + $t_{\rm BUF}$ |

| t <sub>ICS</sub>                         | Input register clock to output register setup, D-type                   | $t_{\rm ICOSi}$ + $t_{\rm SS}$                  |

| t <sub>ICS</sub>                         | Input register clock to output register setup, T-type                   | $t_{\rm ICOSi}$ + $t_{\rm SST}$                 |

| t <sub>SLLA</sub>                        | Setup time from input through transparent input latch to PT output gate | t <sub>PDILi</sub> + t <sub>SAL</sub>           |

| t <sub>SLLS</sub>                        | setup time from input through transparent input latch to output gate    | t <sub>PDILi</sub> + t <sub>SSL</sub>           |

| t <sub>PDLL</sub>                        | Input to output through transparent input and output latches            | $t_{PDILi}$ + $t_{PDLi}$ + $t_{BUF}$            |

| t <sub>PDLI</sub>                        | Input, I/O, or feedback to output through input register                | $t_{PDILZi} + t_{PDi} + t_{BUF}$                |

#### Table 3. Derivation of Eliminated Parameters

|                    | Derivation                                                              |                                        |

|--------------------|-------------------------------------------------------------------------|----------------------------------------|

| t <sub>sllai</sub> | Setup time from input through transparent input latch to PT output gate | $t_{PDILZi} + t_{SAL}$                 |

| t <sub>SLLSI</sub> | Setup time from input through transparent input latch to output gate    | t <sub>PDILZi</sub> + t <sub>SSL</sub> |

| t <sub>PDLLI</sub> | Input to output through transparent input and output latches            | $t_{PDILZi}$ + $t_{PDLi}$ + $t_{BUF}$  |

#### Table 3. Derivation of Eliminated Parameters (Continued)

To maintain consistency with the timing models of other MACH families, some of the parameters have been renamed. In particular, the set/reset parameters,  $t_{RP}$ ,  $t_{PRW}$ , and  $t_{PRR}$ , have been renamed to  $t_{SR}$ ,  $t_{SRW}$ , and  $t_{SRR}$ . Information about all of the timing parameters can be found in the *MACH 4 (A) Family Data Sheet* and in Table 1.

### **Feedback Timing**

In the original MACH 4 timing model, the only feedback path reported in a MACHXL timing report was the external feedback path. Signals using internal feedback were reported as if they had gone through the external feedback path. As a result, the reported delays for those signals would be greater than what would actually be seen in the real device. The new MACH 4 timing model now makes a distinction between those signals using internal feedback and those using external feedback.

To make the distinction between internal and external feedback, several timing parameters have been changed, and the parameter  $t_{BUF}$  has been introduced. All of the changed parameters deal with a signal going to the I/O pad. As an example, the parameter  $t_{PD}$  was originally defined as an input, I/O or feedback going to a combinatorial output. This parameter is now the sum of two parameters:  $t_{PDi}$  and  $t_{BUF}$ . The parameter  $t_{PDi}$  is defined as the time it takes an input, I/O or feedback to go through a combinatorial path to the internal feedback, while  $t_{BUF}$  is the time it takes to go from internal feedback through the output buffer and to the I/O pad.

## Input Register/Latch Timing

Another area in which the MACH 4 timing model has been improved is in the reporting of input register/latch timing. Because there was no mechanism for reporting the internal timing of a MACH 4 device, the timing used for input registers/latches could become complicated. The specifications found in the original MACH 4 data sheets relied on timing that went through both an input register/latch and an output register/latch. As an example, the parameter  $t_{ICOA}$  represented the clock-to-output time for a signal to go through an input register to a combinatorial macrocell, plus the time it took to go through the combinatorial macrocell and to an I/O pad. This method of determining timing was very difficult for the software implementation of the timing model and for designers attempting to determine their timing requirements.

The MACH 4 timing model has greatly simplified the input register timing by reporting all parameters as internal feedback. The same parameter,  $t_{ICO}$ , will no longer exist but rather will be calculated as  $t_{ICOi}$ , the clock-to-internal feedback of the input register, plus a  $t_{PDi}$  and a  $t_{BUF}$ . Because of this modularized timing model, several of the original input register/latch specifications have been eliminated.

## **USING THE MACH 4 TIMING MODEL**

The use of the MACH 4 timing model will be demonstrated using two examples. The first example is a combinatorial logic design and demonstrates the use of internal feedback. The second example is a synchronous sequential logic design and demonstrates how to calculate  $f_{MAX}$ .

## Example 1

This combinatorial logic design is fit into an M4-64/32. A group of input signals are routed to Block A, which is in high power mode. Logic is generated in array "A" and allocated to macrocell A5, which is configured as a combinatorial path. This logic is sent to pad I/O6, which is configured to have a slow slew rate. The signal delay T1 of this path would be:

$$T1 = t_{PDi} + t_{BUF} + t_{SLW}$$

This logic is also fed back to the central switch matrix via the internal feedback path and then routed to Block D, which is in low power mode. A second logic is generated in array "D" using the first logic along with another group of input signals. This second logic is allocated to macrocell D8, which is configured as a combinatorial path. This second logic is sent to pad I/O31, which is in fast slew rate. The longest delay path of this design would be from Block A to I/O31 and the delay  $T_{CRITICAL}$  is:

$$T_{CRITICAL} = t_{PDi} + t_{PL} + t_{PDi} + t_{BUF}$$

The original MACH 4 timing model required an additional  $t_{BUF}$  be added to the delay path because internal feedback was not defined.

### Example 2

This synchronous sequential logic design has a 16-bit up-counter with load enable and reset. It is fit into an M4-96/48 using 16 macrocells configured with T-type registers. Register inputs are defined by the device inputs and flip-flop output, which is internally fed back to the switch matrix. Under these conditions, the period  $t_{CNT}$  is limited by the internal delay from the flip-flop outputs through the internal feedback and logic to the flip-flop inputs.

$$t_{CNT} = t_{COSi} + t_{SST}$$

The  $f_{MAX}$  is designated " $f_{MAXINT}$ ."

#### $f_{MAXINT} = 1/t_{CNT}$

Again, the original MACH 4 timing model required an additional  $t_{BUF}$  be added to the delay path when calculating  $t_{CNT}$  because internal feedback was not defined. Consequently,  $f_{MAX}$  was slower.

The modular approach to the MACH 4 timing model is straightforward, and its use merely requires the addition of internal parameters to arrive at the device timing.

## **HIGH SPEED DESIGN WITH MACH 4 DEVICES**

While the possibility has always existed to control the implementation of high speed designs into a MACH 4 device, the reporting of the timing never made it easy because no distinction was made between internal and external feedback. The improved MACH 4 timing model makes that critical distinction, making it easier to understand how a design is fit into a device.

During the fitting process, the software may use external feedback on timing critical nodes where internal feedback may be required to meet a particular speed. It is also possible that the software feeds a signal into either the block or global switch matrices, which will affect timing. Constraints can be placed on a design to ensure that the critical paths are fit to meet timing. The more a design is constrained, the more difficult it becomes to fit the design. Some methods that can be used to constrain a design are briefly covered here and are more fully covered in the *MACHXL*<sup>®</sup> *User's Manual* and the Application Note entitled, *PI File Reference Guide*. MACHXL software uses the PI File to control the fitting process and constrain the design. It contains pinout and placement information along with directives that determine the fitting algorithms used.

## **Controlling Feedback**

To control the signal feedback path, the PI File directives, FORCE\_INTERNAL\_FEEDBACK, can be utilized. This PI property forces a signal to use an internal feedback path rather than giving it a choice of using an external or internal feedback path. By forcing a signal to use internal feedback, the delay caused by the output buffer is saved.

## CONCLUSION

The MACH 4 timing model provides for a more accurate, easier to understand timing calculation. It defines both internal and external feedback paths and simplifies the timing used for internal registers/latches. By using and understanding the timing model in the proper way, it becomes easier to control the critical path timing in a high speed design using the properties in the PI File.