# Packages

# INTRODUCTION

Vantis provides its programmable logic devices (PLDs) in a wide range of packages. These packages provide benefits such as high power dissipation capability, small footprint, and high I/O. This section provides details about the packages that Vantis supplies.

## **EXTERNAL LEAD DESIGNS**

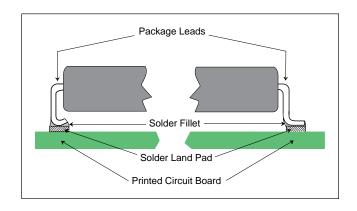

The shape of the leads on leaded surface-mount packages, which includes all but the BGA package, are formed in either a gull-wing or J-bend shape. Both lead shapes offer the advantage of being flexible, which allows them to absorb thermal expansion mismatches between the IC package and the board.

| Plastic Package Design       | Leadcounts    | Lead Design/Direction |

|------------------------------|---------------|-----------------------|

| Leaded Chip Carrier (PLCC)   | 20-84 leads   | J-Bend/4 sides        |

| Quad Flat Pack (PQFP)        | 100-240 leads | Gull-wing/4 sides     |

| Thin Quad Flat Pack(TQFP)    | 44—176 leads  | Gull-wing/4 sides     |

| Ball Grid Array (BGA)        | 256—352 balls | Solder Balls/Array    |

| Plastic Dual-In-Line (PDIP)  | 20-28 leads   | Through-hole          |

| Small Outline Plastic (SOIC) | 20-24 leads   | Gull-wings/2 sides    |

◆ Gull-Wing Lead Design

Gull-wing leads are similar to dual-in-line, through-hole leads except that the leads are bent at the tips to rest flat on the board surface. This provides a built-in standoff between the package and the board, enabling thorough board cleaning and easy-to-inspect solder joints.

♦ J-Bend Lead Design

Like the gull-wing design, J-bend leaded packages can be mounted directly to the board, thus offering a built-in standoff and all the advantages inherent in this. A strong, inspectable bond is easily attainable provided the solder lands include extensions out from under the package. The J-bend design also allows easy socketing, which facilitates device testing and programming.

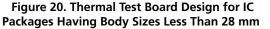

21552B-001

Figure 1. J-Bend (On the Left) and Gull-Wing Lead Formations (On the Right) Allow Components to be Mounted onto the Surface of the Circuit Board

# PACKAGE MATERIALS

The materials used in Vantis' plastic packages and flammability data are provided in this section.

| Package                                    | Leadcount         | Ul Rating &<br>Oxygen Index <sup>1</sup> | Resin Weight<br>Per Unit (grams) | Compound Weight Per<br>Unit (grams) |

|--------------------------------------------|-------------------|------------------------------------------|----------------------------------|-------------------------------------|

|                                            | 20 (PL)           |                                          | 0.1                              | 0.6                                 |

| Plastic Leaded<br>Chip Carriers            | 28 (PL)           |                                          | 0.2                              | 1.0                                 |

|                                            | 44 (PL)           | 94 V-0 & ≥28%                            | 0.5                              | 2.0                                 |

| (PL, PLH)                                  | 68 (PL)           | 94 v-0 & ≥28%                            | 1.1                              | 4.4                                 |

| (                                          | 84 (PL)           |                                          | 1.8                              | 7.3                                 |

|                                            | 84 (PLH)          |                                          | 1.4                              | 5.8                                 |

|                                            | 100 (PQR)         |                                          | 0.3                              | 1.4                                 |

| Metric Plastic Quad<br>Flat Pack (PQR)     | 144 (PQR)         |                                          | 1.2                              | 4.8                                 |

|                                            | 160 (PQR)         |                                          | 1.1                              | 4.8                                 |

|                                            | 208 (PQR)         | 94 V-0 & ≥28%                            | 1.2                              | 4.8                                 |

| Thermally Enhanced                         | 160 (PQE)         |                                          | 0.9                              | 3.8                                 |

| Metric Plastic Quad<br>Flat Pack           | 208 (PRH)         |                                          | 1.1                              | 4.6                                 |

| (heat spreader (PRH),                      | 208 (PQE)         |                                          | 0.9                              | 3.8                                 |

| heat sink (PQE))                           | 240 (PQE)         |                                          | 0.9                              | 3.97                                |

|                                            | 44 (PQT)          |                                          | <0.1                             | 0.1                                 |

| Thin Plastic Quad Flat Pack                | 48 (PQL)          |                                          | <0.1                             | 0.1                                 |

| (1.0 mm thick (PQT);<br>1.4 mm thick (PQL) | 100 (PQL)         | $94 \text{ V} - 0 \& \ge 28\%$           | <0.1                             | 0.3                                 |

| TQFP                                       | 144 (PQL)         |                                          | <0.1                             | 0.7                                 |

|                                            | 176 (PQL)         |                                          | <0.1                             | 0.7                                 |

|                                            | 256 (BGD)         | substrate:                               | 0.07 (Note 2)                    | 0.26 (Note 3)                       |

| Plastic Ball Grid Array                    | 352 (BGD)         | UL 94V-O<br>glob top: UL 94HB            | 0.12 (Note 2)                    | 0.45 (Note 3)                       |

|                                            | 20                |                                          | 0.3                              | 1.2                                 |

| Plastic Dual-In-Line                       | 24 (PD3) (Note 3) |                                          | 0.3                              | 1.5                                 |

|                                            | 28 (PD3) (Note 3) | $94 \text{ V} - 0 \& \ge 28\%$           | 0.4                              | 1.6                                 |

| Small Outline Plastic                      | 20                |                                          | <0.1                             | 0.2                                 |

|                                            | 24                |                                          | <0.1                             | 0.2                                 |

| Table 1. Flammability Ratings per Package Type and Size | Table 1 | . Flammability | Ratings p | er Package | Type and Size |

|---------------------------------------------------------|---------|----------------|-----------|------------|---------------|

|---------------------------------------------------------|---------|----------------|-----------|------------|---------------|

1. The mold compound is tested according to the ASTM Standard D2863-77,:Standard Method for Measuring Oxygen Concentration to Support Candlel-Like Combustion of Plastics (Oxygen Index)." The flammability rating is determined by the Underwriters Laboratories (UL) Standard 94, "Test for Flammability of Plastic Materials for Parts in Devices and Applications.

2. Refers to the weight of the glob-top encapsulation.

3. PD3 (300-mil) designates a PDIP design for which the package mil size is not what is standard for that lead count.

| Package Type &<br>Leadcount | Pa                                 | ckage Part                  | Material                         | Percentage of Composition <sup>2</sup>      |

|-----------------------------|------------------------------------|-----------------------------|----------------------------------|---------------------------------------------|

| All Plastic Surface         | Mount Packages (exclud             | ing Ball Grid Array Package | es)                              |                                             |

|                             |                                    |                             | epoxy novolac                    | 13.0%-30.5%                                 |

|                             |                                    |                             | silica filler                    | 69.5%—87.0%                                 |

|                             |                                    |                             | chlorine                         | 7—80 ppm                                    |

|                             | Package body                       |                             | bromine                          | 0.0%—0.9% weight                            |

|                             |                                    |                             | antimony trioxide                | 0%—1.8%                                     |

|                             |                                    |                             | sodium                           | 5—40 ppm                                    |

|                             |                                    |                             | potassium                        | 0—10 ppm                                    |

|                             | Die attach adhesive                |                             | ероху                            | 20%-30%                                     |

|                             |                                    |                             | silver filler                    | 80%—70%                                     |

|                             |                                    |                             | sodium                           | 5—50 ppm                                    |

|                             |                                    |                             | chlorine                         | 5—50 ppm                                    |

| All Package Types           |                                    |                             | potassium                        | 5—20 ppm                                    |

| and Lead Counts             | Die-to-package<br>interconnections | bond wire                   | gold                             | 99.99%                                      |

|                             |                                    |                             | copper                           | 96.2%—99.9%                                 |

|                             |                                    |                             | nickel                           | 3.0%                                        |

|                             |                                    |                             | iron                             | 0.005%—2.35%                                |

|                             |                                    |                             | silicon                          | 0.65%                                       |

|                             | Leadframe                          | copper                      | magnesium                        | 0.15%                                       |

|                             |                                    |                             | zinc                             | 0.12%                                       |

|                             |                                    |                             | zirconium                        | 0.0%-0.15%                                  |

|                             |                                    |                             | phosphorous, aluminum, manganese | traces, depending on the leadframe supplier |

|                             | Lead plating                       |                             | tin/lead                         | 85%, +5%, -0%/15%, -5%                      |

# Table 2. Package Materials <sup>1</sup>

#### Notes:

1. Excluding the die

2. Ranges are provided in some cases, to cover the differences in materials per supplier. Contact your local Vantis sales representative for more product specific information.

| Package Type<br>& Leadcount | Packa                                | ge Part      | Material          | Percentage of Composition <sup>2</sup> |

|-----------------------------|--------------------------------------|--------------|-------------------|----------------------------------------|

| Ball Grid Array Package     | 25                                   |              |                   |                                        |

|                             |                                      | substrate    | organic resin     | 40%-60%                                |

|                             |                                      | Substrate    | glass fibers      | 40%60%                                 |

|                             | Package body                         | circuitry    | copper (Note 3)   | 99%—100%                               |

|                             | Fackage bouy                         |              | resin             | 40%-60%                                |

|                             |                                      | solder mask  | inorganic fillers | 35%—55%                                |

|                             |                                      |              | additives         | 1%—10%                                 |

|                             | Die attach adhesive                  |              | ероху             | 20%—30%                                |

| All Plastic                 | Die attach adhesive                  |              | silver filler     | 70%—80%                                |

| Package Versions            | Die-to-package<br>interconnections   | bond wire    | gold              | 99.99%                                 |

|                             | Package-to-board<br>outerconnections | solder balls | tin, lead         | 63%, 37% (eutectic)                    |

|                             | Clob top operation                   |              | epoxy resin       | 20%—40%                                |

|                             | Glob top encapsulation               |              | silica filler     | 60%—80%                                |

|                             | Heat spreader                        |              | copper            | 96%—99%                                |

|                             | fieat spreauer                       |              | iron              | 0%—2.4%                                |

### Table 3. Package Materials <sup>1</sup>

#### Notes:

- 1. Excluding the die

- 2. Ranges are provided in some cases to cover the differences in materials per supplier. Contact your local Vantis sales representative for more product specific information.

- 3. The internal leads are electroplated with nickel, copper, and gold. These persentages vary depending on the specific package. Contact your local Vantis sales representative should you need product specific information.

#### Table 4. Materials Not Detectable in Vantis' Plastic Components

| 4-Aminodiphenyl and its salts      | Hydrazine                           | Polyhalogenated Dibenzofurans/Dioxins |

|------------------------------------|-------------------------------------|---------------------------------------|

| Ammonium Salts                     | 2-Naphthylamine and its salts       | Polychlorinated Naphthalenes          |

| Arsenic                            | Nickel Tetracarbonyl                | Polycyclic Compounds                  |

| Asbestos                           | N, N-Dimethylformamide              | Selenium                              |

| Benzene                            | N, N-Dimethylacetamide              | Tetrabromobenzylimidazole             |

| Brominated Diphenyl Oxides         | N-Nitrosoamines                     | Tetrabromobisphenol A                 |

| Cadmium and Cadmium Compounds      | Mercury and Mercury Compounds       | Tetrabromoethylene                    |

| Decabromodiphenyl Ether            | Ozone Depleting Compounds           | Toluene                               |

| 4, 4-Diaminophenyl Methane         | Octabromodiphenyl Ether             | Triethylamine                         |

| Epichlorhydrine                    | Oils and Greases                    | Tris (2, 3-Dibromopropyl) Phosphate   |

| Ethylene Glycol ethers             | Palladium                           | Tris (aziridinyl) Phosphin Oxide      |

| Fluorine                           | Phthalate                           | Vinyl Chloride Monomer                |

| Formaldehyde                       | Halogenated Aliphatic Hydrocarbons  | Xylene                                |

| Halogenated Aliphatic Hydrocarbons | Polyhalogenated Bi/Triphenyl Ethers |                                       |

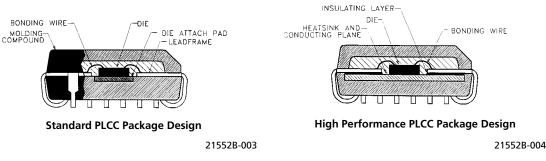

### **Thermally Enhanced Plastic Package Designs**

In addition to the standard package designs, Vantis' PLCC and PQFP package families include highperformance variations for devices having greater power and faster speed. We are also evaluating high-performance designs in our TQFP and BGA package families.

The high-performance package designs include two variations: one in which a heat spreader is embedded in the package, and the other entails assembling into the package a heat sink which is visible on the topside of the package.

### **Heat Spreader Design**

This design includes a heat sink that is attached to a padless leadframe using a B-stage adhesive. The heat sink, referred to in this design as a heat spreader because it serves as the die attach pad, fills the narrow gap between where the die-attach pad would normally end and the leads begin. This provides a more efficient means of heat transferal since heat from the device no longer has to pass over a gap to escape to the leadframe. Also thermally advantageous, a thin strip of insulating tape in the B-stage epoxy allows the heat sink to be quite close to the leadframe without actually touching it (since to do so would cause an electrical short.

The heat sink also serves as a fixed potential plane in that its voltage level will not vary much from the voltage on the back of the die. Because the heat sink is underneath the die, separated from it by only the epoxy and the 0.003-inch thick insulating tape, it is closer to all the input/output, power, and ground leads than in a standard PLCC package (in which the closest ground is on the circuit board,  $\approx 0.090$  inch below the leads). This significantly lowers lead inductance which keeps the noise level down.

Comparative analysis of package performance using the same device in a standard versus a highperformance PLCC package have shown the latter to outperform the standard package in the areas of lead inductance, thermal impedance ( $\theta_{\mu}$ ), speed, and yields.

Figure 2. A High-Performance PLCC Package Includes a Heat Spreader Within the Package—a Feature not Present in a Standard PLCC Package Design

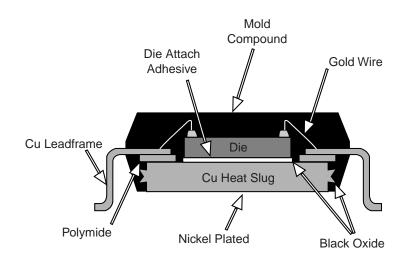

### **Exposed Heat Sink Design**

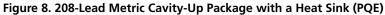

For very high-power devices, it is necessary that the heat sink conduct the heat all the way to the surface of the IC package. For such devices, a much thicker heat sink is used to span the entire encapsulated portion of the leadframe. This design can be achieved in either a cavity-down version (see Figure 3), in which the heat sink is visible on the top of the package, or a cavity-up version,

in which the heat sink is exposed on the package bottom (Figure 3). This style of heat sink is sometimes referred to as a heat slug, since the metal comes in contact with the chip itself (as opposed to a heat sink that is attached to the exterior of the package body).

### **Thermal Performance Improvement**

The improvement in thermal performance for, say, a 28-mm body PQFP, is approximately 30 percent for the heat spreader design and 60 percent for the exposed heat sink version.

Contact your Vantis sales representative should you need additional information about Vantis' highperformance plastic package designs.

21552B-005

Figure 3. A Heat Sink Assembled in a Thermally Enhanced PQFP (Known as PQE Package) is Visible on the Bottom Side of the Package

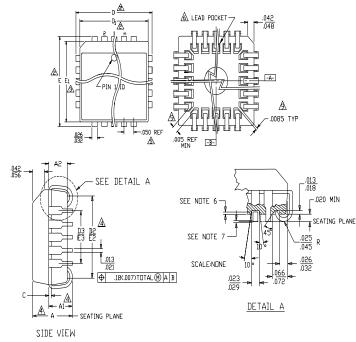

### **Plastic Leaded Chip Carrier (PLCC) Packages**

The PLCC package design is an attractive alternative to higher leadcount plastic DIPs because it can accommodate larger die sizes and offer the advantages of SMT. Above 84 leads, the PLCC configuration and lead-pitch are impractical given the availability of lower profile, high leadcount packages, such as finer pitch PQFPs.

The PLCC package construction consists of a device attached to the die pad of a leadframe, the circuitry of which is wire bonded to the lead fingers. A plastic epoxy material is injection-molded to encapsulate the device/leadframe configuration. The quad-directional leads are trimmed and formed to a J-bend formation.

The 50-mil lead-pitch of a PLCC package is half the conventional lead spacing of a DIP. This, coupled with the PLCC leads being located on all four sides of the package, greatly reduce the footprint. A comparison of package dimensions is shown in Table 5.

| Leadcount | Package Body Area (L X W)<br>Inches SQ. | Lead Pitch<br>Inches | Package Weight (Grams) |

|-----------|-----------------------------------------|----------------------|------------------------|

| 20        | 0.125                                   |                      | 0.65                   |

| 28        | 0.205                                   |                      | 1.07                   |

| 44        | 0.426                                   | 0.05                 | 2.22                   |

| 68        | 0.908                                   |                      | 4.62                   |

| 84        | 1.33                                    |                      | 7.45                   |

| Table 5. PLCC (PL) | Package Size | Overview |

|--------------------|--------------|----------|

|--------------------|--------------|----------|

#### Note:

1. PL is Vantis' internal abbreviation for a PLCC package.

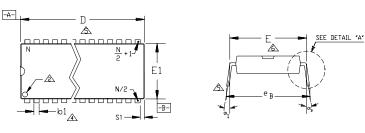

Figure 4. Square Packages (PL)

21552B-006

|                 |        |         | Vanti  | s Package Ty | /pe & Leadco | ount (JEDEC | Drawing Nu | mber)   |         |         |

|-----------------|--------|---------|--------|--------------|--------------|-------------|------------|---------|---------|---------|

|                 | PL     | 020     | PL     | 028          | PL           | 044         | PL         | 068     | PL 084, | PLH084  |

|                 | (MS-01 | 8(A)AA) | (MS-01 | 8(A)AB)      | (MS-01       | 8(A)AC)     | (MO-04     | 7(B)AE) | (MO-04  | 7(B)AF) |

| Dimension Codes | Min    | Max     | Min    | Max          | Min          | Max         | Min        | Max     | Min     | Max     |

| Α               | 0.165  | 0.180   | 0.165  | 0.180        | 0.165        | 0.180       | 0.165      | 0.180   | 0.165   | 0.180   |

| A1              | 0.090  | 0.120   | 0.090  | 0.120        | 0.090        | 0.120       | 0.090      | 0.130   | 0.090   | 0.130   |

| A2              | 0.062  | 0.083   | 0.062  | 0.083        | 0.062        | 0.083       | 0.062      | 0.083   | 0.062   | 0.083   |

| D, E            | 0.385  | 0.395   | 0.485  | 0.495        | 0.685        | 0.695       | 0.985      | 0.995   | 1.185   | 1.195   |

| D1, E1          | 0.350  | 0.356   | 0.450  | 0.456        | 0.650        | 0.656       | 0.950      | 0.956   | 1.150   | 1.156   |

| D2, E2          | 0.290  | 0.330   | 0.390  | 0.430        | 0.590        | 0.630       | 0.890      | 0.930   | 1.090   | 1.130   |

| D3, E3          | 0.20   | ) REF   | 0.30   | 0 REF        | 0.50         | 0 REF       | 0.80       | 0 REF   | 1.00    | 0 REF   |

| С               | 0.009  | 0.015   | 0.009  | 0.015        | 0.009        | 0.015       | 0.007      | 0.013   | 0.007   | 0.013   |

- 1. All dimensions are in inches.

- 2. Dimensions "D" and "E" are measured from the outermost point.

- 3. Dimensions "D1" and "E1" do not include corner mold flash. Allowable corner mold flash is 0.010 inch.

- 4. Dimensions "A, A1, D2, and E2" are measured from the points of contact to the base plane.

- 5. Lead spacing as measured from the center-line to the center-line shall be within  $\pm 0.005$  inch.

- 6. J-bend lead tips should be located inside the "pockets."

- 7. Lead coplanarity shall be within 0.004 inch as measured from the seating plane.

- 8. Lead tweeze shall be within 0.0045 inch on each side as measured from a vertical flat plane.

- 9. The lead pocket may be rectangular (as shown) or oval. If the corner lead pockets are connected, then 0.005-inch minimum lead spacing is required.

- 10. PL is Vantis' internal abbreviation for a PLCC. PLH refers to one that has been thermally enhanced with an embedded heat spreader.

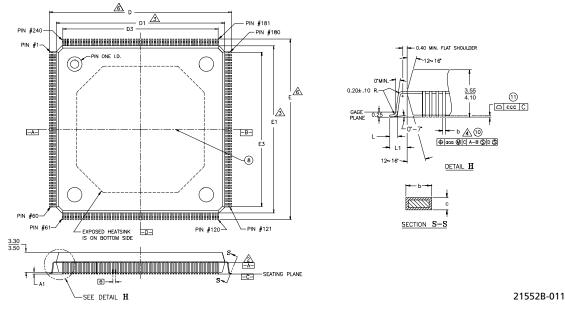

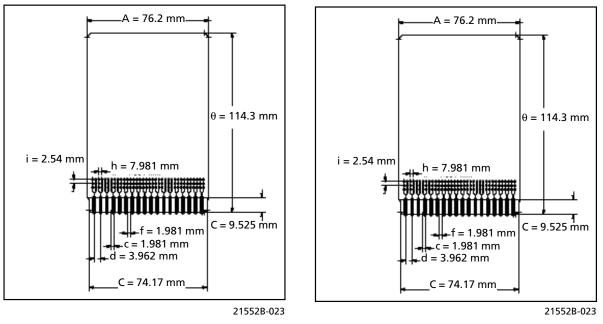

### Plastic Quad Flat Pack (PQFP) Packages

PQFP packages were developed primarily for high-leadcount applications. The finer lead-pitch of a PQFP enables this design to accommodate higher leadcount devices than desirable in PDIP, PLCC, and SOIC packages. As the benefits of the PQFP package configuration were realized within the industry, the design was extended to lower leadcounts.

The PQFP package construction consists of a device attached to the die pad of a leadframe, the circuitry of which is wire bonded to the lead fingers. A plastic epoxy material is injection-molded to encapsulate the device/leadframe configuration. The quad-directional leads are trimmed and formed to a gull-wing formation.

Vantis' PQFP package family includes a wide range of leadcount variations (from 100 to 240). For the most part, the package designs comply with JEDEC and/or EIAJ package versions. Some of the packages are thermally enhanced with either a heat spreader, embedded in the package body; or an exposed heat sink.

| Leadcount      | Package Body Area (L X W)<br>Inches SQ. (mm SQ.) | Lead Pitch<br>Inches (mm) | Package Weight (Grams) |

|----------------|--------------------------------------------------|---------------------------|------------------------|

| 100 (PQR)      | 0.434 (280.0)                                    | 0.030 (0.80)              | 1.66                   |

| 144 (PQR)      | 1.215 (784.0)                                    |                           | 5.21, 5.34             |

| 160 (PQR)      | 1.215 (784.0)                                    | 0.025 (0.65)              | 5.30                   |

| 160 (PQE)      | 1.215 (784.0)                                    |                           | 5.37                   |

| 208 (PQR, PRH) | 1.215 (784.0)                                    |                           | 9.53, 9.68             |

| 208 (PQE)      | 1.213 (/84.0)                                    | 0.020 (0.50)              | 10.87                  |

| 240 (PQE)      | 1.588 (1024.0)                                   |                           | 15.07                  |

### Table 6. PQFP (PQR)<sup>1</sup> Package Size Overview

#### Note:

1. PQR (cavity up) is Vantis' internal abbreviations for metric PQFPs. Thermally ebanced versions are denoted as PRH (cavity up with beat spreaders) and PQE (cavity up with exposed heat sink).

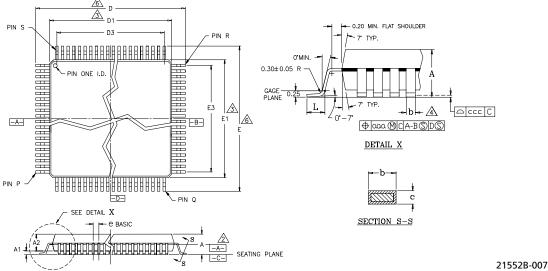

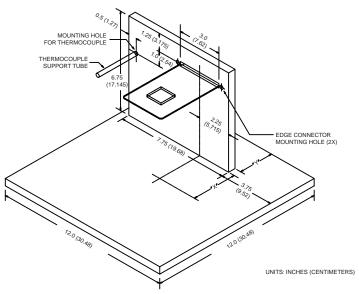

Figure 5. Rectangular Metric, Cavity-Up Packages (PQR)

|                 | Vantis Package Type & Leadcount |          |  |  |

|-----------------|---------------------------------|----------|--|--|

|                 | PQR, PRH100                     |          |  |  |

| -               | (MO-108                         | (B)CC-1) |  |  |

| Dimension Codes | Min                             | Мах      |  |  |

| Α               | _                               | 3.35     |  |  |

| A1              | 0.25                            | —        |  |  |

| A2              | 2.70                            | 2.90     |  |  |

| b (Note 4)      | 0.22                            | 0.38     |  |  |

| с               | 0.15                            | 0.23     |  |  |

| D (Note 5)      | 17.00                           | 17.40    |  |  |

| D1 (Note 3)     | 13.90                           | 14.10    |  |  |

| D3              | 12.35 REF                       |          |  |  |

| e (Note 7)      | 0.651                           | BASIC    |  |  |

| E (Note 5)      | 23.00                           | 23.40    |  |  |

| E1 (Note 3)     | 19.90                           | 20.10    |  |  |

| E3              | 18.85                           | 5 REF    |  |  |

| aaa             | 0.13                            | NOM      |  |  |

| ссс             | 0.10 NOM                        |          |  |  |

| L               | 0.73                            | 1.03     |  |  |

| Lead P          | 30                              |          |  |  |

| Lead Q          | 50                              |          |  |  |

| Lead R          | 80                              |          |  |  |

| Lead S          | 10                              | 00       |  |  |

- 1. All dimensions are in millimeters, and the dimensions and tolerances conform to ANSI Y14.5M-1982.

- 2. Datum plane A— is located at the mold parting line and is coincident with the bottom of the lead where the lead exits the plastic body.

- 3. Dimensions "D1 and E1" do not include mold protrusion. Allowable mold protrusion is 0.25 mm per side. (Also see Note 5.)

- 4. Dimension "b" does not include dambar protrusion.

- 5. Dimensions "D1 and E1" do include mold mismatch and are determined at datum plane —A—.

- 6. Dimensions "D and E" are measured from both the innermost and outermost points.

- Deviation from the lead-tip true position shall be within ±0.076 mm for packages having lead pitch >0.5 mm, and within ±0.04 mm when the pitch is ≤0.5 mm.

- 8. Lead coplanarity shall be within 0.10 mm for devices having lead pitch of 0.65–0.80 mm, and 0.076 mm when the lead pitch is 0.50 mm.

- 9. The balf span (center of the package to the lead tip) shall be within ±0.0085.

- 10. PQR is Vantis' internal abbreviation for a metric PQFP.

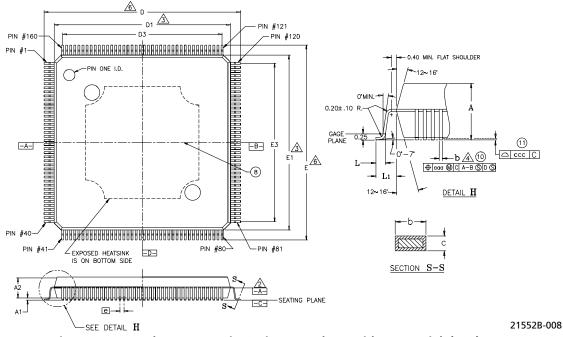

Figure 6. 160-Lead Square Metric, Cavity-Up Package with a Heat Sink (PQE)

|           | Vantis Package Type & Leadcount<br>(JEDEC Drawing Number) |       |  |

|-----------|-----------------------------------------------------------|-------|--|

| Dimension | PQE<br>(MS-022(                                           |       |  |

| Codes     | Min                                                       | Max   |  |

| A         | _                                                         | 4.00  |  |

| A1        | 0.25                                                      | 0.45  |  |

| A2        | 3.25                                                      | 3.45  |  |

| b         | 0.22                                                      | 0.38  |  |

| с         | 0.11                                                      | 0.17  |  |

| D, E      | 30.80                                                     | 31.60 |  |

| D1, E1    | 27.90                                                     | 28.10 |  |

| D3, E3    | 25.35                                                     | REF   |  |

| e         | 0.65 B                                                    | BASIC |  |

| L         | 0.73                                                      | 1.03  |  |

| L1        | 1.60 NOM                                                  |       |  |

| aaa       | 0.08 NOM                                                  |       |  |

| ccc       | 0.08 NOM                                                  |       |  |

- 1. All dimensions are in millimeters, and the dimensions and tolerances conform to ANSI Y14.5M-1982.

- 2. Datum plane -A- is located at the mold parting line and is coincident with the bottom of the lead where the lead exits the plastic body.

- 3. Dimensions "E1 and D1" do not include mold protrusion. Allowable mold protrusion is 0.25 mm per side. (See also Note 5.)

- 4. Dimension "b" does not include dambar protrusion.

- 5. Dimensions "E1 and D1" do include mold mismatch and are determined at datum plane -A-.

- 6. Dimensions "D and E" are measured from both the outermost points.

- 7. The pin-one ID may be inside the top ejector mark or separate.

- The heatsink center line is aligned to the package body's center line at a tolerance of ±0.30 mm.

- 9. The half span (center of the package to the lead tip) shall be within  $15.30 \pm 0.165$  mm.

- 10. No lead distortion (bent leads, etc.) shall cause deviation from the lead's true position by greater than  $\pm 0.04$  mm at the maximum of the "b" dimension.

- 11. Lead coplanarity with respect to the seating plan shall not exceed 0.10 mm.

- 12. PQE is Vantis' internal abbreviation for a cavity-up, metric PQFP which has been thermally enhanced with an exposed heat sink.

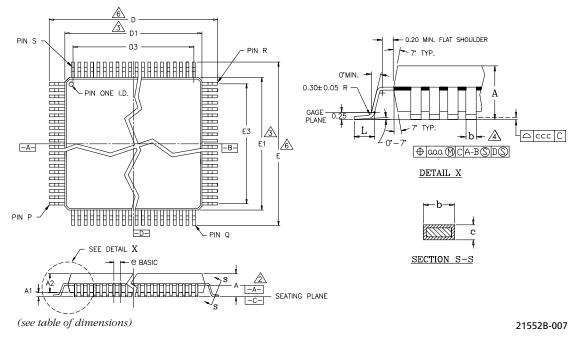

Figure 7. Plastic Quad Flat Pack (PQFP) Packages

|                    | Vantis Package Type & Leadcount<br>(JEDEC Drawing Number) |            |            |          |            |           |

|--------------------|-----------------------------------------------------------|------------|------------|----------|------------|-----------|

|                    | PQR                                                       | 144        | PQR        | 160      | PQR, P     | RH 208    |

| Dimension          | (MO-108                                                   | (B)DC-1)   | (MO-108    | (B)DD-1) | (MO-143    | B(B)FA-1) |

| Codes              | Min                                                       | Мах        | Min        | Max      | Min        | Max       |

| A                  | —                                                         | 3.95       | _          | 3.95     | —          | 3.95      |

| A1                 | 0.25                                                      | —          | 0.25       | _        | 0.25       | —         |

| A2                 | 3.20                                                      | 3.60       | 3.20       | 3.60     | 3.20       | 3.60      |

| b (Note 4)         | 0.22                                                      | 0.38       | 0.22       | 0.38     | 0.18       | 0.30      |

| с                  | 0.13                                                      | 0.23       | 0.13       | 0.23     | 0.13       | 0.20      |

| D, E (Note 5)      | 31.00                                                     | 31.40      | 31.00      | 31.40    | 30.40      | 30.80     |

| D1, E1<br>(Note 3) | 27.90                                                     | 28.10      | 27.90      | 28.10    | 27.90      | 28.10     |

| D3, E3             | 22.75                                                     | 5 REF      | 25.35 REF  |          | 25.50 REF  |           |

| e (Note 7)         | 0.65                                                      | BASIC      | 0.65 BASIC |          | 0.50 BASIC |           |

| aaa                | 0.13                                                      | NOM        | 0.13 NOM   |          | 0.08 NOM   |           |

| ссс                | 0.                                                        | 10         | 0.         | 10       | 0.08       |           |

| L                  | 0.73                                                      | 1.03       | 0.73       | 1.03     | 0.50       | 0.75      |

| Lead P             | 3                                                         | 6          | 4          | 0        | 5          | 2         |

| Lead Q             | 7                                                         | 2          | 8          | 0        | 1          | 04        |

| Lead R             | 10                                                        | )8         | 12         | 20       | 1          | 56        |

| Lead S             | 14                                                        | <b>1</b> 4 | 10         | 50       | 20         | 08        |

- 1. All dimensions are in millimeters, and the dimensions and tolerances conform to ANSI Y14.5M-1982.

- 2. Datum plane -A- is located at the mold parting line and is coincident with the bottom of the lead where the lead exits the plastic body.

- 3. Dimensions "D1 and E1" do not include mold protrusion. Allowable mold protrusion is 0.25 mm per side. (Also see Note 5.)

- 4. Dimension "b" does not include dambar protrusion.

- 5. Dimensions "D1 and E1" do include mold mismatch and are determined at datum plane -A-.

- 6. Dimensions "D and E" are measured from both the innermost and outermost points.

- Deviation from the lead-tip true position shall be within ±0.08 mm for packages having lead pitch >0.5 mm, and within ±0.04 mm when the pitch is≤0.5 mm.

- 8. Lead coplanarity shall be within 0.10 mm for devices baving lead pitch of 0.65—0.80 mm, and 0.08 mm when the lead pitch is 0.50 mm.

- 9. The half span (center of the package to the lead tip shall be within ±0.0085.

- 10. PQR (cavity up) is Vantis' internal abbreviation for metric PQFPs. Thermally-enhanced PQFPs are denoted by those with heat spreaders embedded in them (PRH for cavity up).

|           | Vantis Package Type & Leadcount<br>(JEDEC Drawing Number) |       |  |  |  |

|-----------|-----------------------------------------------------------|-------|--|--|--|

| Dimension | PQE208<br>(MO-143(B)FA-1)                                 |       |  |  |  |

| Codes     | Min                                                       | Max   |  |  |  |

| Α         | —                                                         | 3.70  |  |  |  |

| A1        | 0.25                                                      | 0.42  |  |  |  |

| A2        | 3.29                                                      | 3.45  |  |  |  |

| b         | 0.17                                                      | 0.27  |  |  |  |

| с         | 0.10                                                      | 0.20  |  |  |  |

| D, E      | 30.40                                                     | 30.80 |  |  |  |

| D1, E1    | 27.90                                                     | 28.10 |  |  |  |

| D3, E3    | 25.50                                                     | ) REF |  |  |  |

| e         | 0.50 I                                                    | BASIC |  |  |  |

| L         | 0.50                                                      | 0.75  |  |  |  |

| L1        | 1.30 NOM                                                  |       |  |  |  |

| aaa       | 0.08 NOM                                                  |       |  |  |  |

| ссс       | 0.08                                                      | NOM   |  |  |  |

- 1. All dimensions are in millimeters, and the dimensions and tolerances conform to ANSI Y14.5M-1982.

- 2. Datum plane -A- is located at the mold parting line and is coincident with the bottom of the lead where the lead exits the plastic body.

- 3. Dimensions "E1 and D1" do not include mold protrusion. Allowable mold protrusion is 0.25 mm per side. (See also Note 5.)

- 4. Dimension "b" does not include dambar protrusion.

- 5. Dimensions "E1 and D1" do include mold mismatch and are determined at datum plane -A-.

- 6. Dimensions "D and E" are measured from both the outermost points.

- 7. The pin-one ID may be inside the top ejector mark or separate.

- 8. The heatsink center line is aligned to the package body's center line at a tolerance of  $\pm 0.30$  mm.

- 9. The half span (center of the package to the lead tip) shall be within  $15.30 \pm 0.165$  mm.

- 10. No lead distortion (bent leads, etc.) shall cause deviation from the lead's true position by greater than  $\pm 0.04$  mm at the maximum of the "b" dimension.

- 11. Lead coplanarity with respect to the seating plan shall not exceed 0.08 mm.

- 12. PQE is Vantis' internal abbreviation for a cavity-up, metric PQFP that has been thermally enhanced with an exposed heat sink.

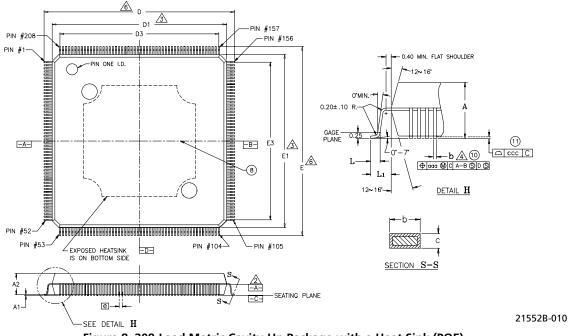

Figure 9. 240-Lead Metric Cavity-Up Package with a Heat Sink (PQE)

|           | Vantis Package Type & Leadcount<br>(JEDEC Drawing Number) |       |  |  |  |

|-----------|-----------------------------------------------------------|-------|--|--|--|

| Dimension | PQE240 (MO-143(B)/GA)                                     |       |  |  |  |

| Codes     | Min                                                       | Max   |  |  |  |

| A1        | 0.25                                                      | 0.45  |  |  |  |

| b         | 0.17                                                      | 0.27  |  |  |  |

| с         | 0.10                                                      | 0.20  |  |  |  |

| D, E      | 34.35                                                     | 34.85 |  |  |  |

| D1, E1    | 31.90                                                     | 32.10 |  |  |  |

| D3, E3    | 29.50                                                     | ) REF |  |  |  |

| e         | 0.50                                                      | BASIC |  |  |  |

| L         | 0.45                                                      | 0.75  |  |  |  |

| L1        | 1.30 NOM                                                  |       |  |  |  |

| aaa       | 0.08 NOM                                                  |       |  |  |  |

| ссс       | 0.08                                                      | NOM   |  |  |  |

- 1. All dimensions are in millimeters, and the dimensions and tolerances conform to ANSI Y14.5M-1982.

- 2. Datum plane -A- is located at the mold parting line and is coincident with the bottom of the lead where the lead exits the plastic body.

- 3. Dimensions "E1 and D1" do not include mold protrusion. Allowable mold protrusion is 0.25 mm per side. (See also Note 5.)

- 4. Dimension "b" does not include dambar protrusion.

- 5. Dimensions "E1 and D1" do include mold mismatch and are determined at datum plane -A-.

- Dimensions "D and E" are measured from both the outermost points.

- 7. The pin-one ID may be inside the top ejector mark or separate.

- 8. The beatsink center line is aligned to the package body's center line at a tolerance of ±0.30 mm.

- 9. The half span (center of the package to the lead tip) shall be within  $15.30 \pm 0.165$  mm.

- 10. No lead distortion (bent leads, etc.) shall cause deviation from the lead's true position by greater than ±0.04 mm at the maximum of the "b" dimension.

- 11. Lead coplanarity with respect to the seating plan shall not exceed 0.08mm.

- 12. PQE is Vantis' internal abbreviation for a cavity-up, metric PQFP that has been thermally enhanced with an exposed heat sink.

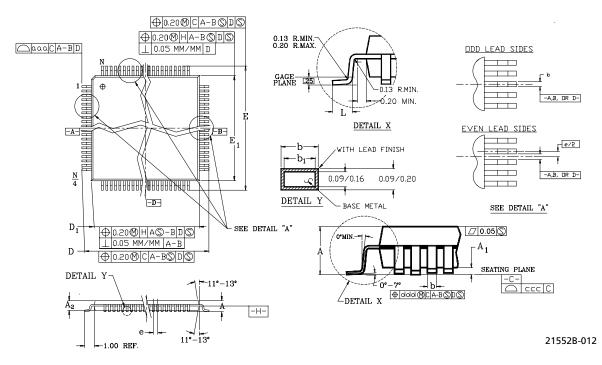

### Thin Quad Flat Pack (TQFP) Packages

The TQFP package is the same basic package design as a PQFP except the package is thinner, and the dimensions governing the solder land pattern are different. The thickness of the package body is 1.0 mm to 1.4 mm, versus the 3.5-mm thickness of a standard PQFP. This is possible because the die is back ground down to a 0.34-mm thickness.

The major applications for TQFP packages are in handheld products, small disk drives, doublesided boards, and PCMCIA cards.

Vantis' family of TQFP packages includes cavity-up versions (denoted internally as PQT and PQL) from 44 to 176 leads.

| Leadcount | Package Body<br>Area (L X W)<br>Inches Sq. (mm sq.) | Lead Pitch<br>Inches (mm) | Package Body<br>Thickness<br>Inches (mm) | Package Weight<br>(Grams) |

|-----------|-----------------------------------------------------|---------------------------|------------------------------------------|---------------------------|

| 44 (PQT)  | 0.155 (100)                                         | 0.03 (0.80)               | 0.04 (1.00)                              | 0.232                     |

| 48 (PQL)  | 0.076 (49)                                          | 0.02 (0.5)                | 0.055 (1.4)                              | 0.17                      |

| 100 (PQL) | 0.304 (196)                                         | 0.02 (0.50)               | 0.055 (1.40)                             | 0.63                      |

| 144 (PQL) | 0.62 (400)                                          | 0.02 (0.50)               | 0.055 (1.40)                             | 1.32                      |

| 176 (PQL) | 0.893 (576)                                         | 0.02 (0.50)               | 0.055 (1.40)                             | 1.82                      |

### Table 7. TQFP<sup>1</sup> Package Size Overview

#### Note:

1. PQT is Vantis' internal abbreviation for TQFPs baving a package body thickness of 1.0 mm. PQL denotes TQFPs with package body thickness of 1.4 mm.

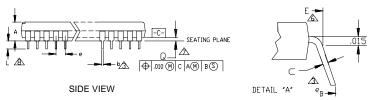

Figure 10. Thin Plastic Quad Flat Pack (TQFP) Packages

|                    | Vantis Package Type & Leadcount (JEDEC Drawing Number) |                 |      |                |       |                  |       |                  |       |                       |

|--------------------|--------------------------------------------------------|-----------------|------|----------------|-------|------------------|-------|------------------|-------|-----------------------|

| Dimension<br>Codes |                                                        | 044<br>5(A)ACB) |      | 048<br>6(B)AE) | · ·   | .100<br>5(A)BED) |       | .144<br>5(A)BFB) | •     | (note 12)<br>5(A)BGA) |

|                    | Min                                                    | Max             | Min  | Max            | Min   | Max              | Min   | Max              | Min   | Max                   |

| А                  | _                                                      | 1.20            | _    | 1.60           | _     | 1.60             | _     | 1.60             | _     | 1.60                  |

| A1                 | 0.05                                                   | 0.15            | 0.05 | 0.15           | 0.05  | 0.15             | 0.05  | 0.15             | 0.05  | 0.15                  |

| A2                 | 0.95                                                   | 1.05            | 1.35 | 1.45           | 1.35  | 1.45             | 1.35  | 1.45             | 1.35  | 1.45                  |

| D, E               | 11.80                                                  | 12.20           | 9.00 | BASIC          | 15.80 | 16.20            | 21.80 | 22.20            | 25.80 | 26.20                 |

| D1, E1             | 9.80                                                   | 10.20           | 7.00 | BASIC          | 13.80 | 14.20            | 19.80 | 20.20            | 23.80 | 24.20                 |

| L                  | 0.45                                                   | 0.75            | 0.45 | 0.75           | 0.45  | 0.75             | 0.45  | 0.75             | 0.45  | 0.75                  |

| N                  | 4                                                      | 4               | 4    | 8              | 10    | 00               | 14    | 44               | 1     | 76                    |

| e                  | 0.80                                                   | BASIC           | 0.50 | BASIC          | 0.50  | BASIC            | 0.50  | BASIC            | 0.50  | BASIC                 |

| b                  | 0.30                                                   | 0.45            | 0.17 | 0.27           | 0.17  | 0.27             | 0.17  | 0.27             | 0.17  | 0.27                  |

| b1                 | 0.30                                                   | 0.40            | 0.17 | 0.23           | 0.16  | 0.23             | 0.17  | 0.23             | 0.17  | 0.23                  |

| ссс                | _                                                      | 0.10            | _    | 0.08           | _     | 0.08             | _     | 0.08             | _     | 0.08                  |

| ddd                | _                                                      | 0.20            | _    | 0.08           | _     | 0.08             | _     | 0.08             | _     | 0.08                  |

| aaa                | _                                                      | 0.20            | —    | 0.20           | _     | 0.20             | —     | 0.20             | _     | 0.20                  |

1. All dimensions are in millimeters, and the dimensions and tolerances conform to ANSI Y14.5M-1982.

- 2. Datum plane -H- is located at the mold parting line and is coincident with the bottom of the lead where the lead exits the plastic body.

- 3. Dimensions "E1 and D1" do not include mold protrusion. Allowable mold protrusion is 0.254 mm per side. (See also Note 5.)

- 4. Dimension "b" does not include dambar protrusion. Allowable dambar protrusion shall be 0.08 mm total in excess of the "b" dimension at maximum material condition. The dambar cannot be located on the lower radius or the foot.

- 5. Dimensions "E1 and D1" do include mold mismatch and are determined at datum plane -H-.

- 6. Dimensions "D and E" are measured from both the innermost and outermost points.

- 7. Deviation from the lead-tip true position shall be within  $\pm 0.076$  mm for packages having lead pitch >0.5 mm, and within  $\pm 0.04$  mm when the pitch is  $\leq 0.5$  mm.

- 8. Lead coplanarity shall be within 0.10 mm for devices having lead pitch of 0.65—0.80 mm, and 0.08 mm when the lead pitch is 0.50 mm.

- 9. The half span (center of the package to the lead tip) shall be within ±0.16 mm.

- 10. "N" is the total number of terminals.

- 11. The top of the package is smaller than the bottom of the package by 0.15 mm.

- 12. PQT is Vantis' internal abbreviation for a 1.0-mm thick TQFP. PQL designates a 1.4-mm thick TQFP.

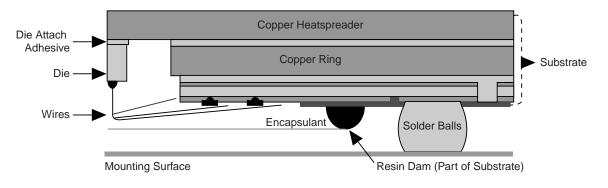

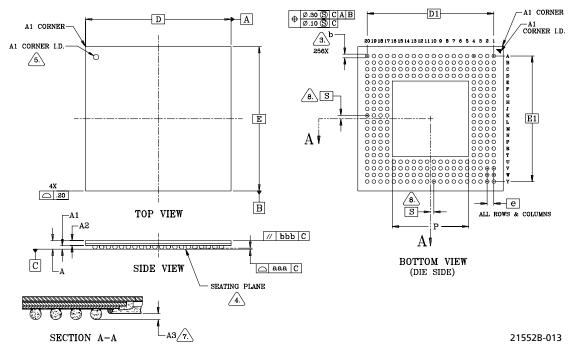

### Ball Grid Array (BGA) Packages

The BGA package is a relatively new package design which is gaining popularity as an attractive package solution for Programmable Logic and FPGA devices. It offers a high-density package with a smaller form/fit factor than a comparable leadcount quad flat pack package. More importantly, it is designed with solder balls instead of leads, which are more durable and loosely pitched than the fragile package leads of a comparable surface-mount component. This results in higher board yields.

### **Package Design**

The package consists of a thin Printed Circuit Board (PCB) made of a BT epoxy laminate, doublesided, and overlaid with copper over which metallized wire bond pads and a die pad are fabricated. The wirebond pads extend outward to plated through-hole vias located around the board's periphery. These vias provide the electrical continuity from the top of the board to the other side where copper traces run from the holes to a matrix of solder bumps. The bumps are soldered onto a land pattern on a circuit board in the end-use application. A solder mask is photo defined on the backside of the package to contain the flow of solder during board assembly.

The die is attached to the die pad using a standard epoxy die attach method. Gold ball bonding is used to connect the die pads to the wire bond pads, and the die is encapsulated with epoxy encapsulation material to protect it.

| Table 8. | BGA | Package | Size | Overview |

|----------|-----|---------|------|----------|

|----------|-----|---------|------|----------|

| Ball Count         | Package Body Area (L X W)<br>Inches Sq. (mm sq.) | Ball Pitch<br>Inches (mm) | Package Weight (Grams) |

|--------------------|--------------------------------------------------|---------------------------|------------------------|

| 256 (BGD) (Note 1) | 1.13 (729.0)                                     | 0.05 (1.27)               | 4.23                   |

| 352 (BGD) (Note 1) | 1.90 (1225.0)                                    | 0.03 (1.27)               | 6.99                   |

#### Note:

1. BGD is Vantis' internal abbreviation for a wirebonded, cavity-down, ball grid array, thermally enhanced with a heat slug

Figure 11. BGD Cross-section

21552B-029

|                        | Vantis Package Type &<br>Leadcount<br>(JEDEC Drawing Number) |       |                         |

|------------------------|--------------------------------------------------------------|-------|-------------------------|

|                        | BGD2<br>(MO-151(B                                            |       |                         |

| <b>Dimension Codes</b> | Min                                                          | Max   | Note                    |

| А                      | 1.10                                                         | 1.65  | overall thickness       |

| A1                     | 0.50                                                         | 0.70  | ball height             |

| A2                     | 0.60                                                         | 0.95  | body thickness          |

| A3 (Note 7)            | 0.15                                                         | 0.45  | seating plane clearance |

| D, E                   | 27.00 H                                                      | BASIC | body size               |

| D1, E1                 | 24.13 H                                                      | BASIC | ball footprint          |

| М                      | 20 x                                                         | 20    | ball matrix size        |

| Ν                      | 25                                                           | 6     | total ball count        |

| MR (Note 6)            | 4                                                            |       | number of rows deep     |

| е                      | 1.27 BASIC                                                   |       | ball pitch              |

| b                      | 0.60                                                         | 0.90  | ball diameter           |

| Р                      | 14.8                                                         | 15.2  | encapsulation area      |

| S                      | 0.635 I                                                      | BASIC | solder ball placement   |

1. BGD is Vantis' internal abbreviation for a wirebonded, plastic, cavity-down ball grid array that has been thermally enhanced with a heat sink.

| Geometric Tolerances |      |             |

|----------------------|------|-------------|

| aaa                  | 0.15 | coplanarity |

| bbb                  | 0.15 | parallelism |

1. All dimensions are in millimeters.

- 2. Dimensioning and tolerancing conform to ASME Y14.5M-1994.

- 3. Dimension "b" is measured at the maximum solder ball diameter on a plane parallel to datum C.

- 4. Datum C and the seating plane are defined by the spherical crowns of the solder balls.

- 5. A1 corner I.D. is marked with ink.

- 6. Refers to the number of peripheral rows or columns.

- 7. *Refers to the height from the encapsulation to the seating plane.*

- 8. "S" is measured with respect to datums A and B and defines the position of the solder balls nearest the package centerlines. When there is an odd number of solder balls in the outer row "S" = 0.000; when there is an even number of solder balls in the outer row the value "S" = e/2.

21552B-014

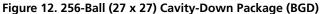

|             | Vantis Package Type & Leadcount<br>(JEDEC Drawing Number) |       |                         |

|-------------|-----------------------------------------------------------|-------|-------------------------|

| Dimension   | BGD<br>(MO-151(B                                          |       |                         |

| Codes       | Min                                                       | Max   | Note                    |

| Α           | 1.10                                                      | 1.65  | overall thickness       |

| A1          | 0.50                                                      | 0.70  | ball height             |

| A2          | 0.60                                                      | 0.95  | body thickness          |

| A3 (Note 7) | 0.15                                                      | 0.45  | seating plane clearance |

| D, E        | 35.001                                                    | BASIC | body size               |

| D1, E1      | 31.75 1                                                   | BASIC | ball footprint          |

| М           | 26 x                                                      | 26    | ball matrix size        |

| Ν           | 35                                                        | 2     | total ball count        |

| MR (Note 6) | 4                                                         |       | number of rows deep     |

| e           | 1.27 B                                                    | ASIC  | ball pitch              |

| b           | 0.60                                                      | 0.90  | ball diameter           |

| Р           | 20.4                                                      | 21.2  | encapsulation area      |

| S           | 0.6351                                                    | BASIC | solder ball placement   |

| Geometric Tolerances |      |             |

|----------------------|------|-------------|

| aaa                  | 0.15 | coplanarity |

| bbb                  | 0.15 | parallelism |

1. All dimensions are in millimeters.

- 2. Dimensioning and tolerancing conform to ASME Y14.5M-1994.

- *3. Dimension "b" is measured at the maximum solder ball diameter on a plane parallel to datum C.*

- 4. Datum C and the seating plane are defined by the spherical crowns of the solder balls.

- 5. A1 corner I.D. marked by ink.

- 6. Refers to the number of peripheral rows or columns.

- 7. Refers to the height from the encapsulation to the seating plane.

- 8. "S" is measured with respect to datums A and B and defines the position of the solder balls nearest the package centerlines. When there is an odd number of solder balls in the outer row "S" = 0.000; when there is an even number of solder balls in the outer row the value "S" = e/2.

- 9. BGD is Vantis' internal package abbreviation for a wirebonded, plastic, cavity-up package.

### Plastic Dual-In-Line Packages (PDIP)

The Plastic Dual-In-Line package (PDIP) construction consists of a device attached to the die pad of a leadframe, the circuitry of which is wire bonded to the lead fingers. A plastic epoxy material is injection-molded to encapsulate the device/leadframe configuration. The leads are trimmed and formed to a through-hole lead design, with lead extensions along the two long ends of the rectangular package.

| Leadcount         | Package Body<br>Area (L X W)<br>Inches | Lead Pitch<br>Inches | Package<br>Weight<br>(Grams) |

|-------------------|----------------------------------------|----------------------|------------------------------|

| 20                | 0.267                                  |                      | 1.39                         |

| 24                | 0.69                                   | 0.10                 | 3.55                         |

| 24 (PD3 (Note 1)) | 0.32                                   | 0.10                 | 1.60                         |

| 28                | 0.81                                   |                      | 4.20                         |

#### Table 9. PDIP (PD) Package Size Overview

#### Note:

1. PD3 (300 mil) designate PDIP designs for which the package mil size is not what is standard for that lead count.

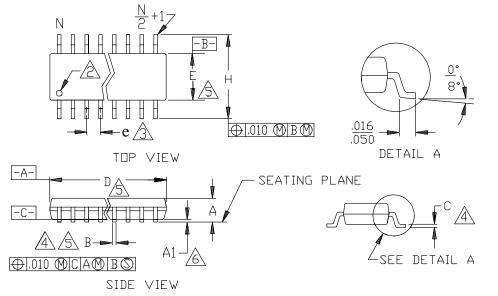

TOP VIEW

END VIEW

Figure 14. Plastic Dual-In-Line (PDIP) Packages

21552B-015

|                         | Vantis Package Type & Leadcount (JEDEC Drawing Number) |       |                             |              |               |                         |       |                                       |       |       |

|-------------------------|--------------------------------------------------------|-------|-----------------------------|--------------|---------------|-------------------------|-------|---------------------------------------|-------|-------|

|                         |                                                        |       | PD                          | D 024 PD3024 |               | PD 028<br>(MS-011(B)AB) |       | PD3028<br>(288 body)<br>(MO-095(A)AH) |       |       |

| Dimension               |                                                        |       | (MS-001(D)AD) (MS-011(B)AA) |              | (MS-011(B)AA) |                         |       |                                       |       |       |

| Codes                   | Min                                                    | Max   | Min                         | Max          | Min           | Max                     | Min   | Max                                   | Min   | Max   |

| А                       | 0.140                                                  | 0.200 | 0.140                       | 0.225        | 0.140         | 0.200                   | 0.140 | 0.225                                 | 0.140 | 0.180 |

| b                       | 0.014                                                  | 0.022 | 0.014                       | 0.022        | 0.014         | 0.022                   | 0.014 | 0.022                                 | 0.014 | 0.022 |

| b1                      | 0.045                                                  | 0.065 | 0.045                       | 0.065        | 0.045         | 0.065                   | 0.45  | 0.65                                  | 0.45  | 0.60  |

| С                       | 0.008                                                  | 0.015 | 0.008                       | 0.015        | 0.008         | 0.015                   | 0.008 | 0.015                                 | 0.008 | 0.015 |

| D                       | 1.010                                                  | 1.040 | 1.240                       | 1.280        | 1.150         | 1.270                   | 1.440 | 1.480                                 | 1.345 | 1.385 |

| E1                      | 0.240                                                  | 0.280 | 0.520                       | 0.580        | 0.240         | 0.280                   | 0.530 | 0.580                                 | 0.275 | 0.295 |

| Е                       | 0.300                                                  | 0.325 | 0.600                       | 0.625        | 0.300         | 0.325                   | 0.600 | 0.625                                 | 0.300 | 0.325 |

| e                       | 0.090                                                  | 0.110 | 0.120                       | 0.160        | 0.120         | 0.160                   | 0.090 | 0.110                                 | 0.090 | 0.110 |

| L                       | 0.120                                                  | 0.160 | 0.090                       | 0.110        | 0.090         | 0.110                   | 0.120 | 0.160                                 | 0.120 | 0.150 |

| Q                       | 0.015                                                  | 0.060 | 0.015                       | 0.060        | 0.015         | 0.060                   | 0.015 | 0.060                                 | 0.015 | 0.060 |

| \$1                     | 0.005                                                  | _     | 0.005                       | _            | 0.005         | _                       | 0.005 | _                                     | 0.005 | _     |

| e <sub>b</sub>          | 0.330                                                  | 0.430 | 0.630                       | 0.700        | 0.330         | 0.430                   | 0.630 | 0.700                                 | 0.330 | 0.430 |

| $(\alpha_1 - \alpha_2)$ | 00                                                     | 10°   | 0°                          | 10°          | 0°            | 10°                     | 0°    | 10°                                   | 0°    | 10°   |

| $(\alpha_1, \alpha_2)$  | 00                                                     | 15°   | 0°                          | 15°          | 0°            | 15°                     | 0°    | 15°                                   | 0°    | 15°   |

| N                       | 20                                                     |       | 2                           | .4           | 2             | 4                       | 2     | 8                                     | 2     | 8     |

1. All dimensions are in inches.

- 2. A notch, tab, or pin one identification mark shall be located adjacent to the device pin one.

- 3. Lead thickness increases by a maximum of 0.003 inch when a the solder lead finish is applied.

- 4. These dimensions do not include mold flash or protrusion.

- 5. This dimension is measured from the outside of the leads and 0.015 inch below the plane of the package exit, as defined by the top of the lead.

- 6. This dimension is measured from the seating plane to the base plane.

- 7. This dimension is measured from the seating plane (or from the lowest point of the lead shoulder width that measures 0.040 inch) to the lead tip.

- 8. The difference between these two dimensions should not exceed 7°.

- 9. When standoff has radii, the seating plane location is defined where the lead width equals 0.040 inch.

- 10. PD is Vantis' internal designator for a plastic dual-in-line package.

### Small Outline (SOIC) Plastic Packages

The SOIC package is an surface-mount alternative for low leadcount devices. Its design is similar to the conventional Dual-In-Line (DIP) package—an attractive feature for circuit designers already familiar with DIPs and memory boards.

Like plastic DIPs, the SOIC package consists of a device attached to the die pad of a leadframe, the circuitry of which is wire bonded to the lead fingers. A plastic epoxy material is injection-molded to encapsulate the device/leadframe configuration. The leads extending from the two long sides of the rectangular package body are trimmed and formed to a gull-wing formation.

The 50-mil lead pitch of SOIC packages allows for considerable reduction in package size over comparable DIPs, as shown in the table to the right. Not only are SOIC packages smaller, they are lighter, too. This makes them ideal for foil/film mounting and virtually all automated board assembly operations.

| Leadcount | Package Body<br>Area (L X W)<br>Inches Sq.<br>(mm sq.) | Lead Pitch<br>Inches (mm) | Package Weight (Grams) |

|-----------|--------------------------------------------------------|---------------------------|------------------------|

| 20        | 0.149 (96.13)                                          | 0.05 (1.27)               | 0.51                   |

| 24        | 0.180 (115.51)                                         | 0.03 (1.27)               | 0.62                   |

### Table 10. SOIC (SO)<sup>1</sup> Package Size Overview

#### Note:

1. SO is Vantis' internal abbreviation for an SOIC package.

#### Figure 15. JEDEC English Packages

21552B-017

**General Information**

|           | Vantis Package Type & Leadcount |        |             |        |  |  |  |

|-----------|---------------------------------|--------|-------------|--------|--|--|--|

| Dimension | SO                              | 20     | SO 24       |        |  |  |  |

| Codes     | Min                             | Max    | Min         | Max    |  |  |  |

| A         | 0.0926                          | 0.1043 | 0.0926      | 0.1043 |  |  |  |

| A1        | 0.0040                          | 0.0118 | 0.0040      | 0.0118 |  |  |  |

| В         | 0.0138                          | 0.0192 | 0.0138      | 0.0192 |  |  |  |

| С         | 0.0091                          | 0.0125 | 0.0091      | 0.0125 |  |  |  |

| D         | 0.4961                          | 0.5118 | 0.5985      | 0.6141 |  |  |  |

| е         | 0.050                           | BASIC  | 0.050 BASIC |        |  |  |  |

| Е         | 0.2914                          | 0.2992 | 0.2914      | 0.2992 |  |  |  |

| Н         | 0.3940                          | 0.4190 | 0.3940      | 0.4190 |  |  |  |

| N         | 20                              | )      | 24          |        |  |  |  |

- 1. All dimensions are in inches.

- 2. An identification mark shall be located adjacent to the device pin one.

- 3. Dimension "e" is measured at the center line of the leads.

- 4. Dimensions "B" and "C" increase by 0.003 inch maximum for all leads when solder dip lead finish is applied.

- 5. Dimension "B" does not include dambar protrusion. Allowable protrusion is 0.004 inch.

- 6. Dimensions "A1" is measured from the base plane of contact, which is made when the packaged is allowed to rest freely on a flat, borizontal surface.

- 7. Lead coplanarity shall be within 0.004 inch as measured from the seating plane.

- 8. SO is Vantis' internal abbreviation for an SOIC package.

# PACKAGE DESIGN ADVANTAGES

The BGA package design offers many advantages over other high leadcount packages.

## **Board Real Estate Savings**

Because of the small package size, the BGA offers significant savings in board real estate, occupying about 51 percent of the space a comparable QFP requires. It has a lower profile, too, about one third as thick as a plastic quad flat pack (PQFP) package.

## **Electrical Performance**

The BGA offers superior electrical performance because the shorter wirebond lengths in it help reduce inductance. Comparing a 169-ball BGA to a 160-Pin PQFP, the BGA shows a 31 percent reduction in signal capacitance and a 46 percent reduction in signal time delay.

## **Thermal Performance**

Studies have been conducted that show that the BGA thermally outshines a comparable PQFP when it is fabricated with "thermal vias" (i.e., through-hole vias) underneath the die pad. These vias allow heat generated by the device to flow to the board, which would improve thermal performance provided the board has a conducting plane built into it. To more accurately ascertain the thermal performance of a BGA, the specific end-use application environment needs to be considered.

## **Board Assembly Advantages**

The pitch of the solder balls on a BGA is far more manageable during board assembly, at 1.0 to 1.5 mm, than the typical 0.5-mm pitch of high leadcount Quad Flat Packs (QFPs).

BGAs can be handled with the same pick-and-place equipment that is used for conventional surface-mount devices, including solder reflow methods. During reflow assembly, the wetting action of the solder balls tends to pull them into alignment so that placement of the component on the solder land does not need to be nearly as precise as with a QFP. The alignment can be off by as much as 6 mils—more forgiving than the 3 mils (0.076 mm) required for fine lead-pitch QFPs.

## **Post Assembly Inspections**

Once the BGA is mounted on the board, there is the challenge of how to inspect the ball joints. Thus far, x-ray techniques appear the most viable solution, although these systems can be quite expensive. Once the component is mounted, it can be removed and a new component remounted; however, there is currently no process for reworking the removed component for reuse.

## Vantis' Development Plans

Vantis is currently shipping BGA packages with body sizes of 27 mm x 27 mm and 35 mm x 35 mm at 1.27 mm ball pitch. Vantis will continue to develop other enhanced BGA packages with smaller ball pitches, better thermal performance and higher ball counts with smaller body sizes for our future products.

# THERMAL CHARACTERIZATION OF PACKAGES

With the increased density and complexity of CMOS VLSI semiconductor devices, the need to accurately evaluate the thermal properties of packaged Integrated Circuits (ICs) is fundamental to the understanding and prediction of device reliability and performance. Failure rates are inseparably tied to the operating temperature of the device, and they increase exponentially as the temperature of the device junction rises. Therefore, it is important that the junction temperature of every IC in the system be controlled to attain high reliability and a long operating life. Likewise, understanding the thermal properties of each component in the system is important for addressing overall thermal concerns at the system level given the end-use application environment.

Thermal performance data is usually measured in the form of thermal resistance or thermal impedance characteristics ( $R\theta_{JA}$ ,  $\theta_{JA}$ ), and it is used to estimate the junction temperature of a device operating in a given environment. A certain amount of caution should be exercised, however, when using thermal data to design or evaluate systems because many factors influence the thermal performance of the chip-package combination. These factors include such phenomenon as the ambient temperature, the power dissipation of the chip, the thermal conductivity of the Printed Circuit Board (PCB), the proximity and power dissipation of neighboring devices, and the airflow through the system. Therefore, it is important to carefully evaluate and analyze the entire system and its environment before utilizing any standard thermal data. Vantis reports data using the JEDEC JESD51 specification format so that the end user can approximate the effect of the application environment.

The following sections detail the methodology and techniques used by Vantis to evaluate the thermal performance of our devices, with an emphasis on fundamental heat flow properties. Our methods comply with established standards, both government and commercial, and we meet or exceed all military specifications for testing and reporting data. Our thermal data is collected for still air, moving air, and isothermal case temperature, using measurement techniques that are in conformance with MIL-SPEC 883D, Method 1012.1 specifications. We also adhere to the recently published improved standards for the thermal test method, environmental considerations, and mounting surface specification. These were published by the Engineering Industries Association (EIA) and Joint Electronic Devices Engineering Council (JEDEC), and they are documented in the JESD51 series.

At Vantis, we are committed to providing current and relevant thermal information for every product we manufacture. In our state-of-the art thermal characterization facility, we can evaluate the thermal performance of any Vantis product. Customers interested in product-specific thermal data should contact a Vantis sales representative.

# TERMINOLOGY

The most common terminology used in the industry for specifying thermal performance is the  $\theta_{JA}$  term and related forms. These are used to describe the thermal characteristics of semiconductor devices in various environments such as natural or forced convection. They are also used when simulating an infinite heat sink as in junction-to-case measurements. In addition, a new term has been recently defined to meet the needs of end users of plastic surface-mount packages. Denoted as  $\Psi_{JT}$  this measurement will allow a case temperature measurement during thermal test, which can then relate the case temperature in a free convection boundary condition to the junction temperature. The  $\Psi_{JT}$  parameter also helps to validate junction temperature measurements and calculations during thermal characterization.

The terminology commonly used to specify thermal performance, and mathematical constructs for calculating thermal resistance parameters, are provided in the following pages.

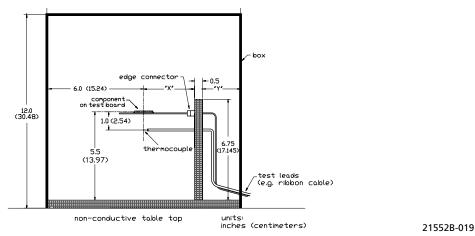

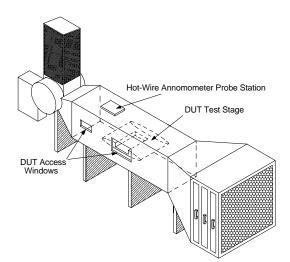

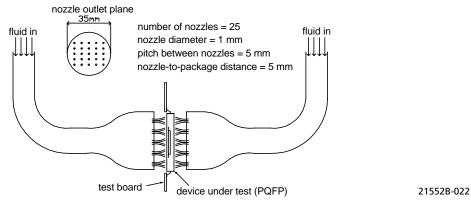

# **MEASUREMENT METHODS**

Vantis uses two primary test methods to evaluate the thermal resistance of packaged ICs: the live device method and the thermal test die method. In both methods, we utilize a heat source that is mounted within the package. For the live device method, it is a thermal test chip.