### **Analog and Mixed-Signal Products**

# Analog Applications Journal

February 2000

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

To receive other editions of *Analog Applications Journal*, please return the enclosed reply card or sign up at www.ti.com/sc/analogapps

## **Contents**

| Introductioniv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Acquisition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| A methodology of interfacing serial A-to-D converters to DSPs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| The operation of the SAR-ADC based on charge redistribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Power supply solutions for TI DSPs using synchronous buck converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Powering Celeron-type microprocessors using TI's TPS5210 and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| The new TPS5210EVM-147 (SLVP147) evaluation module confirms that TI's TPS5210 and TPS5211 hysteretic controllers provide a cost-effective solution to supply future Celeron microprocessors. The evaluation module includes a synchronous DC-DC buck converter with a DC load current of 14.5 A (up to 18.4 A during transients), high-frequency decoupling capacitors for PGA-370 microprocessor packages, and a load current transient tester. The module meets electrical specifications in the Intel document titled "VRM 8.4 DC-DC Converter Design Guidelines" for >733-MHz clock and 133-MHz bus-frequency Celeron processors. The detailed test results are presented in this article. |

| <b>Data Transmission</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

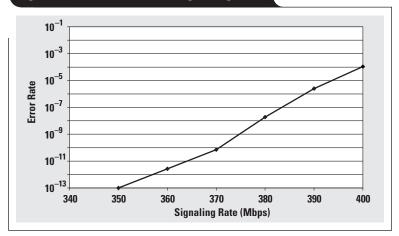

| Skew definition and jitter analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| LVDS receivers solve problems in non-LVDS applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Amplifiers: Op Amps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

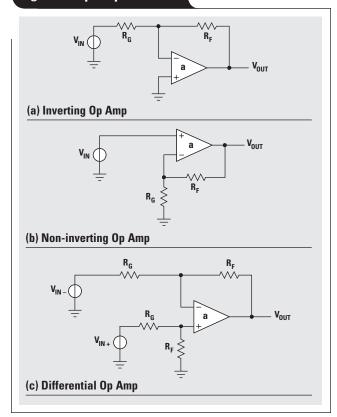

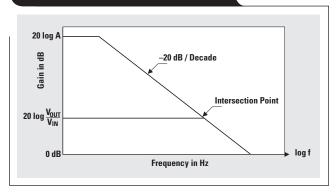

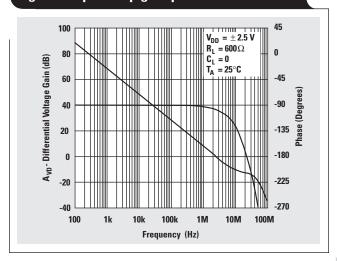

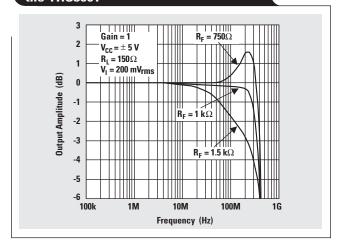

| Matching operational amplifier bandwidth with applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Amplifiers: Audio Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

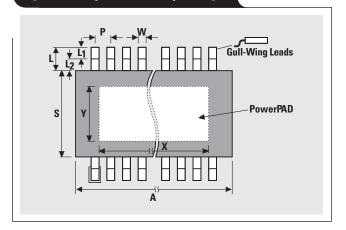

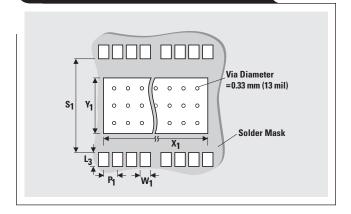

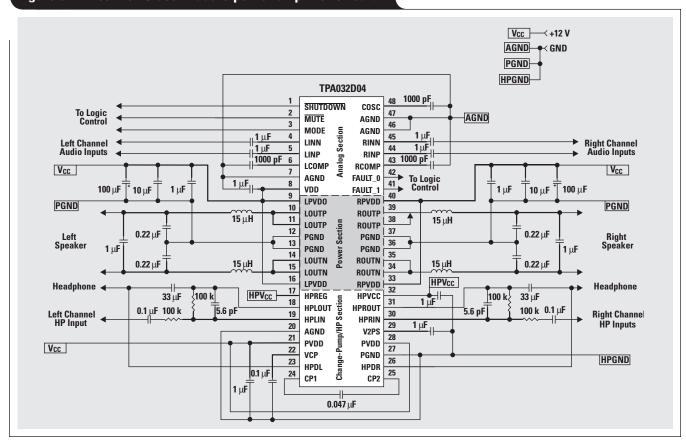

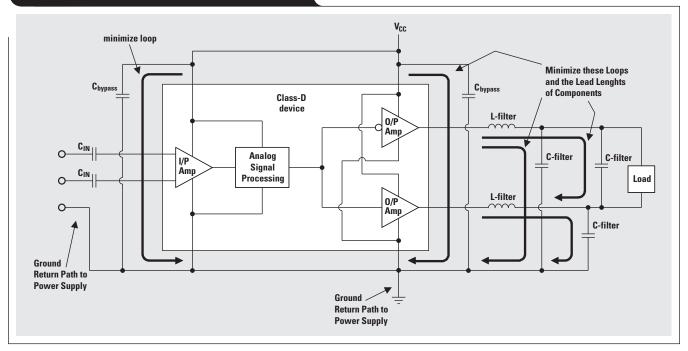

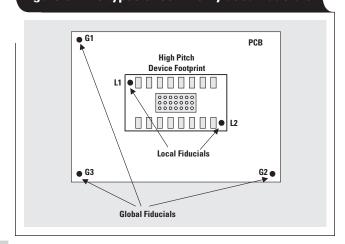

| PCB layout for the TPA005D1x and TPA032D0x Class-D APAs.  Following sensible printed circuit board (PCB) layout practices will ensure peak performance and reliability from Class-D audio power amplifiers. A good thermal and mechanical bond between the device pins and PowerPAD <sup>TM</sup> and the PCB landings (pads) will provide the necessary electrical and thermal pathways. This article shows how this can be achieved with an understanding of the basic manufacturing process and a proper layout of the IC and PowerPAD footprint.                                                                                                                                           |

| TI Worldwide Technical Support 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

### Introduction

Analog Applications Journal is a collection of analog application articles designed to give readers a basic understanding of TI products and to provide simple but practical examples for typical applications. Written not only for design engineers but also for engineering managers, technicians, system designers and marketing and sales personnel, the book emphasizes general application concepts over lengthy mathematical analyses.

These applications are not intended as "how-to" instructions for specific circuits but as examples of how devices could be used to solve specific design requirements. Readers will find tutorial information as well as practical engineering solutions on components from the following product categories:

- Data Acquisition

- Power Management

- Data Transmission

- Amplifiers

Where applicable, readers will also find software routines and program structures. Finally, *Analog Applications Journal* includes helpful hints and rules of thumb to guide readers in preparing for their design.

Because this book is limited in size, readers should refer to more detailed technical information, which can be found on TI's product-specific websites listed at the end of each article.

## A methodology of interfacing serial A-to-D converters to DSPs

#### By Thomas Kugelstadt

Application Manager

#### Introduction

Designers of DSP systems often have to rewrite their interface software when a desired increase in system performance requires the replacement of the current A-to-D converter with a device of higher speed or resolution. This article describes a method for interfacing various types of serial ADCs to the standard serial port of a DSP (TMS320C50) while keeping the software modifications at a minimum. It concludes with the introduction of "C-callable assembler routines" provided by TI's application staff that relieve the experienced C-programmer from performing tedious assembler studies.

#### Serial analog-to-digital converters

Table 1 lists a range of serial ADCs that interface directly to DSPs without additional control logic. All these devices have the following in common:

- the conversion is performed by successive approximation based on charge redistribution,

- a conversion is initiated by an external trigger signal, and

- the data format for the transfer between DSP and ADC is 16 bits.

For purposes of describing interface timing the devices in Table 1 are grouped in two categories:

- on-the-fly converters that perform a conversion while exchanging data with the host, and

- sequential converters that execute a conversion following a data transfer.

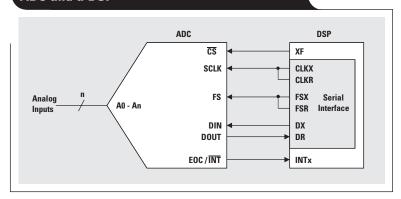

Figure 1 shows a typical interface between a DSP and a serial ADC. The DSP general-purpose I/O XF signal activates the ADC. The control and data signals of the DSP serial port manage the transfer of data. The additional EOC/INT output, only available on sequentially converting ADCs, signals the end of a conversion to the DSP, indicating that a new transfer can begin.

Figure 1. Typical serial interface between an ADC and a DSP

Before the timing sequence of a data transfer is discussed, the reader should understand the internal operation of the standard serial interface.

#### Standard serial interface

TI provides a variety of DSPs with different types of serial interfaces including:

- buffered serial port (BSP) with auto-buffering unit module (AMU),

- buffered serial interfaces with internal FIFO, and

- time-division-multiplex (TDM) serial interfaces, particularly useful for telecom applications.

The standard serial interface is the focus of this discussion because it is used far more often than the BSP or the TDM serial port. The serial port interfaces to data converters via the following six control lines:

**CLKX** Transmit clock input or output. This signal clocks data from the transmit shift register (XSR) to the DX pin. The serial port can be configured for internal clock generation or to accept an external clock. If the port is configured to generate the

Table 1. Family of serial A-to-D converters

| DEVICE  | CONVERSION | SUPPLY<br>(V) | RESOLUTION<br>(bits) | INPUT<br>CHANNEL | CONVERSION<br>RATE (MSPS) | POWER<br>DOWN | SWEEP<br>MODE | FIFO |

|---------|------------|---------------|----------------------|------------------|---------------------------|---------------|---------------|------|

| TLV1570 | On-the-fly | 2.7 – 5.5     | 10                   | 1                | 1.25                      | Auto          | -             | _    |

| TLV1572 | On-the-fly | 2.7 – 5.5     | 10                   | 8                | 1.25                      | Auto          | ~             | -    |

| TLV1544 | Sequential | 2.7 – 5.5     | 10                   | 4                | 0.1                       | Prog.         | ~             | -    |

| TLV1548 | Sequential | 2.7 – 5.5     | 10                   | 8                | 0.1                       | Prog.         | ~             | _    |

| TLV2544 | Sequential | 2.7 – 5.5     | 12                   | 4                | 0.2                       | Prog.         | ~             | V    |

| TLV2548 | Sequential | 2.7 – 5.5     | 12                   | 8                | 0.2                       | Prog.         | ~             | ~    |

| TLC2554 | Sequential | 5.0           | 12                   | 4                | 0.4                       | Prog.         | ~             | ~    |

| TLC2558 | Sequential | 5.0           | 12                   | 8                | 0.4                       | Prog.         | ~             | V    |

data clock on-chip, CLKX becomes an output, providing the data clock for the serial interface. If the port is configured to accept an external clock, CLKX changes to an input, receiving the external clock signal.

- FSX Transmit frame synchronization input or output. FSX indicates the start of a transmission. The serial port can be configured for internal framesync generation or to accept an external framesync signal. If the port is configured to generate the frame sync pulse on-chip, FSX becomes an output. If the port is configured to accept an external frame sync pulse, this pin becomes an input.

- **DX** Serial data transmit. DX transmits the actual data from the transmit shift register (XSR).

- **CLKR** Receive clock input. CLKR always receives an external clock for clocking the data from the DR pin into the receive shift register (RSR).

- **FSR** Receive frame synchronization input. FSR always receives an external frame sync pulse to initiate the reception of data at the beginning of a frame.

- **DR** Serial data receive. DR receives the actual data which are clocked into the receive shift register (RSR).

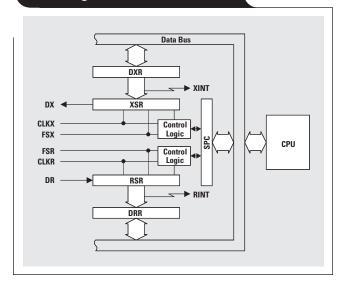

Figure 2 shows the block diagram of the standard serial interface. The operation of the serial port is supported by the following five 16-bit registers:

- **DXR** Data transmit register. Transmit data are written by the CPU into this register and then copied into the XSR. The DXR provides double buffering function by allowing the CPU to update its content via a new write-cycle, while the previous data transmit out of XSR is still ongoing.

- XSR Transmit shift register. Transmit data are copied from the DXR into the XSR and sent to the data converter.

- **RSR** Receive shift register. Receive data from the data converter are clocked into this register and then copied to the DRR.

- DRR Data receive register. Receive data, copied from the RSR, are read by the CPU from this register. The DRR provides double buffering function by allowing the CPU to read its content, while the next data reception into RSR has already started.

- **SPC** Serial port control register. The SPC contains control bits, which are set by the CPU to configure the operation of the serial port.

Figure 2. Standard serial interface block diagram

#### Serial port general operation

In the transmit direction the CPU initiates a data transfer by writing transmit data to the DXR. Then the data are copied from the DXR into the XSR and clocked out to the DX output. Upon the completion of a DXR-to-XSR copy, a transmit interrupt, XINT, is generated. This interrupt signals the CPU that new data can be written into the DXR.

In the receive direction the incoming data are clocked into RSR and then copied into DRR. Upon the completion of the data copy, a receive interrupt, RINT, is generated. This interrupt signals the CPU that new data are available in DRR. The CPU needs to read these data, while the next receive frame is clocked into the RSR.

#### Serial port configuration

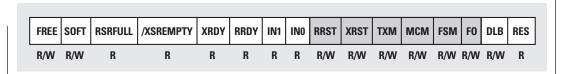

Before a data transfer can be executed, the serial port needs to be configured via the serial port control register, SPC. Figure 3 shows the 16-bit memory-mapped SPC of the TMS320C50DSP (R = read-only bits, R/W = read/write bits).

Out of the 16 bits of the SPC, only six R/W bits (shaded bits in Figure 3) are used to configure the serial port. The remaining non-shaded R/W bits, such as the emulation bits FREE and SOFT, and the digital loop back bit, DLB, are set to zero (FREE = SOFT = DLB = 0).

Figure 3. Serial port control register

Table 2 explains the functions of the six bits that configure the serial port.

The following example shows a typical serial port configuration when interfacing to a serial A-to-D converter from Texas Instruments.

- For standard serial port operation, all non-shaded R/W bits are set to zero (Free = Soft = DLB = 0).

- During the SPC configuration the serial port transmitter and receiver need to be disabled by setting the respective reset bits to zero (/XRST = /RRST = 0).

- Assuming that no external clock and frame sync generator are used, both signals need to be generated on-chip, thus requiring that TXM and MCM be set to one (TXM = MCM = 1).

- To comply with the 16-bit data format of the A-to-D converter, FO is set to zero (FO = 0).

- As mentioned previously, all serial ADCs require a trigger signal for each data transfer plus subsequent conversion. As will be shown in the following section, this trigger signal is already available through the FS-pulse of the serial port. For this purpose the serial port needs to be configured for burst mode operation by setting FSM to one (FSM = 1).

Figure 4 shows the resulting binary pattern with the corresponding hex code that is loaded into the SPC.

The assembler instruction <code><< SPLK #0038h</code> , <code>SPC >> commands</code> the CPU to write the content 38h into the serial control register, SPC. The CPU then activates the serial port via a second instruction <code><< SPLK #00F8h</code> , <code>SPC >> by setting the /XRST</code> and <code>/RRST</code> bit to one.

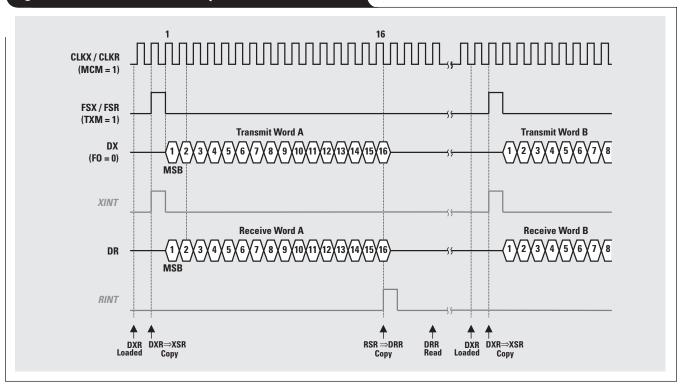

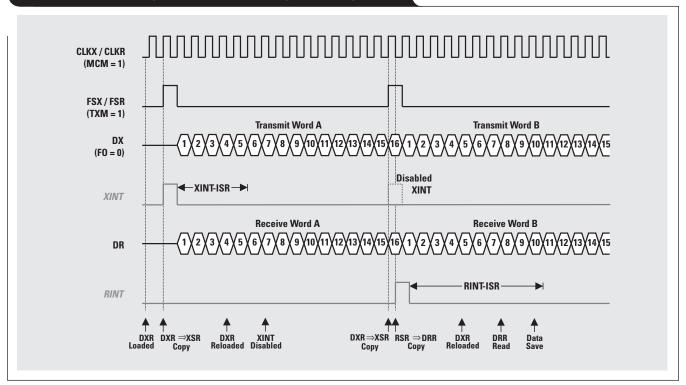

#### Transmit and receive operations in burst mode

The serial port can be programmed for continuous mode or burst mode operation. Both modes indicate the beginning of a data frame via a frame-sync pulse at FS. In continuous mode, only one FS-pulse is needed to indicate the beginning of a number of consecutive data frames. In burst mode, an FS-pulse indicates the start of one data frame (16 SCLK cycles) only, thereby providing the required trigger signal for an A-to-D conversion. Therefore, the serial port needs to operate in burst mode. Figure 5 shows the interface timing of the serial port in burst mode operation.

The data clock has the two designators CLKX and CLKR because the clock signal of the serial port transmitter is

Table 2. Important SPC bits for an ADC/DSP interface

| NAME       | FUNCTION                                                                  |

|------------|---------------------------------------------------------------------------|

| /XRST/RRST | The Transmit and Receive reset signals activate and deactivate the        |

|            | transmitter and receiver of the serial port.                              |

|            | /XRST, / RRST = 1, transmitter and receiver are active                    |

|            | /XRST, / RRST = 0, activity halts                                         |

| TXM        | The Transmit Mode bit specifies the source for FSX-pulse generation.      |

|            | TXM = 1, FSX is generated on-chip and synchronized to CLKX                |

|            | TXM = 0, FSX needs to be applied from external source                     |

| MCM        | The Clock Mode bit specifies the clock source for CLKX.                   |

|            | MCM = 1, on-chip clock source is used                                     |

|            | MCM = 0, external clock source is chosen                                  |

| FSM        | The Frame Synch Mode bit specifies when a frame sync pulse is needed.     |

|            | FSM = 1, Burst Mode is selected (an FS-pulse is used for each word)       |

|            | FSM = 0, Continuous Mode is selected (only one start pulse is required)   |

| F0         | The Format bit specifies the word length of the transmitter and receiver. |

|            | FO = 0, word length is 16-bit                                             |

|            | FO = 1, word length is 8-bit                                              |

identical to the one of the serial port receiver. Figure 1 shows that when the serial port is configured for on-chip clock generation (MCM = 1), CLKX is not only connected to the clock input of the ADC but also fed back into the data clock input of the serial port receiver. The same is valid for the frame-sync signals, FSX and FSR.

A data transfer is initiated by the CPU writing transmit data (i.e., ADC configuration data) into the data transmit register, DXR. With the second rising edge of CLKX, the content of DXR is copied into the transmit shift register, XSR. At this time, a frame-sync pulse and a transmit interrupt, XINT, are generated. With the first rising edge of CLKX after FSX has gone low, transmit data are shifted out to the DX-pin while receive data are clocked into the receive shift register, RSR, via the DR-pin. Both data streams, in transmit and receive, start with the most significant bit, MSB. While data change with the rising edge of CLKX, the falling edge of CLKX latches the transmit data into the ADC and the receive data into RSR. With the 16th falling edge of CLKX (after FSX has gone low). the receive shift register, RSR, is full. The content of RSR is copied into the data receive register, DRR, and a receive interrupt, RINT, is generated. The falling edge of the 16th CLKX cycle completes an entire data transfer, both in receive and transmit. Any further data transfer needs to be initiated with a CPU reload of DXR.

The serial port interrupts, XINT and RINT (shaded gray in Figures 5 and 6), represent internal signals, which are available to the CPU only. If either one of these interrupts

Figure 4. Serial port configuration code

| FREE | SOFT | RSRFULL | /XSREMPTY | XRDY | RRDY | IN1 | IN0 | RRST | XRST | TXM | мсм | FSM | F0 | DLB | RES |     |

|------|------|---------|-----------|------|------|-----|-----|------|------|-----|-----|-----|----|-----|-----|-----|

| 0    | 0    | 0       | 0         | 0    | 0    | 0   | 0   | 0    | 0    | 1   | 1   | 1   | 0  | 0   | 0   | Bin |

|      |      | 0       |           | 0    |      |     | 3   |      |      |     | 8   |     |    |     | Hex |     |

Figure 5. Transmit and receive operation in burst mode

Figure 6. Burst mode operation at maximum packet frequency

occurs, the program execution is directed to a transmit interrupt service routine, XINT-ISR, or a receive interrupt service routine, RINT-ISR. Within those ISRs, the CPU can execute serial port supporting tasks while a data transfer over the serial interface is still in progress.

For example, an XINT-ISR is often used to reload DXR after the old DXR content is copied into XSR. This ensures that the next DXR-to-XSR copy happens as soon as XSR is empty and a second data transmit can follow immediately. However, as will be shown in the next secton, when interfacing to sequentially operating ADCs, XINT needs to be disabled. A RINT-ISR is used to read the data receive register, DRR, and to save the content into data memory. When interfacing to on-the-fly converters, the RINT-ISR can also include the initiation of the next data transfer to maximize the data throughput.

A specific case of the burst mode is the operation at maximum packet frequency, shown in Figure 6.

At maximum packet frequency, the data bits in consecutive packets are transmitted contiguously with no inactivity between bits. This is achieved by reloading DXR during the first XINT-ISR. A second instruction disables XINT for all further data frames. A XINT-ISR executing these two instructions takes approximately five CLKX cycles to complete. With the rising edge of the 16th CLKX cycle, the last transmit bit is shifted out of XSR, and the latest DXR content is copied into XSR. At this time a new frame sync pulse, which overlaps the last transmit bit of the previous frame, is generated to start a new data transfer.

With the 16th falling edge of CLKX, half a clock cycle later, the last receive bit is clocked into the RSR. The subsequent RSR-to-DRR copy generates a receive interrupt. During the following RINT-ISR, the CPU reloads the transmit data register, DXR. It then reads the receive data register, DRR, and saves its content into data memory. While the CPU is executing the RINT-ISR, the serial port continues to transfer data. From now on, only one interrupt

service routine, the RINT-ISR, is used to save the receive data into memory, as well as to initiate all further data transfers. Care must be taken when adding further instructions to the RINT-ISR. Since the data stream needs to be contiguous, the length of the ISR must not exceed 15 CLKX cycles.

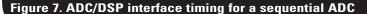

#### **Interfacing to sequential ADCs**

The sequential A-to-D converters in Table 1 operate in two phases. In phase 1, the ADC simultaneously receives configuration data from the DSP and transmits conversion results to the DSP. During this data transfer, the ADC is configured for the desired operation mode and starts sampling the analog input channel. Phase 2 represents the actual analog-to-digital conversion, followed by an interrupt signal once a conversion is complete. The advantage of the sequential operation is that the sampling period can be extended by a factor of 2 without affecting the conversion time. This is particularly useful for sampling high-impedance input sources. A long sampling time allows the ADC internal switched capacitors to be charged longer, thus helping the analog input signal sampled to settle within a 0.5-LSB accuracy.

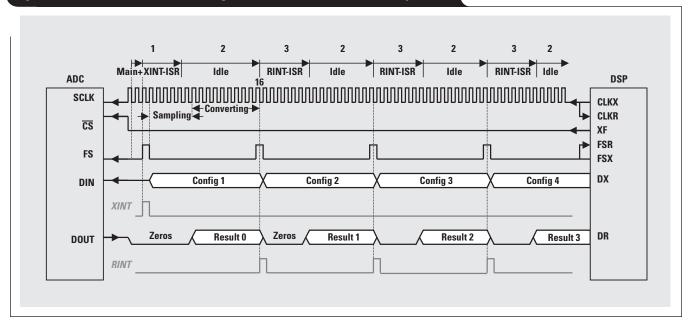

Figure 7 shows the timing diagram of the TLV2544 ADC in single-shot mode. Because a conversion needs to be completed before another one can be started, a contiguous flow of data bits is not possible, which is true for all sequentially operating ADCs.

Note that most ADCs provide a programmable EOC/INT pin to signal the end of a conversion. The following discussion assumes that the EOC/INT pin is programmed to use the /INT pulse to indicate the end of a conversion. The two gray-shaded signals, EOC and RINT, serve demonstration purposes only.

EOC presents the internal conversion time of the A-to-D converter, while RINT demonstrates the occurrence of the DSP internal receive interrupt.

The data acquisition process starts with the DSP providing the data clock, SCLK, for the serial interface. The DSP then activates the ADC by applying a logic low via the external flag output, XF, to the /CS input of the A-to-D converter. With the falling edge of /CS, the data output of the ADC leaves the high-impedance state and provides a random logic value at DOUT.

After the ADC is enabled, each data transfer is executed by the following five steps:

- 1. In the main routine, the DSP initiates a data transfer by writing ADC configuration data into the DXR of the serial port. On the second rising edge of SCLK following the DXR-write, a frame sync pulse, FS, is generated.

- 2. With the falling edge of FS, the serial port transmits configuration data to the ADC via DIN. The first four bits represent the actual configuration data, while the remaining 12 bits are ignored by the ADC. Simultaneously the ADC transmits the conversion results via DOUT to the DSP. To comply to the 16-bit frame format, the results of a 10-bit converter is followed by six zero bits. A 12-bit conversion result requires only four trailing zeros.

- 3. With the 16th falling edge of SCLK, the DX output, and with it DIN, goes into high-impedance, while DOUT stays low till the next data transfer. The A-to-D converter starts the conversion process and the generated receive interrupt of the serial port leads the CPU to enter the RINT-ISR. During this interrupt routine, the

- CPU reads the receive data from the serial port and saves it into data memory.

- 4. Upon the completion of the RINT-ISR the CPU idles until an unmasked interrupt occurs. The ADC completes the conversion and provides an interrupt pulse via its /INT output to one of the DSP external interrupt inputs, /INT1 /INT3.

- 5. The CPU now enters the INTx-ISR, reloading the DXR with ADC configuration data (i.e., the channel number). The new DXR-write initiates the next data transfer sequence, and Steps 1–4 are repeated until all samples have been acquired.

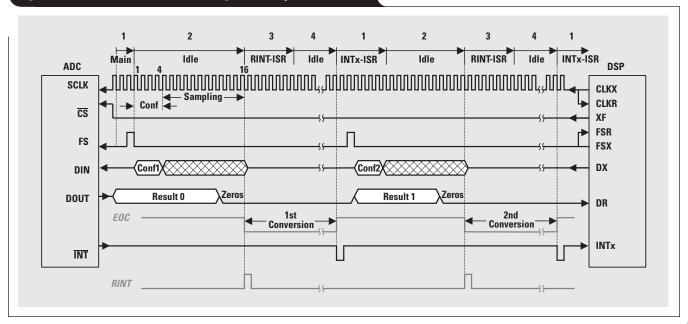

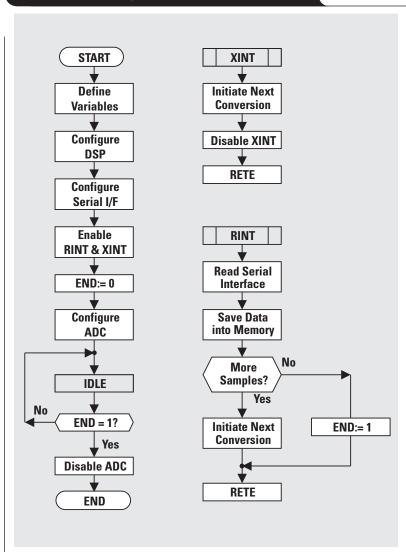

Figure 8 shows the basic program flow that supports the above interface timing.

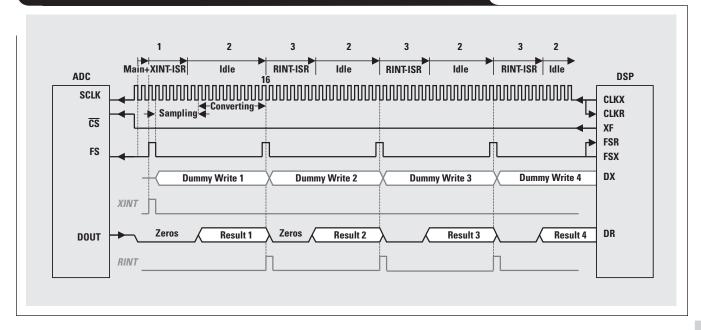

#### Interfacing to "on-the-fly" ADCs

These converters perform the analog-to-digital conversion at the same time they transfer data to the DSP. A data acquisition, including device configuration and data conversion, is completed within the 16 data clock cycles, thus allowing the stream of data bits to be contiguous. On-the-fly converters usually provide a sample rate of 1–4 MSPS. Figure 9 shows the timing diagram of the multi-channel, on-the-fly A-to-D converter, TLV1570.

After the DSP has activated the ADC by taking /CS low, the data transfer is executed by the following three steps:

1. In the main routine, the DSP writes ADC configuration data into the DXR of the serial port and generates an FS-pulse as well as a transmit interrupt, XINT. The serial port executes the first transfer of data by sending a

Figure 8. Interface program for sequential ADCs

#### **Main routine**

The main routine starts with defining the following variables:

- the number of samples to be acquired,

- the memory start address for the acquired data, and

- the ADC configuration words such as the conversion mode, the sampling mode, and the channel numbers.

The DSP configuration disables all interrupts, specifies the wait-states to zero, and defines the program memory range for the data acquisition program. Then the serial port is configured for burst mode operation and on-chip data clock and frame-sync generation.

The two interrupts, RINT and INTx, are enabled, and the END-flag, which determines the end of the data acquisition program, is set to zero.

To configure the A-to-D converter, the DSP takes the XF-output low and enables the ADC via the /CS- input. The CPU loads the DXR with ADC configuration data, causing the first data transfer to start. Then the CPU is set into idle mode, waiting for interrupts to occur.

Once an ISR has been completed, the CPU checks for program completion. As long as the END-flag is zero, the CPU returns to idle mode. If the END-flag is one, the DSP disables the ADC by taking XF high, thus completing the main routine.

#### RINT-ISR

During the RINT-ISR the CPU reads the receive data in the serial port, saves the data into memory, and returns to the main routine.

#### INTx-ISF

The INT-ISR initiates all further data transfers. As long as more samples are to be acquired, the CPU continuously reloads the DXR to start a new conversion.

Once all samples have been acquired, the END-flag is set to one and program control returns to the main routine.

- 16-bit configuration word to the ADC. In receive, the ADC provides 16-bit output data, consisting of four preceding zeros and a 12-bit conversion result.

Meanwhile the XINT-ISR reloads DXR and disables XINT for all further data frames.

- 2. While the data transfer continues, the CPU idles, waiting for a receive interrupt to occur.

- 3. With the rising edge of the 16th SCLK cycle, a new FSpulse starts the next data frame. Upon the falling edge of the 16th SCLK cycle, a RINT is generated that forces the CPU to leave the idle mode and enter the

receive interrupt service routine. Within the RINT-ISR, the CPU reads the DRR and saves the received data into memory. It then writes a new configuration word into DXR to prepare for the next data frame. After completing the RINT-ISR, the CPU returns to idle mode. Then Steps 2 and 3 are repeated until all samples have been acquired.

Figure 10 shows the timing diagram of the 12-bit, single-channel ADC, TLV1572. The interface timing is similar to that of the TLV1570, except that the output data of the

Figure 9. ADC/DSP interface timing for a multi-channel on-the-fly ADC

Figure 10. ADC/DSP interface timing for a single-channel, on-the-fly ADC

TLV1572 represent the results of the current conversion, while the output data of the TLV1570 are the results of the conversion executed in the previous data frame.

The TLV1572 is not configurable and therefore provides no DIN terminal. The DSP still needs to perform a dummy write of the DXR (i.e., with random data) to generate the required FS-pulse, which indicates the start of a data frame and triggers the A-to-D conversion.

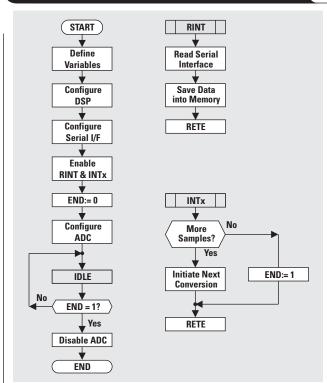

Figure 11 shows the basic program flow that supports the above interface timing.

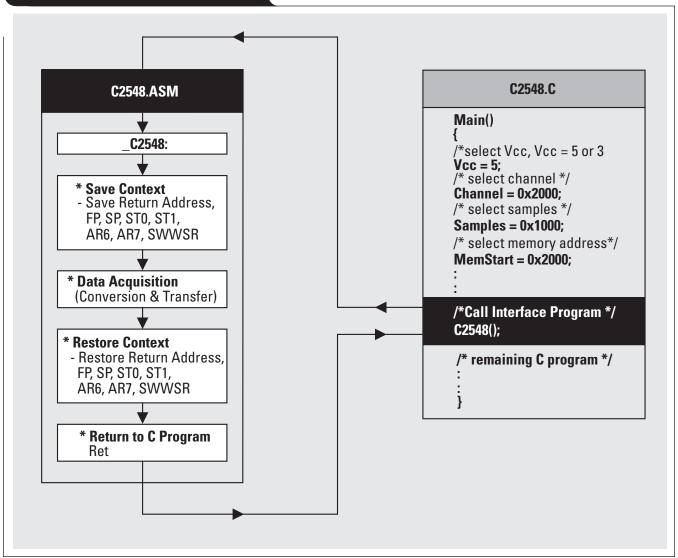

#### **C-callable interface routines**

The previous flowcharts describe the structure of the interface routines written in assembler. These assembler routines are used to investigate and to optimize the interface timing between newly released data converters and DSPs. However, with the majority of DSP programmers

using C rather than assembler, TI's application team for analog products has made its assembler routines C-callable.

Figure 12 gives an example of a C-callable assembler routine for the 8-channel, 12-bit ADC, TLV2548.

In addition, the assembler routine received a savecontext and a restore-context task.

- Save-context saves all pointers and registers, such as frame-pointer, stack-pointer, status and auxiliary registers, which have been used previously in the C-program.

- Restore-context restores the original content of these registers before returning to the C-program.

After the variable definition in C, a call instruction starts the assembler routine. All previously used registers are saved, and the actual data acquisition begins. Once the user-defined number of samples has been received, all pointers and registers are restored. The CPU exits the assembler routine and returns to the C-program. Using C-callable interface relieves the programmer from the tedious task of studying device-specific assembler code.

Figure 11. Interface program for on-the-fly ADCs

#### Main routine

The main routine is almost the same as the one in Figure 8, except that the internal transmit interrupt, XINT, is used instead of the external interrupt, INTx.

The main routine starts with defining the number of samples to be acquired, the memory start address for the acquired data, and the ADC configuration words. In the case of a non-configurable device, there are no configuration words. Instead, any random code can be written to DXR to start a data transfer.

The main routine continues with configuring the DSP and the serial port.

Then the two serial port interrupts, RINT and XINT, are enabled, and the END-flag is set to zero.

To configure the ADC, the DSP takes the XF-output low and enables the device via the /CS- input. The CPU writes configuration data to DXR. The following data transfer configures the ADC, while the CPU goes into idle mode, waiting for interrupts to occur.

Once an ISR has been completed, the CPU checks for program completion. Depending on the status of END, the CPU either returns to idle mode or disables the ADC and completes the main routine.

#### XINT-ISR

With the start of the first data frame, a XINT is generated. The CPU enters the XINT-ISR and reloads DXR to ensure an immediate start of the second frame, once the first transfer is completed and XSR is empty.

Then the CPU disables XINT for all further transfers.

#### **RINT-ISR**

This RINT-ISR is the sum of the previous RINT- and INTx-ISRs for sequential converters. The CPU reads the receive data and saves it into memory.

As long as more samples are to be acquired, the CPU continuously reloads the DXR to start a new conversion. Once all samples have been acquired, the END-flag is set to one and program control returns to the main routine.

Figure 12. C-callable interface program

#### References

For more information related to this article, visit the TI Web site at www.ti.com/ and look for the following materials by entering the TI literature number into the quick-search box.

| <b>Document Title</b>                     | TI Lit. # |

|-------------------------------------------|-----------|

| 1. Analog Applications (August 1999)      | SLYT005   |

| 2. Characteristics, Operation, and Use of |           |

| the TLV157XEVM                            | SLAU025   |

| 3. Interfacing the TLV1572 ADC to the     |           |

| TMS320C203 DSP                            | SLAA026B  |

| 4. TLV1570 EVM User's Guide               | SLAU024   |

| 5. TLV1572 EVM User's Guide               | SLAU018   |

| 6. Choosing an ADC and Op Amp for         |           |

| Minimum Offset                            | SLAA064   |

| 7. | Interfacing the TLV 1544 ADC to the |             |

|----|-------------------------------------|-------------|

|    | TMS320C203 DSP                      | . SLAA 028A |

| 8. | Interfacing the TLV1544 ADC to the  |             |

|    | TMS320C50 DSP                       | . SLAA 025A |

| 9. | Switched-capacitor ADC Analog Input |             |

|    | Calculations                        | .SLAA036    |

#### **Related Web sites**

Get product data sheets at:

www.ti.com/sc/docs/products/analog/device.html Replace device with tlc2554, tlc2558, tlv1544, tlv1548, tlv1570, tlv1572, tlv2544, or tlv2548

www.ti.com/sc/docs/products/dsp/tms320c50.html

## The operation of the SAR-ADC based on charge redistribution

#### By Thomas Kugelstadt

Application Manager

Figure 1. Five-bit SAR-ADC based on charge redistribution

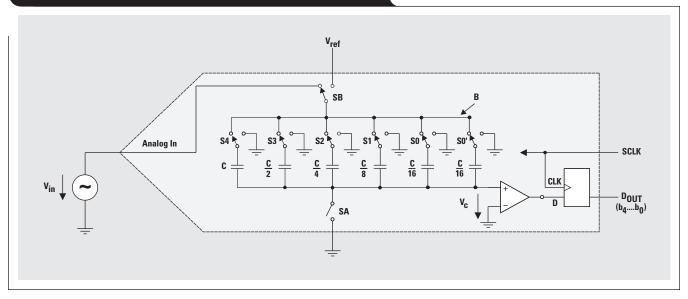

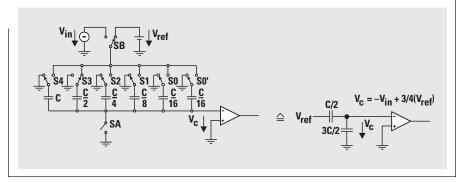

All Texas Instruments TLV- and TLC-series sequential serial analog-to-digital converters perform successive approximation based on charge redistribution. This article explains the operation of the SAR (successive approximation register)-ADC (analog-to-digital converter). It provides a concise description of a model SAR-ADC based on charge redistribution. Figure 1 shows the simplified circuit of a 5-bit charge redistribution converter using switched capacitor architecture.

All capacitors have binary weighted values, i.e., C, C/2,  $C/4,....C/2^{n-1}$ . The last two capacitors having the value

C/2<sup>n-1</sup> are connected so that the total capacitance of the n+1 capacitors is 2C. MOS-transistors are used to implement the required n+3 switches, and the voltage comparator provides the appropriate steering of the switches via auxiliary logic circuitry. The conversion process is performed in three steps: the sample mode, the hold mode, and the redistribution mode (in which the actual conversion is performed).

#### Sample mode

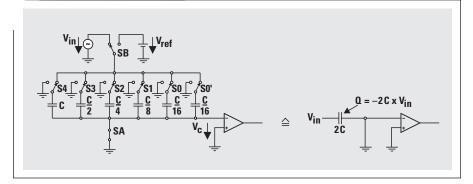

In the sampling mode (Figure 2), switch SA is closed and SB is switched to the input voltage  $V_{in}$ . The remaining switches are turned to the common bus B. Due to charging, a total charge of  $Q_{in} = -2 \text{C x } V_{in}$  is stored on the lower plates of the capacitors.

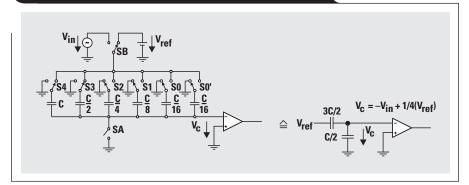

#### Hold mode

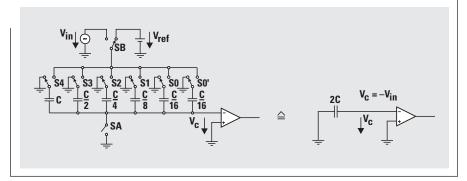

During the hold mode (Figure 3), switch SA is opened while the switches S4....SO' are connected to ground,

Figure 2. Sample mode

thereby applying a voltage of  $V_{c}=-V_{\rm in}$  to the comparator input. This means that the circuit already has a built-in sample-and-hold element.

#### Redistribution mode

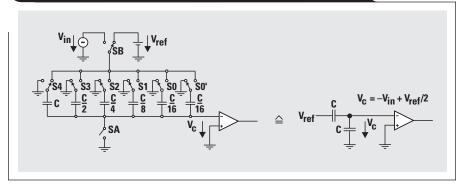

The actual conversion is performed by the redistribution mode. The first conversion step, shown in Figure 4, connects C (the largest capacitor) via switch S4 to the reference voltage V<sub>ref</sub>, which corresponds to the full-scale range (FSR) of the ADC.

Capacitor C forms a 1:1 capacitance divider with the remaining capacitors connected to ground. The comparator input voltage becomes  $V_C = -V_{in} + V_{ref}/2$ . If  $V_{in} > V_{ref}/2$ , then  $V_C < 0$ , and the comparator output goes high, providing the most significant bit MSB (bit 4) = 1. On the other hand, if  $V_{in} < V_{ref}/2$ , then  $V_C > 0$ , and bit 4 = 0.

The second conversion step connects C/2 to  $V_{ref}$ . If the first conversion step resulted in bit 4=1, switch S4 is turned to ground again to discharge C as shown in Figure 5; otherwise it remains connected to  $V_{ref}$  if bit 4=0 (Figure 6), resulting in a comparator input voltage  $V_c = V_{in} + \text{bit } 4 - V_{ref}/2 + V_{ref}/4$ .

According to this voltage, the next most significant bit (bit 3) is obtained by comparing  $V_{in}$  to 1/4  $V_{ref}$  or 3/4  $V_{ref}$  through the different voltage dividers. Switch S3 is then either turned to ground if bit 3 = 1, thereby discharging C/2, or S3 remains connected to  $V_{ref}$  if bit 3 = 0.

This process continues until all bits are generated, with the final conversion step being performed at a comparator input voltage of  $V_C = -V_{in} + \text{bit } 4 \times V_{ref}/2 + \text{bit } 3 \times V_{ref}/4 + \text{bit } 2 \times V_{ref}/8 + \text{bit } 1 \times V_{ref}/16 + \text{bit } 0 \times V_{ref}/32.$

#### **Related Web site**

www.ti.com/sc/docs/products/msp/dataconv/index.htm

#### Figure 3. Hold mode

Figure 4. Conversion Step 1 determines the MSB (bit 4)

Figure 5. If bit 4 = 1,  $V_{in}$  is compared with 3/4  $V_{ref}$

Figure 6. If bit 4 = 0,  $V_{in}$  is compared with 1/4  $V_{ref}$

## Power supply solutions for TI DSPs using synchronous buck converters

#### By Bang S. Lee

Application Specialist, Power Management

#### Introduction

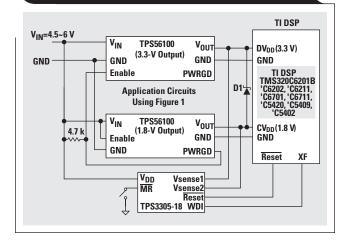

This article describes simple power solutions for TI's TMS320C6000 and TMS320VC54xx DSP applications using synchronous buck converter controllers such as the TPS56100, TPS5210, TPS56xx, and TPS5602. DSP power solutions from a single-input-only system (5-V or 12-V), a dual-input system (5-V and 12-V), and a wide-input voltage system (4.5-V  $\sim$  25-V) are presented.

## Review of DSP power requirements and synchronous buck converter controllers

The TI DSP families ('C6000 and 'C54xx) require separate core and I/O power. Table 1 summarizes the voltage supply for the current 'C6000 and 'C54xx families.

TI DSPs do not require specific power sequencing between the core supply and the I/O supply; however, systems should be designed to insure that neither supply is powered up for extended periods of time if the other supply is below the proper operating voltage. Excessive exposure to these conditions can adversely affect the long-term reliability of the device. System-level concerns such as bus contention may require supply sequencing to be implemented. In this case, the core supply should be powered up at the same time as, or prior to (and powered down after), the I/O buffers.

TI's synchronous buck converter controllers (TPS56100, TPS5210, TPS56xx, and TPS5602) are specifically designed to provide excellent transient response and high efficiency for the microprocessor power applications such as the 'C6000 and 'C54xx families from TI, as well as similar digital loads. In addition, the hysteresis control method is used so that power-supply designers do not have to worry

Table 1. Summary of DSP 'C6000 and 'VC54xx power requirements

| TI DSP                               | CORE<br>VOLTAGE<br>(V) | I/O<br>VOLTAGE<br>(V) |

|--------------------------------------|------------------------|-----------------------|

| TMS320C6201/'C6202/'C6211            | 1.8                    | 3.3                   |

| TMS320C6202B/'C6203/'C6204/'C6205    | 1.5                    | 3.3                   |

| TMS320C6701/'C6711                   | 1.8                    | 3.3                   |

| TMS320VC5402/'VC5409/'VC5420/'VC5421 | 1.8                    | 3.3                   |

| TMS320VC549/'VC5410                  | 2.5                    | 3.3                   |

| TMS320VC5416/'VC5441                 | 1.5                    | 3.3                   |

about the stability and compensation issues. Table 2 summarizes the controller characteristics.

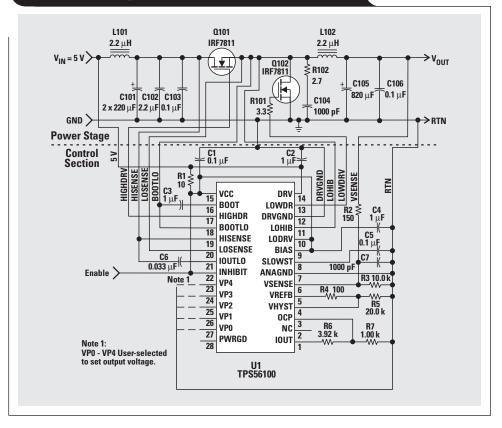

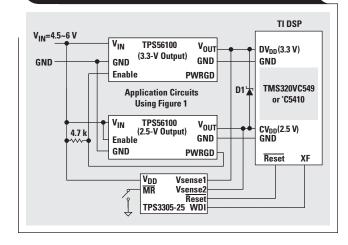

## Solution 1—single-input voltage application $(V_{in} = 5 \text{ V})$

The TPS56100, a synchronous buck switch-mode power-supply controller, provides an accurate programmable supply voltage suitable for 5-V input-only microprocessor power applications. The reference voltage, ranging from 1.3 V to 2.6 V, is determined by the voltage programming (VP) pins. The output voltage can be set equal to the reference voltage using VP, or it can be extended to some multiple of the reference voltage using the sampling resistors (R2, R3) (see Figure 1). The TPS56100 also includes an inhibit input to control power sequencing and undervoltage lockout, thereby insuring the 5-V supply is within limits before the controller starts.

Table 2. Summary of the TI synchronous buck converter controller characteristics

|          | V <sub>in</sub> RANGE<br>(POWER STAGE)<br>(V) | V <sub>CC</sub> RANGE<br>(CONTROLLER)<br>(V) | V <sub>out</sub> RANGE<br>(POWER STAGE)<br>(V) | I <sub>out</sub> *<br>(POWER STAGE)<br>(A) | DRIVER CURRENT<br>(CONTROLLER)<br>(A) | OTHERS     |

|----------|-----------------------------------------------|----------------------------------------------|------------------------------------------------|--------------------------------------------|---------------------------------------|------------|

| TPS56100 | 5                                             | 5                                            | 1.3 to 2.6                                     | 7                                          | 2                                     | 1 channel  |

| TPS5210  | 4.5 ~ 12                                      | 12                                           | 1.3 to 3.5                                     | 8                                          | 2                                     | 1 channel  |

| TPS56xx  | 5                                             | 12                                           | 1.5, 1.8, 2.5, or 3.3                          | 8                                          | 2                                     | 1 channel  |

| TPS5602  | 4.5 ~ 25                                      | 4.5 ~ 25                                     | Adjustable                                     | 4/channel                                  | 1.2 at V <sub>0</sub> = 3 V           | 2 channels |

<sup>\*</sup>The current capability can be extended in multi-phase configuration or if the switching devices are added in parallel; see Table 2 in TI TPS56100/5210 datasheets.

Figure 1 shows the typical application circuit using the TPS56100, which features an accurate programmable stepdown DC-DC converter. The VP pins and the two external resistors (R2, R3) determine a programmable output voltage from 1.3~V to approximately 5~V. The output voltage,  $V_O$ , is set with the following equation:

$$V_{o} = \left(1 + \frac{R2}{R3}\right) V_{ref}$$

(1)

Figures 2 and 3 show power solutions using the TPS56100, suitable for 5-V-only systems. The application circuit for 1.5-V core and 3.3-V I/O supply voltage is identical with the figures except for the core voltage supply (1.5 V) and SVS. To avoid bus contention issues within a DSP system, the recommended start-up sequencing is met by using PWRGD (power good signal) pins as shown in the figures. The PWRGD connected to the Enable pin of the other power supply provides the start-up sequencing (core voltage first, then peripheral voltage). After approximately 10 ms —set by

C5, R4, and R5 (see Figure 1)— the voltage on the PWRGD pin goes high, and the other TPS56100 is brought up.

The Schottky diode D1 provides a measure of protection during the power-down sequence and during other

Figure 1. A 5-V input-only application circuit using the TPS56100 (7-A output)

periods when the DV<sub>DD</sub> supply is below the CV<sub>DD</sub> supply by limiting the CV<sub>DD</sub> - DV<sub>DD</sub> voltage to the forward drop of D1. If CV<sub>DD</sub> fails, the PWRGD pin of the power supply shuts down the other supply.

Figure 2. TMS320C6000/'VC5420/'VC5409/

'VC5402 power-supply solution using

TPS56100 for a 5-V input-only system

Figure 3. TMS320VC549/'VC5410 powersupply solution using TPS56100 for a 5-V input-only system

Table 3. Summary of setting values for TPS56100 1.5-/1.8-/2.5-/3.3-V outputs

| OUTPUT<br>VOLTAGE | <b>R2</b> | R3  | C7   | VP TERMINALS (0 = GND, 1 = FLOATING OR PULL-UP TO 5 V) |     |     |     |     | V <sub>ref</sub>   |

|-------------------|-----------|-----|------|--------------------------------------------------------|-----|-----|-----|-----|--------------------|

| (V)               | (Ω)       | (Ω) | (pF) | VP4                                                    | VP3 | VP2 | VP1 | VP0 | (V <sub>dc</sub> ) |

| 3.3               | 1K        | 1K  | 100  | 0                                                      | 1   | 0   | 0   | 0   | 1.65               |

| 2.5               | 100       | 20K | 1000 | 1                                                      | 1   | 0   | 1   | 0   | 2.50               |

| 1.8               | 100       | 20K | 1000 | 0                                                      | 0   | 1   | 0   | 1   | 1.80               |

| 1.5               | 100       | 20K | 1000 | 0                                                      | 1   | 0   | 1   | 1   | 1.50               |

Table 3 shows the setting values of TPS56100 to generate the output voltages 1.5 V, 1.8 V, 2.5 V, or 3.3 V. To obtain the 3.3-V output, set the reference voltage to 1.65 V and replace R2 and R3 with 1-k $\Omega$  resistors. For the 1.5-V, 1.8-V, and 2.5-V output voltages, the reference voltage represents the output voltage.

Two EVMs (evaluation modules)—SLVP128 (7-A output) and SLVP133 (3-A output)—are available to provide a convenient method for evaluating the performance of the TPS56100. A completed and tested power supply is included in each EVM.

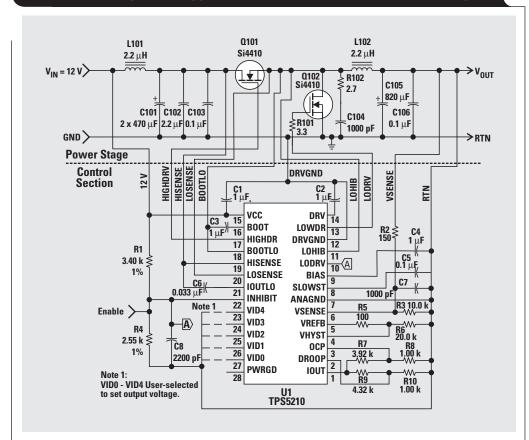

## Solution 2—single-input voltage application $(V_{in} = 12 \text{ V})$

The TPS5210 is suitable for single 12-V input-only system applications. The reference voltage, ranging from 1.3 V to

3.5 V, is determined by the voltage identification code (VID) pins. The output voltage can be set equal to the reference voltage using VID or can be extended to some multiple of the reference voltage using the external sampling resistors (R2, R3). The TPS5210 also includes an inhibit input to control power sequencing.

Figure 4 shows the typical application schematic using the TPS5210, which features a fast step-down DC-DC converter.

The VID pins and the two external resistors (R2, R3) determine a programmable output voltage from 1.3 V to approximately input supply voltage. The output voltage between 1.3 V and 3.5 V can be easily set by shorting the correct VID inputs to ground. Values above the maximum reference voltage (3.5 V) can be achieved by setting the reference voltage to any convenient voltage within its range and selecting values for R2 and R3 to give the correct output.

Figure 4. A 12-V input-only application circuit using the TPS5210 (8-A output)

Table 4. Summary of setting values for TPS5210 1.5-/1.8-/2.5-/3.3-V outputs

| OUTPUT<br>VOLTAGE |      | V <sub>ref</sub> |      |      |      |                    |

|-------------------|------|------------------|------|------|------|--------------------|

| (V)               | VID4 | VID3             | VID2 | VID1 | VID0 | (V <sub>dc</sub> ) |

| 3.3               | 1    | 0                | 0    | 1    | 0    | 3.30               |

| 2.5               | 1    | 1                | 0    | 1    | 0    | 2.50               |

| 1.8               | 0    | 0                | 1    | 0    | 1    | 1.80               |

| 1.5               | 0    | 1                | 0    | 1    | 1    | 1.50               |

The output voltage is obtained with the following equation:

$$V_{o} = \left(1 + \frac{R2}{R3}\right) V_{ref}$$

(2)

R2 and R3 can also be used to make small adjustments to the output voltage within the reference voltage range and/or to adjust for load-current active droop compensation. If there is no need to adjust the output voltage, R3 can be eliminated.

Table 4 shows the setting values of TPS5210 to generate the output voltages 1.5 V, 1.8 V, 2.5 V, or 3.3 V. The reference voltage represents the output voltage.

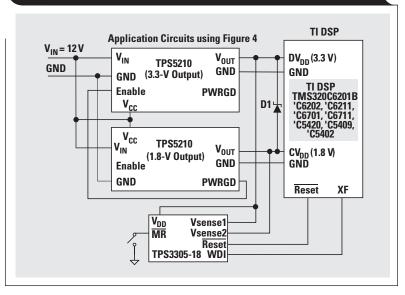

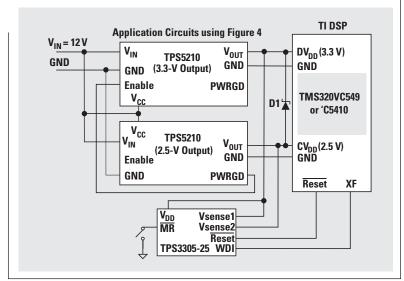

The power solutions for TMS320C6000 and TMS320VC54xx using TPS5210 are shown in Figures 5 and 6. As described in the previous section, the cross-connection between PWRGD (power good signal) and Enable provides the start-up sequencing. The application circuit for 1.5-V core and 3.3-V I/O supply voltage is identical with Figures 5 and 6 except for the core voltage supply (1.5 V) and SVS.

The two power supplies should be placed close to the DSP to minimize the trace resistance and inductance and to minimize the ground loop current between the two output grounds. This ground loop current can generate radiated EMI noise that can adversely affect any circuitry within the loop. The ground connection must be made directly on the DSP to help minimize the problem.

Figure 5. TMS320C6000/'VC5420/'VC5409/'VC5402 powersupply solution using TPS5210 for a 12-V input-only system

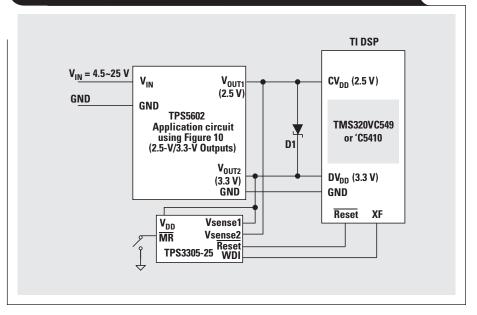

Figure 6. TMS320VC549/'VC5410 power-supply solution using TPS5210 for a 12-V input-only system

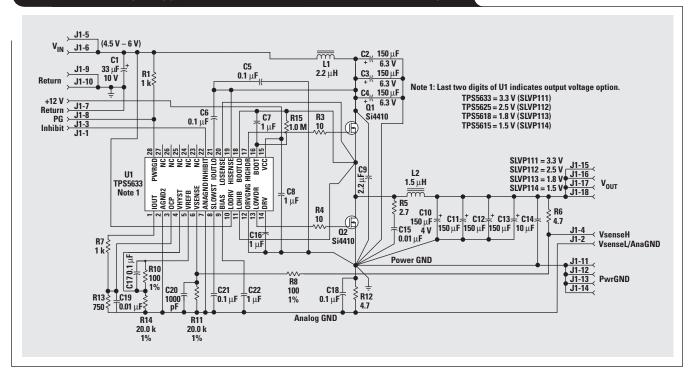

Figure 7. A dual-input application circuit using the TPS56xx (8-A output)

## Solution 3—dual-input voltage application ( $V_{in} = 5 \text{ V}$ and 12 V)

The TPS56xx, a synchronous buck switch-mode power-supply controller, is useful in applications with dual-input voltages and wide DC load ranges, such as multiple-DSP applications. Synchronous buck converters using the TPS56xx feature fixed output voltages of 3.3 V, 2.5 V, 1.8 V, or 1.5 V, providing an elegant power-supply solution for rapidly transitioning DSP loads, fast memory, and similar processors.

A hysteretic controller with user-selectable hysteresis is used to dramatically reduce overshoot and undershoot caused by load transients. The inhibit pin can be used to control power sequencing. Inhibit and undervoltage lockout assures that the 12-V supply voltage and system supply voltage (5 V) are within proper operating limits before the controller starts.

Figure 7 shows the typical application circuit using the TPS5633, which features an accurate 3.3-V output. The optional output voltages (1.5 V, 1.8 V, or 2.5 V) are obtained by replacing controller U<sub>1</sub> with TPS5615, TPS5618, or TPS5625 devices, since the power stage circuitry is identical.

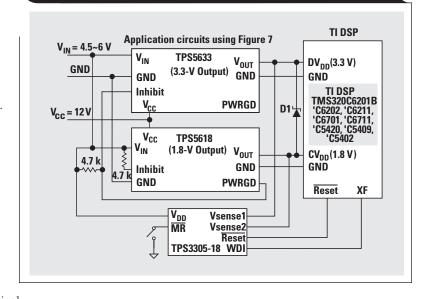

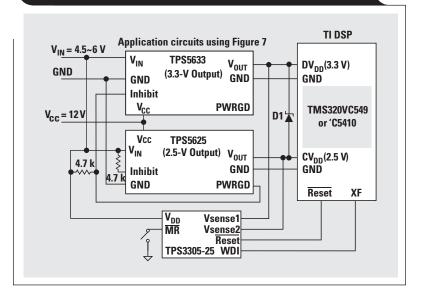

Power solutions using the TPS56xx for TI's DSP are shown in Figures 8 and 9. The application circuit for 1.5-V core and 3.3-V I/O supply voltage can be implemented as described in previous sections.

Figure 8. TMS320C6000/'VC5420/'VC5409/'VC5402 powersupply solution using the TPS5618 and TPS5633 for a dual-input system

The PWRGD connected to the inhibit pin of the other power supply provides the start-up sequencing (core voltage first, then peripheral voltage). After approximately 10 ms—set by C21, R10, and R14 (Figure 7)—the voltage on the PWRGD pin goes high, and the other TPS56xx is brought up.

Four EVMs—the SLVP111 (3.3 V), SLVP112 (2.5 V), SLVP113 (1.8 V), and SLVP114 (1.5 V)—are available to provide a convenient method for evaluating the performance of the TPS56xx. A completed and tested power supply is included in the EVM.

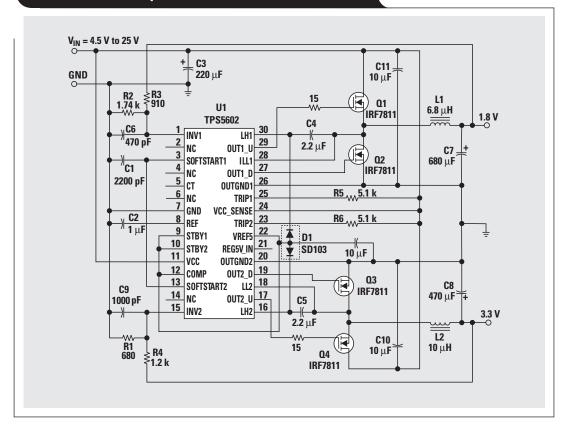

## Solution 4—single wide-input voltage application ( $V_{in} = 4.5 \sim 25 \text{ V}$ )

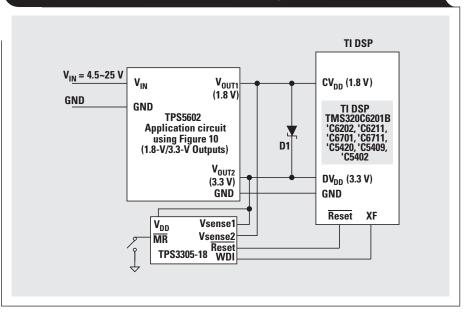

TI TPS5602, a dual-channel synchronous buck switch-mode power-supply controller, features very fast feedback control and dual channels and is designed specifically for DSP applications that require single wide-input applications. The up and down power sequencing can be easily achieved by setting the standby pins, since both channels are independent. The wide-input voltage and adjustable output voltage make the TPS5602 suitable for many applications.

Figure 10 shows a typical circuit design using the TPS5602 that features a dual-channel synchronous buck converter

Figure 9. TMS320VC549/'VC5410 power-supply solution using the TPS5625 and TPS5633 for a dual-input system (5 V and 12 V)

(1.8-V and 3.3-V outputs). The two output voltages are independent and can be adjustable (1.2-V to approximately input voltage) by using the sampling resistors such as R1,

Figure 10. A single wide-input application circuit using the TPS5602 (8-A output)

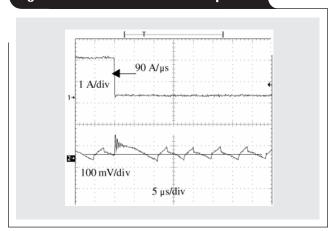

Figure 11. Fast load transient response

Table 5. Summary of setting values for TPS5602 1.5-/1.8-/2.5-/3.3-V outputs

| OUTPUT<br>VOLTAGE<br>(V) | R2 (or R1)<br>(Ω) | R3 (or R4)<br>(Ω) |

|--------------------------|-------------------|-------------------|

| 3.3                      | 680               | 1.2K              |

| 2.5                      | 1K                | 1.1K              |

| 1.8                      | 1.74K             | 910               |

| 1.5                      | 10K               | 2.67K             |

R2, R3, and R4. The output voltages, OUT1 and OUT2, are set with the following equations, where the reference voltage is 1.185 volts:

$$V_{OUT1} = \left(1 + \frac{R3}{R2}\right) V_{ref}$$

(3)

$$V_{OUT2} = \left(1 + \frac{R4}{R1}\right) V_{ref}$$

(4)

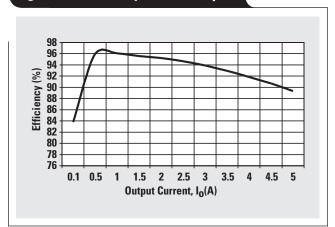

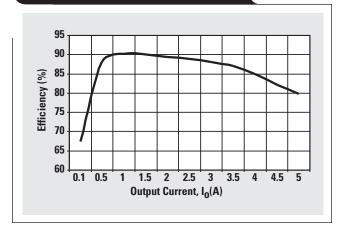

Figure 11 shows the TPS5602's transient response. The response is less than 2 microseconds after a load is applied. Conventional PWM buck converters exhibit approximately 100 microseconds of response. Figures 12 and 13 show the efficiency of the two controllers over load up to 5 A. Efficiency can be improved by choosing lower onresistance MOSFET.

Table 5 shows the setting values of TPS5602 to generate the output voltages  $1.5~\rm{V},\,1.8~\rm{V},\,2.5~\rm{V},\,or\,3.3~\rm{V}.$

The power solutions for TMS320C6000 and TMS320VC54xx using TPS5602 are shown in Figures 14 and 15. The application circuit for 1.5-V core and 3.3-V I/O supply voltage can be implemented as described in previous sections.

Figure 12. Efficiency of 3.3-V output

Figure 13. Efficiency of 1.8-V output

Figure 14. TMS320C6000/'VC5420/'VC5409/'VC5402 power-supply solution using TPS5602 for a single wide-input system (4.5 V  $\sim$  25 V)

By using the SOFTSTART1 and SOFTSTART2 pins in Figure 10, the start-up sequencing (core voltage first, then peripheral voltage) can be easily achieved. The SOFTSTART timing can be adjusted by selecting the SOFTSTART capacitor value such as C1 and C12 shown in Figure 10. The equation is

$$C_{\text{soft}}(\mu F) = 2 \times T_{\text{soft}}(ms),$$

(5)

where  $C_{soft}$  is the SOFTSTART capacitance and  $T_{soft}$  is the start-up time.

For example, to set the start-up time  $T_{soft}$  = 5 ms, the capacitance value of  $C_{soft}$  = 0.01  $\mu F$  is needed.

In addition, the TPS5602 has two external pins (STBY1, STBY2) that can be used alternatively for power-up sequencing.

#### References

For more information related to this article, visit the TI Web site at www.ti.com/ and look for the following materials by entering the TI literature number into the quick-search box.

| <b>Document Title</b>         | TI Lit. # |

|-------------------------------|-----------|

| 1. TPS3305 Application Report | SLVA056   |

| 2. TPS5210 Data Sheet         | SLVS243   |

| 3. TPS5210 User's Guide       | SLVU010,  |

|                               | SLVU011   |

| 4. TPS56xx Data Sheet         | SLVS177a  |

| 5. TPS56xx User's Guide       | SLVU007,  |

|                               | SLVU013   |

| 6. TPS5602 Data Sheet         | SLVS217   |

| 7. TPS56100 Data Sheet        | SLVS201a  |

| 8. TPS56100 User's Guide      | SLVU018   |

Figure 15. TMS320VC549/'VC5410 power-supply solution using the TPS5602 for a single wide-input system (4.5 V  $\sim$  25 V)

#### **Related Web sites**

Get product data sheets at:

**www.ti.com/sc/docs/products/analog/***device.***html** Replace *device* with tps3305-18, tps3305-25, tps5210, tps5211, tps5602, tps5615, tps5618, tps5625, tps5633, or tps56100

www.ti.com/sc/docs/products/dsp/c5000/index.htm www.ti.com/sc/docs/products/dsp/c6000/index.htm www.ti.com/sc/docs/products/dsp/tms320device.html Replace device with c6201, c6202, c6211, c6701, c6711, vc549, vc5402, vc5409, vc5410, or vc5420

## Powering Celeron-type microprocessors using TI's TPS5210 and TPS5211 controllers

**By Rais Miftakhutdinov,** System Engineering, Power Management Products, and Philip Rogers, System Engineering, Power Management Products

#### Introduction

Performance of desktop application microprocessors is improving rapidly, approaching the requirements that were typical for servers and workstations just a few years ago. In this high-performance PC, the voltage regulator has to supply the high current consumed by the microprocessor core to keep the core voltage within tight static and dynamic tolerances for minimum cost. The TPS5210EVM-147 (SLVP147) evaluation module has been designed and tested to confirm TI's TPS5210 and TPS5211 hysteretic controller performance to supply future Celeron™ microprocessors. The SLVP147 includes a synchronous DC-DC buck converter, high-frequency decoupling capacitors for PGA-370 microprocessor packages, and a load-current transient

tester. The DC-DC converter has 5-V input and 1.6-V output voltage and requires 12 V, 30 mA for the controller itself. It was designed as a low-cost solution in mother-board applications where small size is very important. The temperature of the components does not exceed 72°C at room ambient temperature with a load current of 14.5 A. The module has excellent transient characteristics at a peak load current of up to 18.4 A. A four-layer PCB had been used in the module to get electrical and temperature conditions close to actual conditions. The module meets electrical specifications of the Intel document "VRM 8.4 DC-DC Converter Design Guidelines" for >733-MHz clock and 133-MHz bus-frequency Celeron processors.

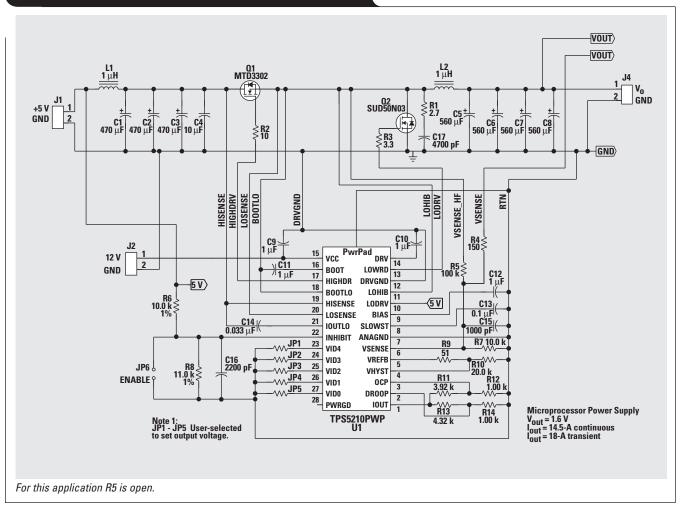

Figure 1. DC-DC synchronous buck converter schematic

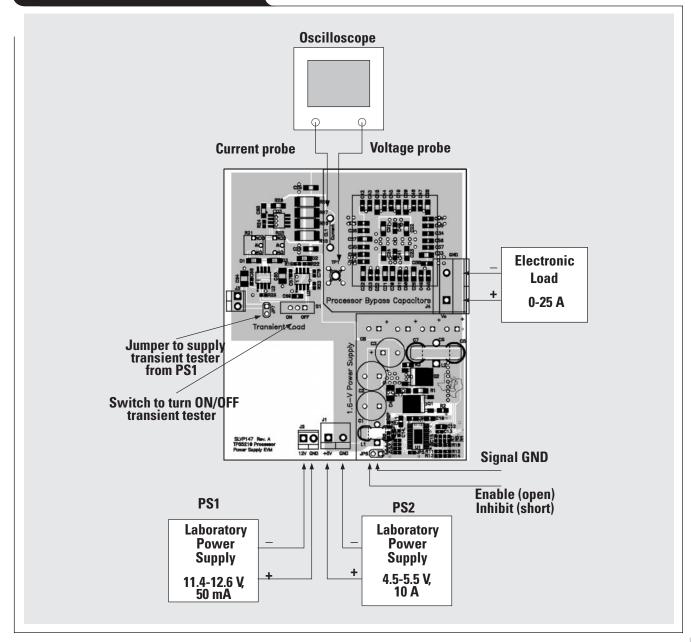

### Brief description of the SLVP147 evaluation module

Several evaluation modules for different desktop motherboard applications have been designed. The description and characteristics of one of them is presented in this report.

The SLVP147 evaluation module (4" x 3.25" x 0.8") includes three main parts:

- 1.6-V power supply (2" x 1.5" x 0.8"),

- Processor bypass capacitors, and

- Transient load.

The four-layer, 1-oz. FR-4 PCB board, which is typical for motherboards, had been used in the module to simulate

actual application conditions for an embedded point-ofload power supply.

#### 1.6-V power supply

The 1.6-V power supply is a DC-DC synchronous buck converter (see the schematic in Figure 1 and lower right corner of the evaluation module in Figure 2) that includes input and output filters, power stage, and control section.

The input voltage for the power section is 5 V  $\pm$  0.5 V, and the control section requires 12 V  $\pm$  0.6 V. All power-supply components are placed in the corner of the board to model the worst-case cooling conditions. Because of

Figure 2. Test setup for SLVP147 EVM

minimum size requirements, high-performance OS-CON-type capacitors have been selected for the input and output filters. The input filter includes three 10SP470M capacitors C1–C3, 10- $\mu$ F ceramic capacitor C4, and 1- $\mu$ H inductor L1. The input capacitors can handle a total maximum RMS current as high as 13.5 A. The output filter has four OS-CON-type capacitors (4SP560M) and a 1- $\mu$ H inductor, L2. The fast hysteretic controller and active droop reduce the number of capacitors while having a reliable margin for dynamic tolerance. The power stage includes power FETs in DPAK packages Q1, Q2, gate resistors R2 and R3, and snubber circuitry including resistor R1 and capacitor C17. The selection of a 10-M $\Omega$  MTD3302 high-side FET and a 7-M $\Omega$  SUD50N03-07 low-side FET is a compromise between cost and efficiency.

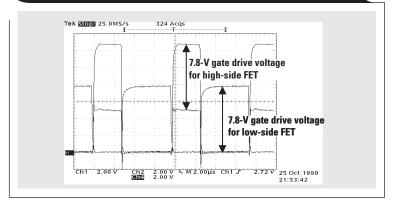

The controller section is based on the high-performance TPS5210 hysteretic controller and provides the following main functions:

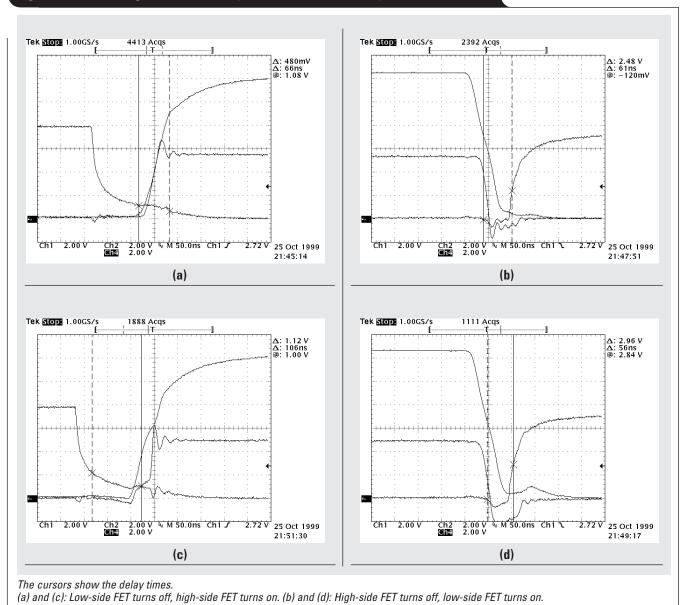

Adaptive dead-time-control high- and low-side drivers with an 8-V drive regulator and internal bootstrap diode

- to switch power FETs with minimum control and switching losses

- ullet A sample-hold circuit to sense the  $V_{ds}$  of the high-side FET for shutdown overcurrent protection and active droop compensation without expensive external current sensors

- A fast hysteresis comparator, which does not need feedback loop compensation circuitry that reacts to transients in 400–500 ns without restrictions on duty cycle (the hysteresis window is set by an external resistor as a percentage of the reference voltage)

- A 5-bit VID code, enable/inhibit signal input, power good signal, undervoltage lockout for both 12-V and 5-V inputs, and overvoltage shutdown

#### **Processor bypass capacitors**

The high-frequency decoupling capacitors (see the upper right corner of the evaluation module in Figure 2) occupy the same area as the cavity of the PG-370 package to model real-load current transient conditions. The decoupling circuitry includes 27 ceramic 0805 1-µF capacitors and 16 ceramic 4.7-µF capacitors in 1206 packages. Test point

Table 1. VRM 8.4 requirements and test data

| TEST | DESCRIPTION                                                                 | SPECIFICATION                                                                                               | DATA                                                                                                                                                                                    |  |  |  |  |  |

|------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

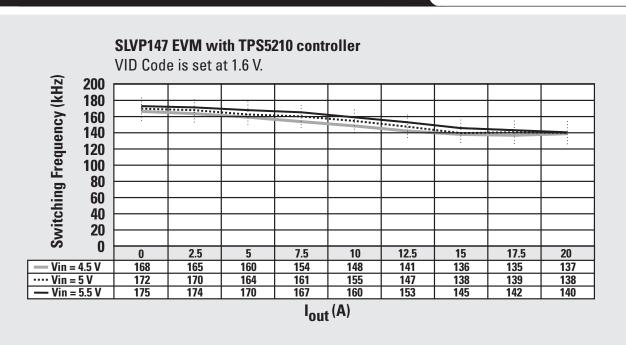

| 1    | Operating voltage and load current (VRM 8.4. sections 1.1 and 1.2)          | Input voltages 4.75 to 5.25 VDC and 11.40 to 12.6 VDC. Load current 0 to 18.4 A                             | Unit operates over the full input-voltage and load-<br>current range at switching frequency 135 to<br>175 kHz (Figure 7)                                                                |  |  |  |  |  |

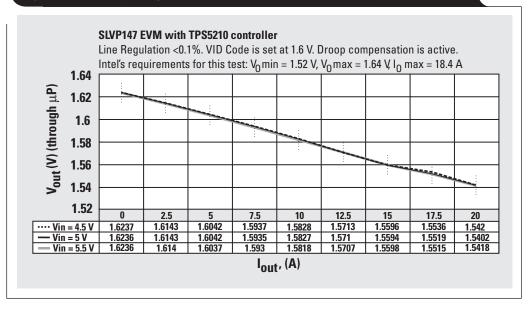

| 2    | Steady-state output voltage<br>(VRM 8.4. section 1.1)                       | Output voltage within 1.52 to 1.64 VDC                                                                      | Output voltage over the full input-voltage and load-<br>current range within 1.551 to 1.624 V including<br>droop compensation. Temperature regulation and<br>set point < 1% (Figure 3). |  |  |  |  |  |

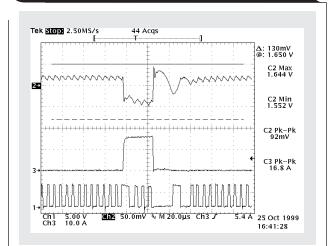

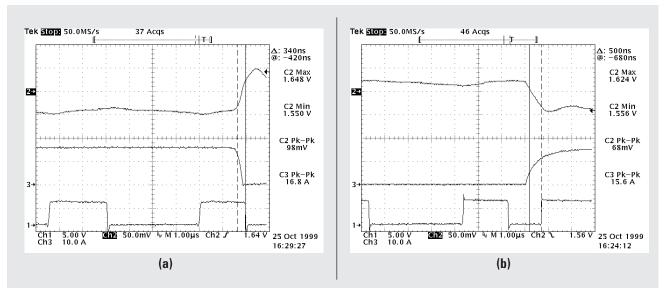

| 3    | Transient output voltage<br>(VRM 8.4. section 1.1)                          | Output voltage within 1.52 to 1.65 VDC at load-current steps in 0.8- to 18.4-A range with 20-A/µs slew rate | Output voltage within 1.552 to 1.644 V, response time < 500 ns, recovery time < 7 µs for step-up and < 34 µs for step-down (Figures 4 and 5)                                            |  |  |  |  |  |

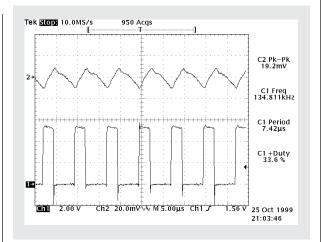

| 4    | Output ripple and noise<br>(VRM 8.4. section 1.1)                           | Included in steady-state output-voltage requirements. Measured with 20-MHz frequency band.                  | 20-mV peak-to-peak maximum (Figure 6)                                                                                                                                                   |  |  |  |  |  |

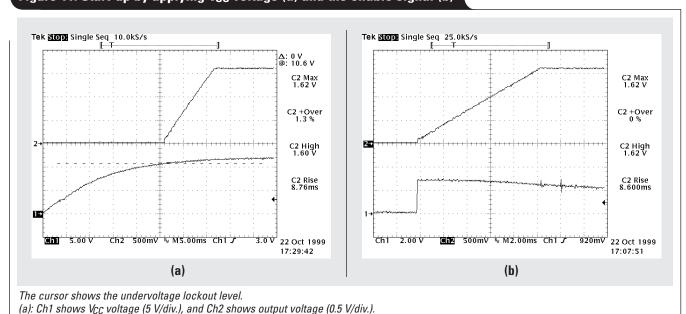

| 5    | Turn on overshoot<br>(VRM 8.4. section 1.1)                                 | < 10%, no load and full load                                                                                | < 1.3% at all load conditions (Figure 11)                                                                                                                                               |  |  |  |  |  |

| 6    | Turn on response time<br>(VRM 8.4. section 1.1)                             | < 10 ms                                                                                                     | < 9 ms (Figure 11)                                                                                                                                                                      |  |  |  |  |  |

| 7    | Power good signal<br>(VRM 8.4. section 1.1)                                 | High if the output voltage exceeds<br>±12% from nominal; otherwise low,<br>transition to high within 20 ms  | ±12% from nominal, guaranteed by controller design                                                                                                                                      |  |  |  |  |  |

| 8    | Output enable<br>(VRM 8.4. section 1.3)                                     | Open-collector input signal                                                                                 | Guaranteed by controller design (Figure 11)                                                                                                                                             |  |  |  |  |  |

| 9    | 5-bit VID (VRM 8.4. section 1.3)                                            | Input open-collector TTL signals                                                                            | Guaranteed by controller design, internal pull-up resistors                                                                                                                             |  |  |  |  |  |

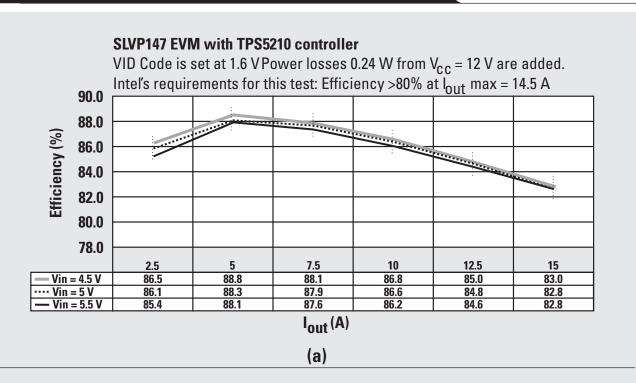

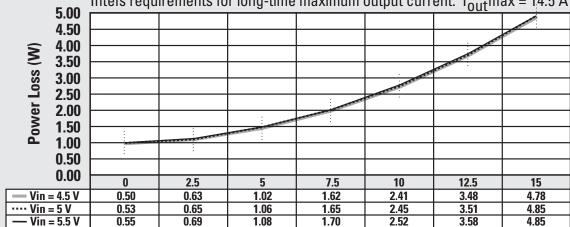

| 10   | Efficiency (VRM 8.4. section 1.4)                                           | > 80% at 14.5-A output current.<br>> 40% at 0.5-A output current.                                           | 83.5% at 15 A after 12 hours of operation (Figure 8)                                                                                                                                    |  |  |  |  |  |

| 11   | Overcurrent protection, output short circuit current (VRM 8.4. section 1.5) | Withstands a continuous short circuit of the output                                                         | Converter shuts down if the load current exceeds 22 A or shorts. Restarts by cycling V <sub>CC</sub> voltage.                                                                           |  |  |  |  |  |

| 12   | Overvoltage protection (VRM 8.4. section 1.5)                               | Latches output off if V <sub>out</sub> = 110 to 125% of nominal                                             | Internal overvoltage protection if V <sub>out</sub> = 112 to 120% of nominal                                                                                                            |  |  |  |  |  |

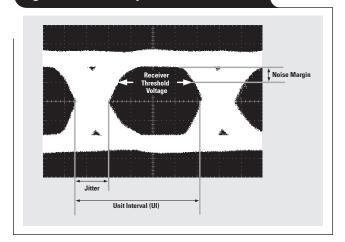

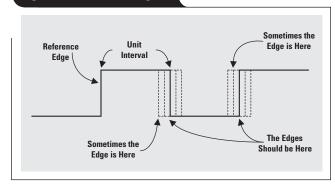

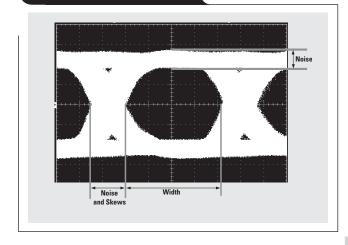

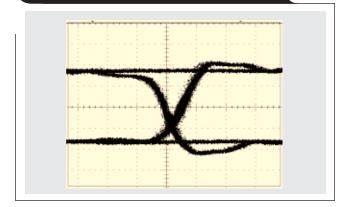

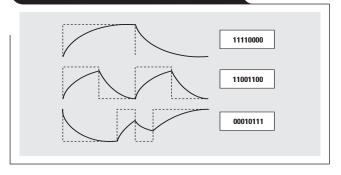

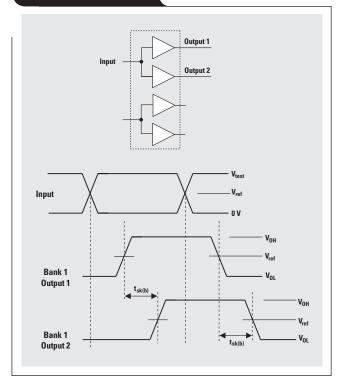

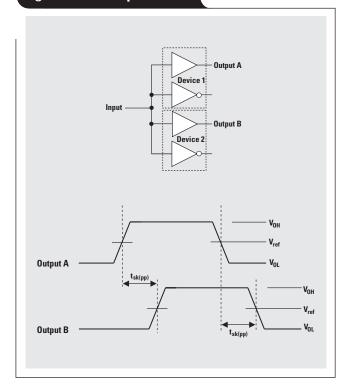

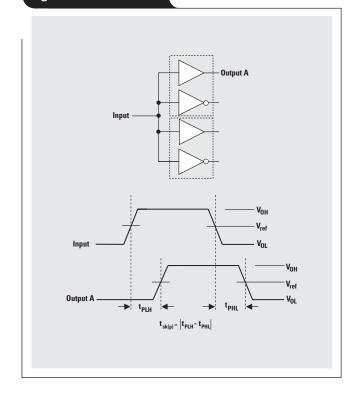

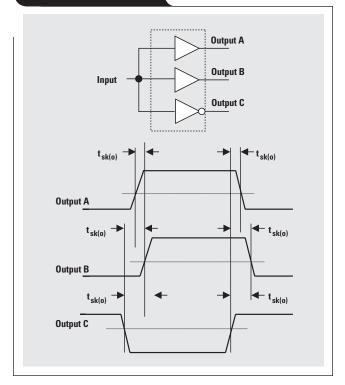

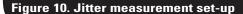

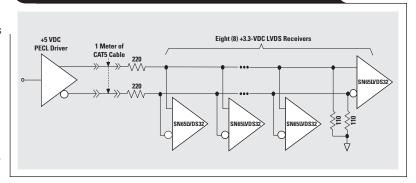

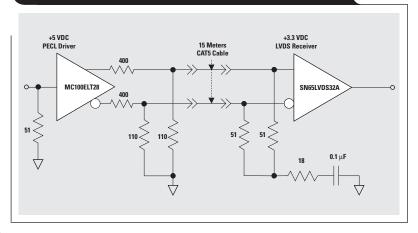

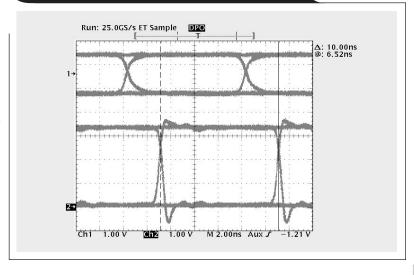

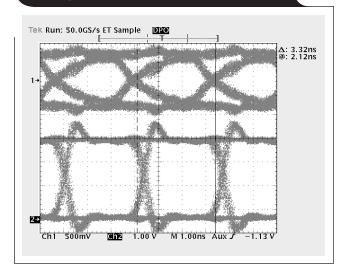

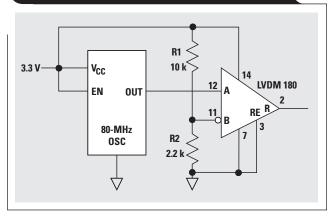

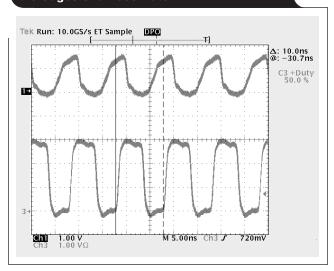

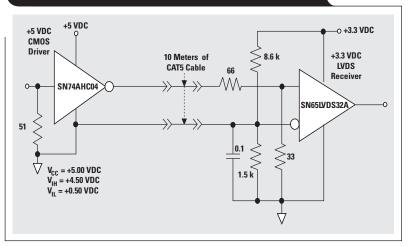

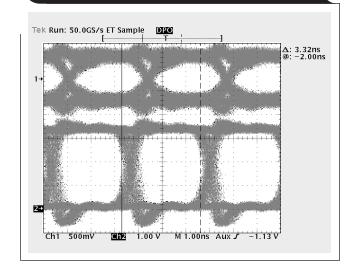

| 13   | Maximum component temperature                                               | FETs < 90°C at room temperature with natural cooling                                                        | FETs = 72°C, capacitors = 52°C, PCB = 47°C at room temperature of 22°C                                                                                                                  |  |  |  |  |  |