Personal Computer Circuit Design Tools

# **Power Specialist's App Note Book**

© copyright *intusoft* 1998 P.O.Box 710 San Pedro, Ca. 90733-0710 Tel. (310) 833-0710 Fax (310) 833-9658 web - www.intusoft.com email - info@intusoft.com

### POWER SPECIALIST'S APP NOTE BOOK Edited by Charles E. Hymowitz

#### Copyright

*intusoft*, 1998. All Rights Reserved. No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language, in any form, by any means, without written permission from *intusoft*.

Inquiries concerning reproduction outside those terms should be sent to the publishers at the following address:

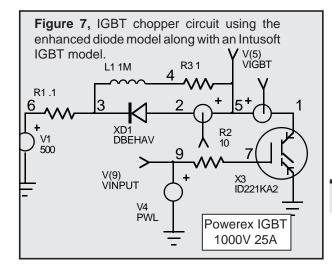

Intusoft P.O. Box 710 San Pedro, CA 90733-0710 USA

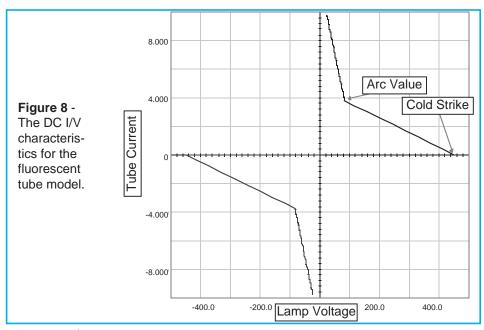

While the editor and the publishers believe that the information and the guidance given in this work is correct, all parties must rely upon their own skill and judgement when making use of it. Neither the editor nor the publishers assume any liability to anyone for any loss or damage caused by any error or omission in the work, whether such error or omission is the result of negligence or any other cause. Any and all such liability is disclaimed.

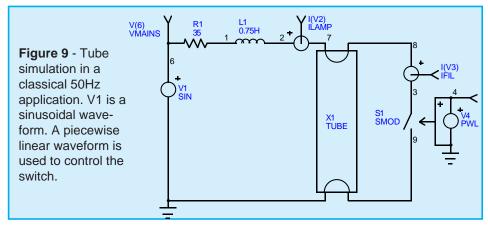

Macintosh is a registered trademark of Apple Computer, Inc. Epson is a registered trademark of Epson Inc. HP is a trademark of the Hewlett-Packard Corp. IBM is a registered trademark of International Business Machines Corporation. Intusoft, the Intusoft logo, ICAP, ICAPS, Design Validator, Test Designer, IsSpice4, SpiceNet, PreSpice, IntuScope, and IsEd are trademarks of Intusoft, Inc. All company/product names are trademarks/registered trademarks of their respective owners.

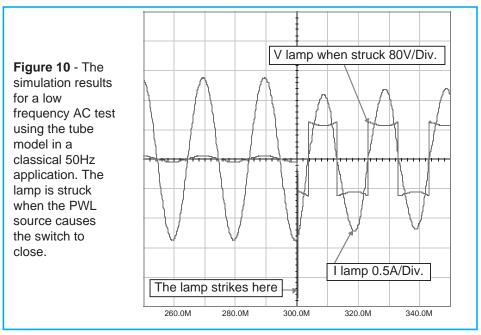

Printed in the U.S.A.

rev. 98/11

#### Acknowledgments

#### Authors

Christophe BASSO, consultant, Sinard, France

Charles Hymowitz, Intusoft, San Pedro, CA USA, charles@intusoft.com

Lawrence Meares, Intusoft, San Pedro, CA USA

Harry H. Dill, Deep Creek Technologies, Inc. Annapolis, MD USA, Testdesigner@compuserve.com

A. F. Petrie, Independent Consultant, 7 W. Lillian Ave., Arlington Heights, IL USA

Mike Penberth, Technology Sources, NewMarket Suffolk, U.K.

Martin O'Hara, Motorola Automotive and Industrial Electronics Group, Stotfold Hitchin Herts. U.K.

Kyle Bratton, Naval Aviation Depot, Cherry Point NC USA

Chris Sparr, Naval Aviation Depot, Cherry Point NC USA

Lloyd Pitzen, CCI Incorporated Arlington, VA USA

#### **Editors**

Charles Hymowitz Bill Halal

# Table Of Contents

| Switched Mode Power Supply Design                                                                                                                               |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Average simulations of FLYBACK converters with SPICE3                                                                                                           | 5   |

| A Tutorial Introduction to Simulating Current Mode Power Stages                                                                                                 | 17  |

| Write your own generic SPICE Power Supplies controller models                                                                                                   | 24  |

| Keep your Switch Mode Supply stable with a Critical-Mode Controller                                                                                             | 33  |

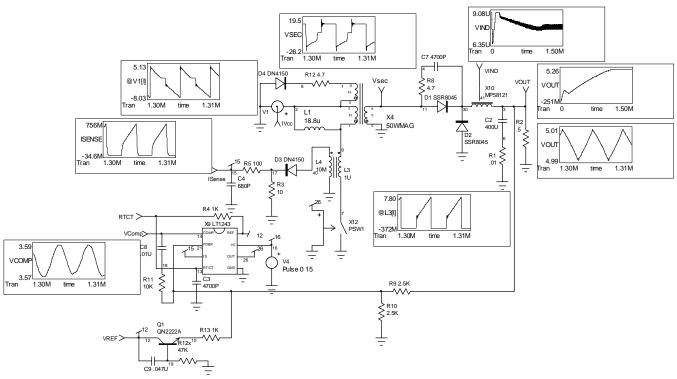

| Exploring SMPS Designs Using IsSpice                                                                                                                            | 40  |

| Average Models For Switching Converter Design                                                                                                                   | 48  |

| Simulating SMPS Designs                                                                                                                                         | 51  |

| SSDI Diode Rectifier Models                                                                                                                                     | 56  |

| High Efficiency Step-Down Converter                                                                                                                             | 57  |

| IsSpice4 Scripting Gives You More Power                                                                                                                         | 58  |

| Magnetics Design and Modeling                                                                                                                                   |     |

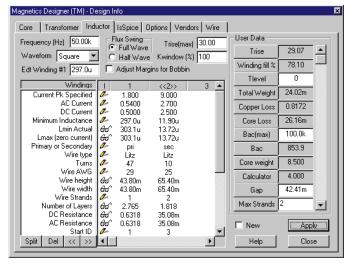

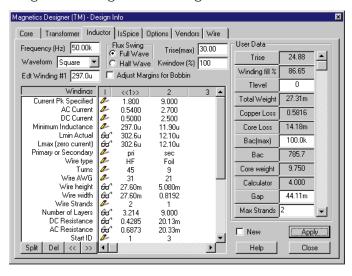

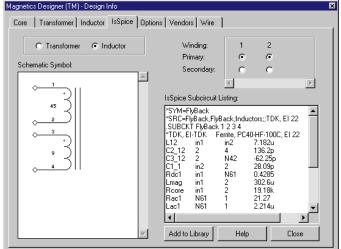

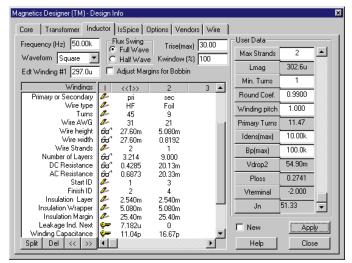

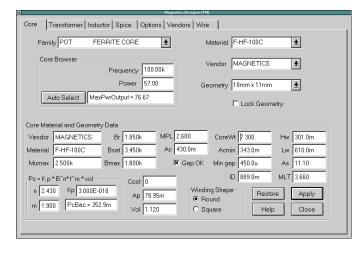

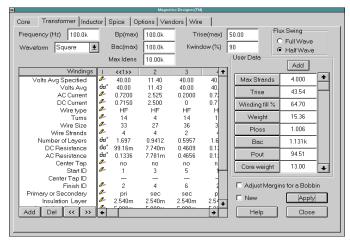

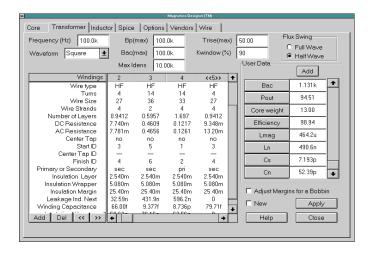

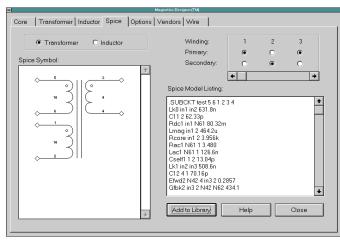

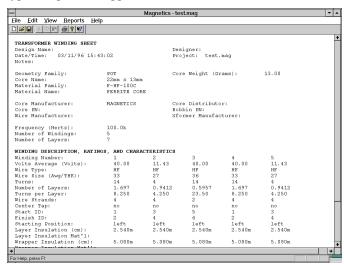

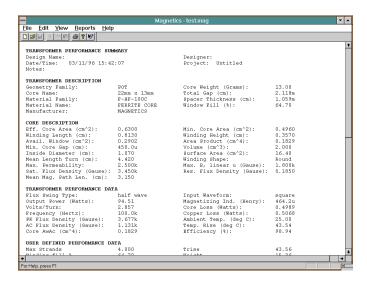

| Designing a 12.5W 50kHz Flyback Transformer                                                                                                                     | 62  |

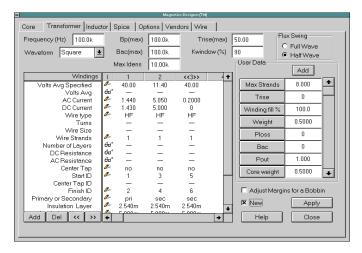

| Designing a 50W Forward Converter Transformer With Magnetics Designer                                                                                           | 65  |

| Signal Generators                                                                                                                                               |     |

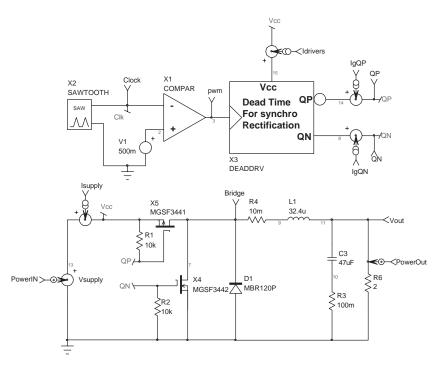

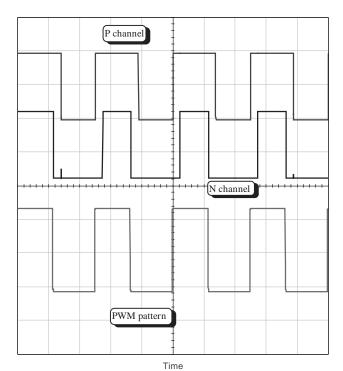

| IsSpice4 introduces a dead-time in your bridge simulations                                                                                                      | 72  |

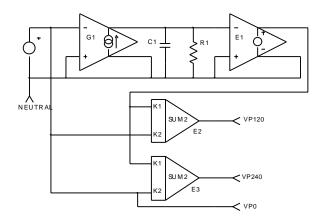

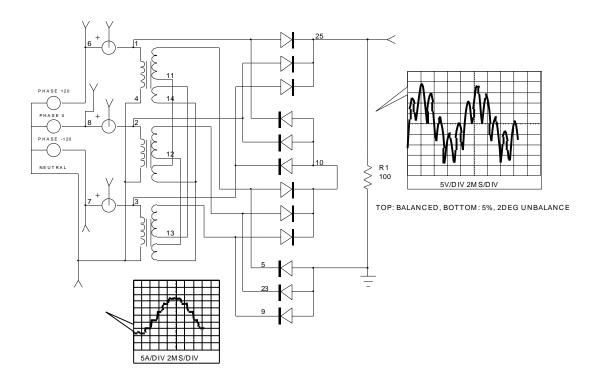

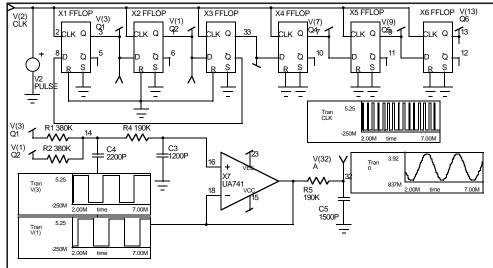

| Three Phase Generator                                                                                                                                           | 74  |

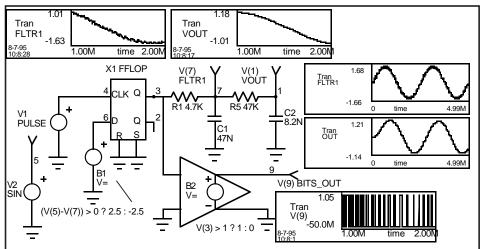

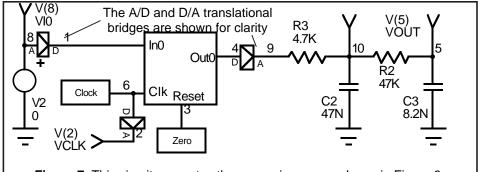

| Simulating Pulse Code Modulation                                                                                                                                | 76  |

| Modeling For Power Electronics                                                                                                                                  |     |

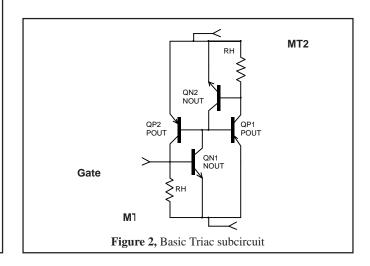

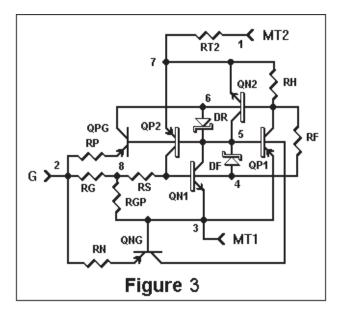

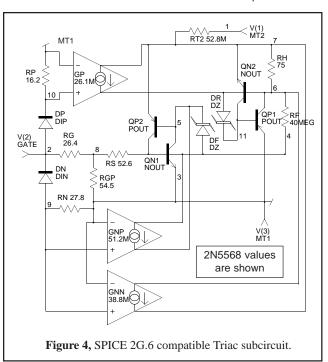

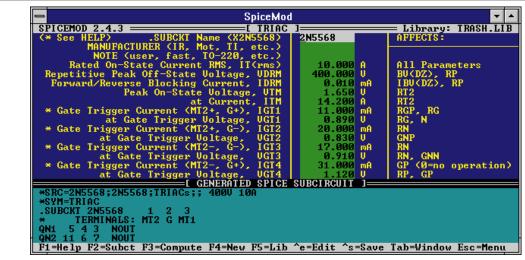

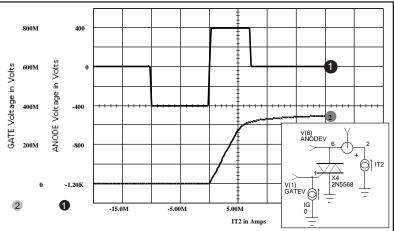

| A Spice Model For TRIACs                                                                                                                                        | 80  |

| A Spice Model For IGBTs                                                                                                                                         | 84  |

| SPICE 3 Models Constant Power Loads                                                                                                                             | 90  |

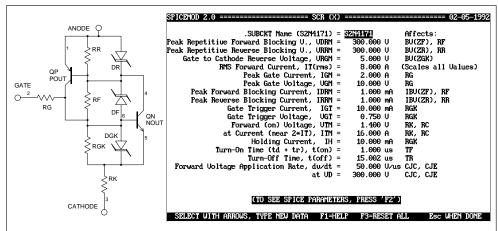

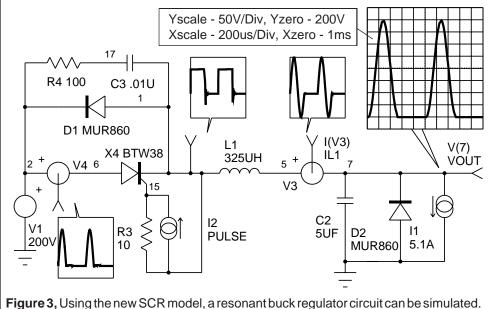

| Simulating Circuits With SCRs                                                                                                                                   | 91  |

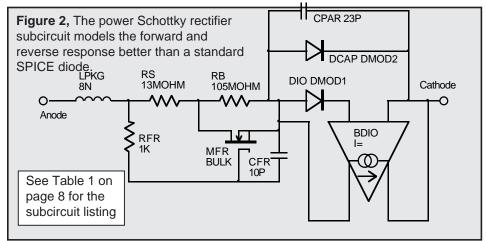

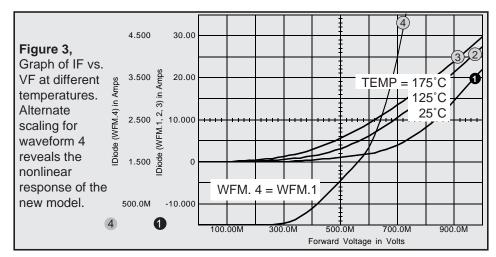

| Power Schottky and Soft Recovery Diodes                                                                                                                         | 96  |

| Spark Gap Modeling                                                                                                                                              | 103 |

| SPICE Simulates A Fluorescent Lamp                                                                                                                              | 108 |

| Sidactor Modeling                                                                                                                                               | 112 |

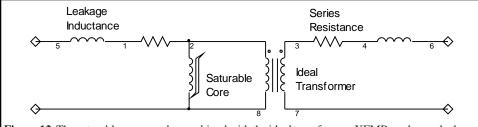

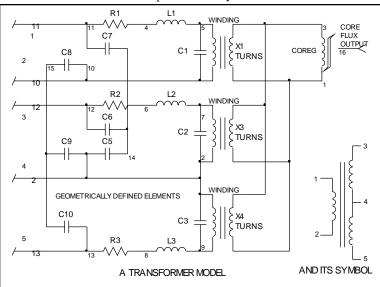

| Transformer and Saturable Core Modeling                                                                                                                         | 114 |

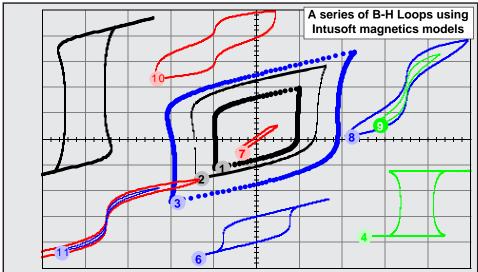

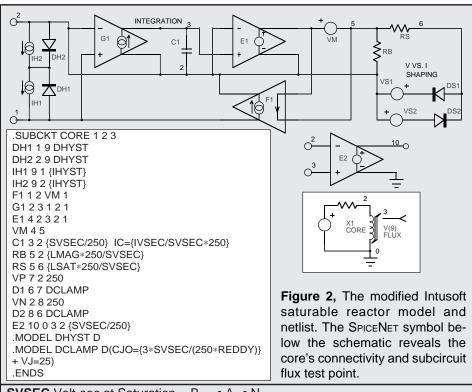

| Modeling Nonlinear Magnetics                                                                                                                                    | 120 |

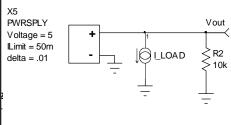

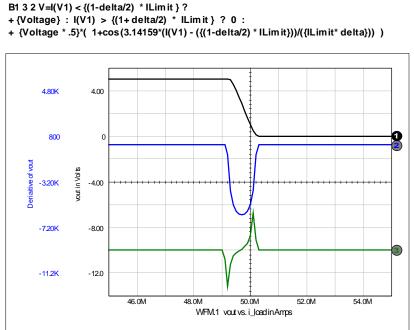

| Current Limited Power Supply                                                                                                                                    | 126 |

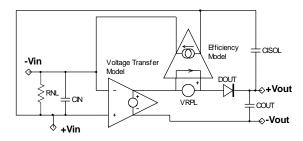

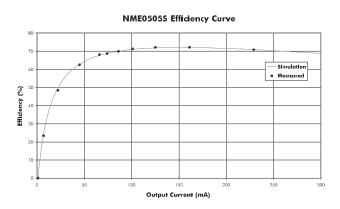

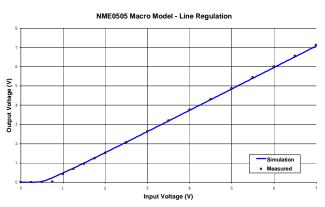

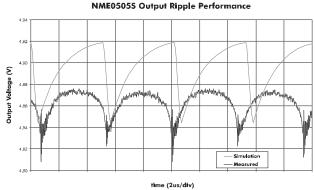

| Macro Modeling Low Power DC-DC Converters                                                                                                                       | 127 |

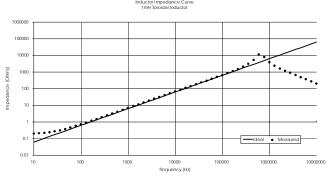

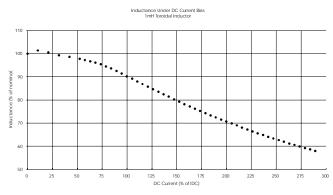

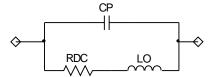

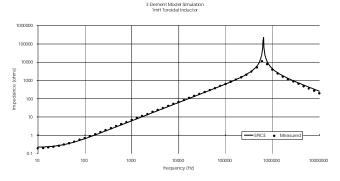

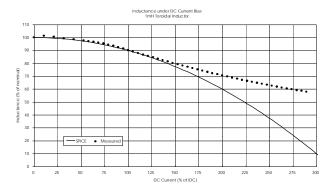

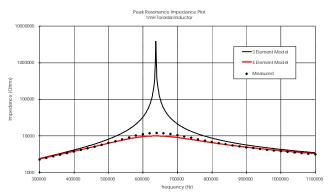

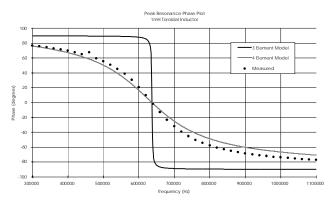

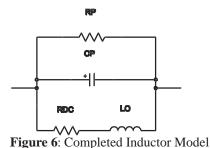

| Modeling Non-Ideal Inductors in SPICE                                                                                                                           | 131 |

| Motor and Relay Modeling                                                                                                                                        |     |

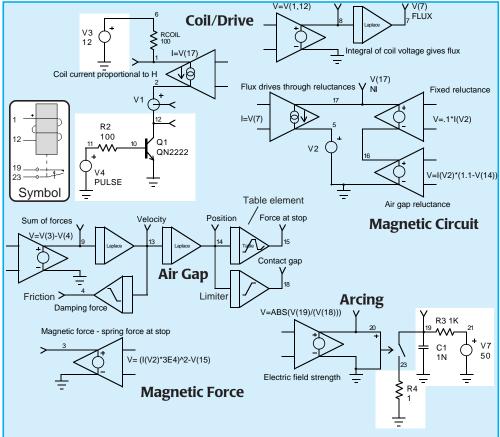

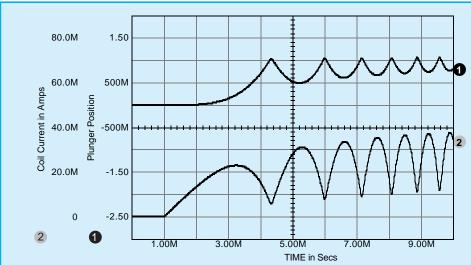

| Modeling A Relay                                                                                                                                                | 136 |

| New SPICE Features Aid Motor Simulation                                                                                                                         | 141 |

| Test Program Development and Failure Analysis for SMPS                                                                                                          |     |

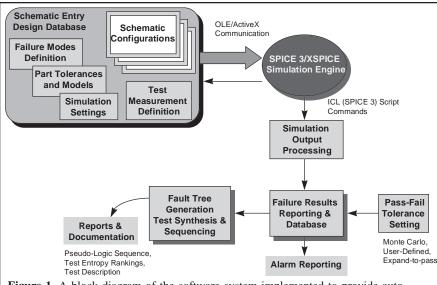

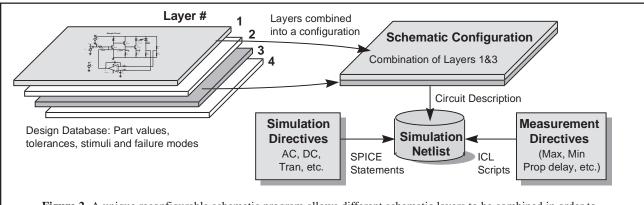

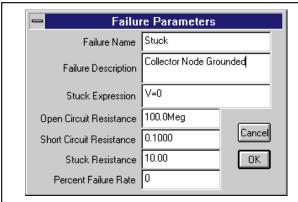

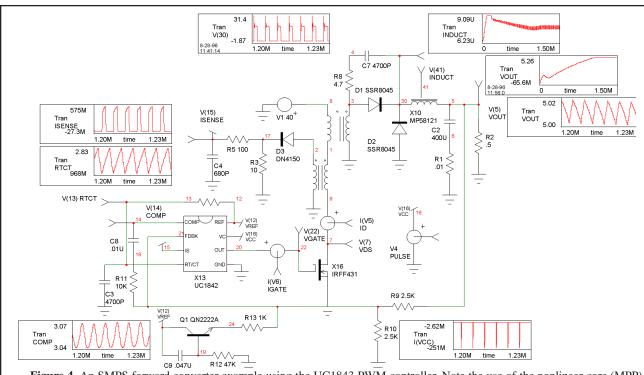

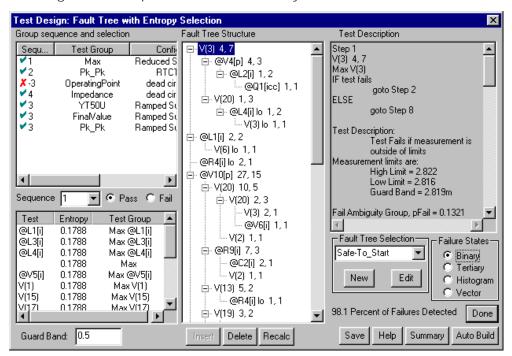

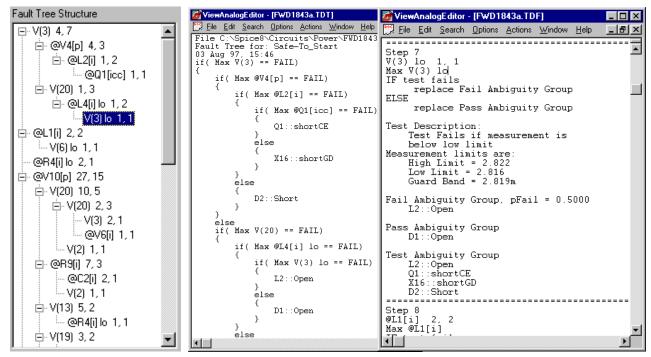

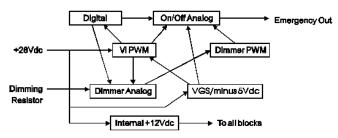

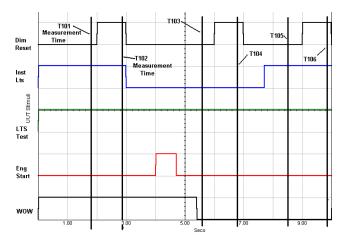

| Automating Analog Test Design                                                                                                                                   | 145 |

| Simulation measurements vs. Real world test equipment                                                                                                           | 150 |

| New Techniques for Fault Diagnosis and Isolation of Switched Mode Power Supplies<br>Application of Analog & Mixed Signal Simulation Techniques to the Synthesis | 152 |

| and Sequencing of Diagnostic Tests                                                                                                                              | 163 |

# Switched Mode Power Supply Design

#### **Authors**

Christophe BASSO, consultant, Sinard, France Charles Hymowitz, Intusoft Larry Meares, Intusoft Scott Frankel, Analytical Engineering Services Steve Sandler, Analytical Engineering Services

#### Average simulations of FLYBACK converters with SPICE3

Christophe BASSO May 1996

Within the wide family of Switch Mode Power Supplies (SMPS), the Flyback converter represents the preferred structure for use in small and medium power applications such as wall adapters, off-line battery chargers, fax machines, etc. The calculations involved in the design of a Flyback converter, especially one which operates in discontinuous mode, are not overly complex. However, the analysis of the impact of the environment upon the system may require a lengthy period of time: ESR variations due to temperature cycles, capacitor aging, load conditions, load and line transients, the effects of the filter stage, etc. must be considered.

A SPICE simulator can help the designer to quickly implement his designs and show how they react to real world constraints. The simulation market constantly releases SMPS models, and the designer can rapidly lose himself in the eclecticism of the offer. This article will show how you can benefit from these new investigation tools.

#### Simulating SMPS with SPICE is not a new topic

In 1976, R. D. Middlebrook settled the mathematical basis for modeling switching regulators [1]. Middlebrook showed how any boost, buck, or buck-boost converter may be described by a canonical model whose element values can be easily derived. In 1978, R. Keller was the first to apply the Middlebrook theory to a SPICE simulator [2]. At that time, the models developed by R. Keller required manual parameter computation in order to provide the simulator with key information such as the DC operating point. Also, the simulation was only valid for small signal variations and continuous conduction mode.

Two years later, Dr. Vincent Bello published a series of papers in which he introduced his SPICE models [3]. These models had the capacity to automatically calculate DC operating points, and allowed the simulated circuit to operate in both conduction modes, regardless of the analysis type (AC, DC or TRAN). Although these models are 15 years old, other models have been introduced since then, our example circuits which have been based upon them will demonstrate how well they still behave.

#### Switching or average models?

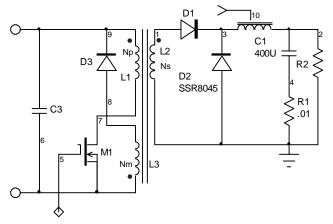

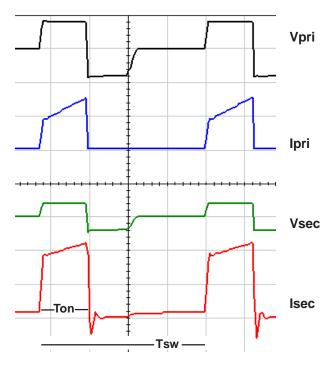

Switching models will exhibit the behavior of an electrical circuit exactly as if it were built on a breadboard with all of its nonlinearities. The semiconductor models, the transformer and its associated leakage elements, and the peripheral elements are normally included. In this case, the time variable **t** is of utmost importance since it controls the overall circuit operation and performance, including semiconductor losses and ringing spikes which are due to parasitic elements. Because SMPS circuits usually operate at high frequencies and have response times on the order of milliseconds, analysis times may be very long. Furthermore, it is

practically impossible to evaluate the AC transfer function of the simulated circuit due to the switch.

Average models do not contain the switching components. They contain a unique state equation which describes the average behavior of the system: in a switching system, a set of equations describe the circuit's electrical characteristics for the two stable positions of the switch/(es), ON or OFF. The "state-space-averaging" technique consists of smoothing the discontinuity associated with the transitions of the switch/(es) between these two states. The result is a set of continuous non-linear equations in which the state equation coefficients now depend upon the duty cycles  $\bf D$  and  $\bf D'$  (1-D). A linearization process will finally lead to a set of continuous linear equations. An in-depth description of these methods is contained in D. M. Mitchell's book, "DC-DC Switching Regulators Analysis", distributed by e/j BLOOM Associates.

#### The general simulation architecture

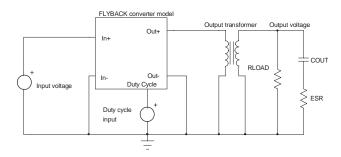

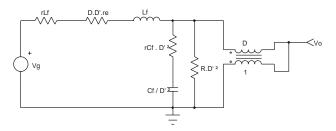

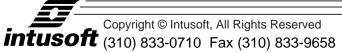

The key to understanding the simulation of SMPS with a SPICE simulator is to first experiment with very simple structures. Figure 1 shows the basic way to simulate an average voltage-mode Flyback converter with its associated components. As a starting point, simply draw a minimum part count schematic: simple resistive load, output capacitor with its ESR, perfect transformer (XFMR symbol), no input filter, no error amplifier etc.

Figure 1

By clicking on the average Flyback model symbol or simply filling in the netlist file, the working parameters will be entered, i.e. the operating switching frequency, the value of the primary power coil, etc. Some recent models require the loop propagation delays or overall efficiency. The parameters for the remaining components are obvious, except for the duty cycle input source. This source will directly pilot the duty cycle of the selected model. By varying the source from 0 to 1V, the corresponding duty cycle will sweep between 0 and 100%. For the first simulation, without an error amplifier, you will have to adjust this source such that the output matches the desired value. This value

corresponds to the DC operating point that SPICE needs for its calculations. The correct value can be determined incrementally or via the features in Intusoft's (San-Pedro, CA) IsSpice software. The Interactive Command Language (ICL), is a tremendously powerful language which has been primarily derived from the SPICE3 syntax and allows the designer to dynamically run SPICE commands without going back and forth from the schematic to the simulator. Below is a brief example of how the previous iteration process could be written:

while V(OUT)<=15 ; while the voltage at node OUT is less than or equal to 15V tran 1u 100u ;run a TRANSIENT analysis lasting 100us alter @Vduty[dc]=@Vduty[dc]+1mV ;increment the duty source by 1mV steps print mean(V(OUT)) mean(@Vduty[dc]) ;print the output and the duty source average values end

The SPICE simulator will compute the different values and refresh the output windows until the specified conditions are met. At this time, Vduty for the desired output value is known and can be reflected back to the schematic. In order to reduce execution time, and yield a more precise result, you could also run a DC sweep, although this method is less flexible.

**Simulation trick:** temporarily replace your large output capacitor with a small value in order to shorten the necessary transient time at every iteration. Small values require fewer switching cycles in order to reach the output target level.

#### The Pulse Width Modulator gain

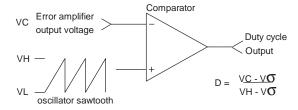

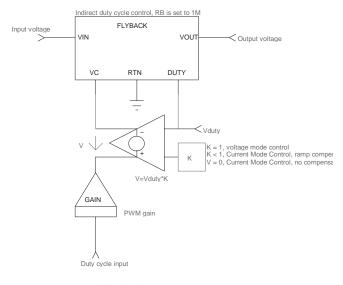

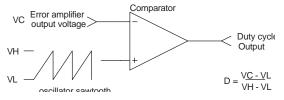

In a voltage-controlled Flyback SMPS, the conduction time of the primary switch depends upon the DC voltage that is compared with the oscillator sawtooth, as shown in Figure 2:

Figure 2

This circuit can be seen as a box which converts a DC voltage (the error amplifier voltage) into a duty cycle (D). The average models accept a 1 volt maximum duty cycle control voltage (D=100%). Generally, the IC's oscillator sawtooth can swing up to 3 or 4 volts, thus forcing the internal PWM stage to deliver the maximum duty cycle when the error amplifier reaches this value. To account for the 1 volt maximum input of our average models, the insertion of an

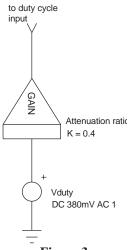

attenuator with  $1/(VH-V\sigma)$  ratio after the error amplifier output is mandatory. For example, if the sawtooth amplitude of the integrated circuit we use is 2.5Vp-p, then the ratio will be: 1/2.5=0.4. In our simulation schematic, to account for the previous sawtooth peak-to-peak value, we would have to restrict the maximum output value of the error amplifier to 2.5 volts and limit the lower value to greater than VL. Figure 3 updates the schematic of Figure 1.

Figure 3

#### Performing AC simulations

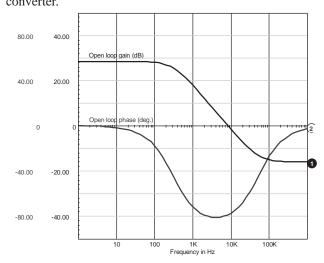

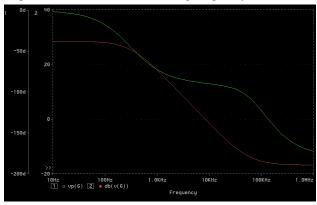

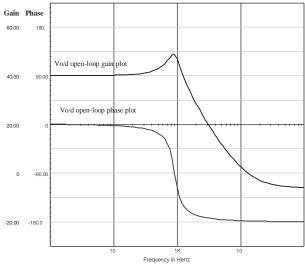

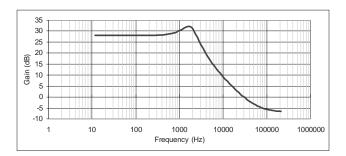

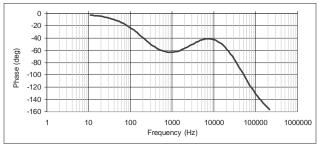

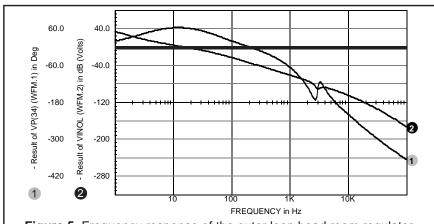

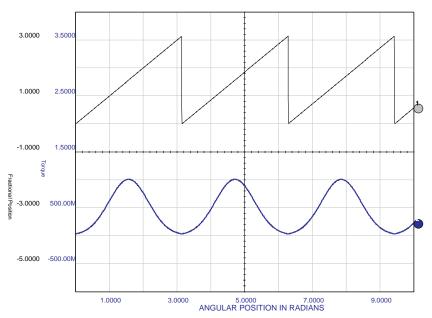

We now have a functional open-loop system with the correct DC output value. The purpose of the next stage will be to sweep the duty cycle source around its DC steady-state level. This will give us the open-loop AC response of the circuit. The Vduty source keeps its DC statement to provide SPICE with a DC point, but the AC 1 command is added. Monitoring the AC output voltage yields the graph of Figure 4, which shows the control to output transfer function for a discontinuous Flyback converter.

Figure 4

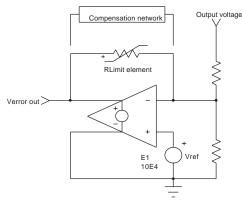

#### Adding the error amplifier

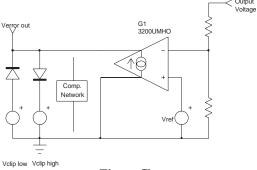

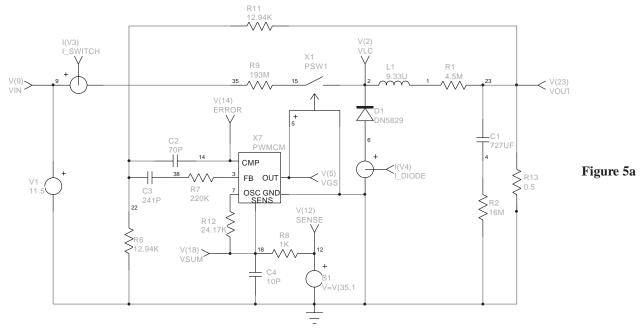

The error amplifier can be selected in function of various criteria: bandwidth, open-loop gain, etc. From a SPICE point of view, the simpler the model, the faster the simulation runs. The easiest method is to use a perfect amplifier like the one depicted in Figure 5a. This model is a simple voltage controlled source which amplifies the input voltage by the open loop gain. To overcome the problems associated with perfect sources, i.e. unrestrained output voltage, the action of a limiting element will confine the output voltage swing within a convenient range. This model is the simplest error amplifier model you can create. Figure 5b represents a transconductance type with its associated clipping network.

Figure 5a

Figure 5b

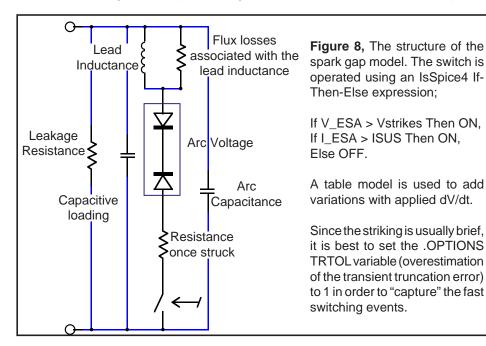

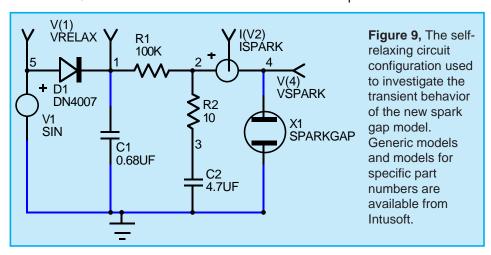

To account for the characteristics of the error amplifier integrated in your real PWM controller, some components have to be added in order to tailor the response curve. The previous models do not really lend themselves to the addition of various internal pole and zero transfer functions.

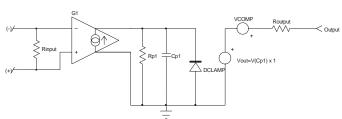

Figure 5c shows another type of amplifier that will facilitate this task.

Figure 5c

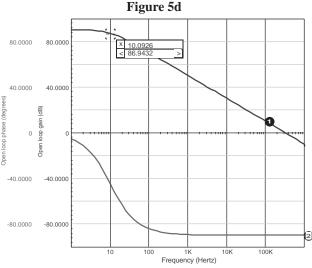

This complete model associates a voltage controlled current source and a unity gain buffer. The first pole is modeled across Rp1 and Cp1, while other passive filter structures may be added between Cp1 and the unity gain buffer. The first stage output clipping is made via the diode DCLAMP and forces the output voltage of G1 to remain within the desired boundaries. Thus, the negative limit is the diode threshold voltage and the upper limit corresponds to the breakdown voltage of the diode. It can be adjusted by the IsSpice BV parameter in the diode model. In order to deliver an output voltage which matches the amplifier specifications, the VCOMP source will compensate the negative threshold of the diode, but also has to be reflected back to its BV value. In our example, the amplifier swings between 200mV and 5V with the following values: .MODEL DCLAMP D (BV=4.2V IBV=10mA) and VCOMP=680mV, as Figure 5d shows:

Figure 5e

The open loop gain is given by:  $AV_{OL} = G1*Rp1$ . With  $G1=100\mu MHOS$  and  $Rp1=316M\Omega$ , we have an open loop gain of 90dB. The first pole is at  $1/2\pi Rp1*Cp1$ , which is 10Hz if Cp1=50.36pF. Figure 5e confirms these results.

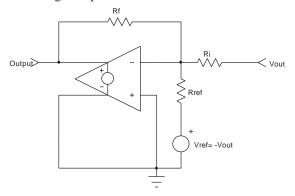

**Simulation trick:** Figure 5f provides an alternative for connecting the reference voltage. It offers better transient behavior and simplifies the feedback network as a first approximation. Note that Vref now becomes -Vout, with  $R_{ref} = R_i$ .

The  $R_{ref}$  resistor in series with the VREF source does not play a role in the loop gain, as long as AOP is closed by  $R_f$ . This condition maintains a virtual ground at the negative input of AOP, and  $R_{ref}$  is in the loop gain calculation. But if you now remove  $R_f$ , or add a capacitor in series, the Vout/Output DC gain is no longer the open loop gain of AOP alone, but is multiplied by 0.5 ( $R_{ref} = R_i$ ) because the negative pin is ½ Vout instead of zero.

Figure 5f

Some SPICE editors not only propose the switching models of many PWM controllers, but also their standalone internal error amplifiers that can easily be incorporated in place of the previous simplified structures.

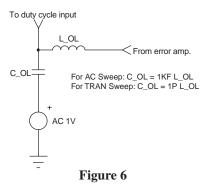

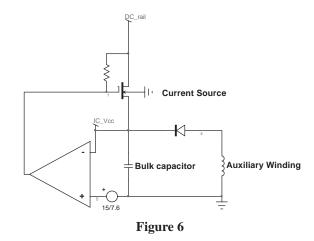

#### Opening a closed loop system

When the complete SMPS structure is drawn, it might be interesting to temporarily open the loop and perform AC simulations. The error amplifier can thus be isolated, and the designer has the ability to adjust the compensation network until the specifications are met. The fastest way to open the loop is to include an LC network as depicted in Figure 6. The inductive element maintains the DC error level such that the output stays at the required value, but stops any AC error signal that would close the loop. The C element permits an AC signal injection, thus allowing a normal AC sweep.

This method has the advantage of an automatic DC duty cycle adjustment, and allows you to quickly modify the output parameter without having to adjust the duty source.

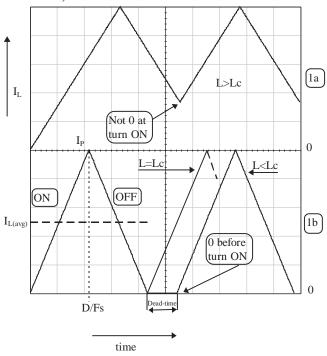

# Average simulation of the Flyback converter in discontinuous mode

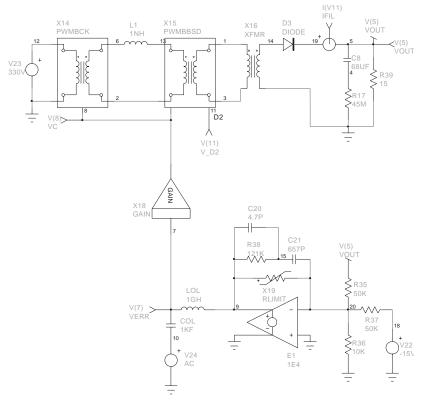

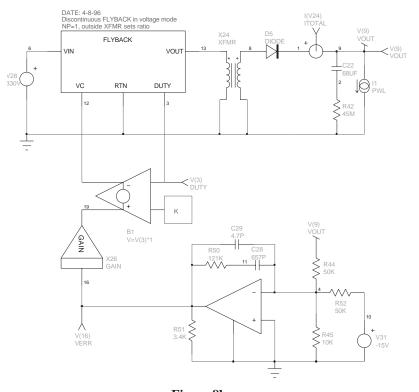

Figure 7a shows a complete average Flyback converter made with Dr. Vincent Bello's models. These models use SPICE2 syntax and can therefore be run on any SPICE compatible engine.

In [3], Dr. Bello described the basic structure models (Buck, Boost ...) and showed how to create topologies such as Flyback and Forward converters. At this time, one model correspondeds to a particular Conduction Mode: Continuous (CCM) or Discontinuous (DCM). The Flyback converter operating in DCM is built with the PWMBCK (Buck) and the PWMBBSD (Discontinuous boost) as depicted in Figure 7a. The primary coil is simply shortened since it does not affect discontinuous operation in the average model. However, Dr. Bello states that despite state-space average technique results, keeping the inductor at its nominal value produces a second high-frequency pole and a RHP zero, as Vorperian demonstrated [4].

Figure 7a

In the models we used here, PWMBBSD has to be modified such that it accounts for operating parameters. In our application (see parameters below) E2 will take the following value:

E2 25 0 1 2 1.25M ; E2 =

$$1/2*L*F_{sw}=T_{sw}/2*L$$

The SMPS drawn represents an off-line wall-adapter delivering 15V@1A. Its nominal characteristics and the corresponding pole-zero calculation are described below:

#### Operating parameters:

$$\begin{array}{llll} V_{\text{out}}\!\!=\!\!15V & I_{\text{nom}}\!\!=\!\!1A & R_{\text{load}}\!\!=\!\!15\Omega \\ V_{\text{in}}\!\!=\!\!330V & L_{\text{p}}\!\!=\!\!4\text{mH} & N_{\text{s}}'N_{\text{load}}\!\!=\!\!0.05 \\ C_{\text{out}}\!\!=\!\!68\mu\text{F} & \text{ESR}\!\!=\!\!45\text{m}\Omega & F_{\text{sw}}\!\!=\!\!100\text{kHz} \\ V_{\text{ramp}}\!\!=\!\!1.7Vpp & \end{array}$$

The iteration process gave a Vduty source of 581mV, which corresponds to a duty cycle of 34.2% (0.581/1.7)

$$\begin{split} G_{\text{PWM}} &= 1/1.7 = -4.6dB \\ K &= 2L_p F_{\text{sw}} / (R_{\text{load}} * (N_s/N_p)^2) = 0.1333 \\ G_1 &= (V_{\text{in}} / \sqrt{K}) * N_s/N_p = 45.19 = 33.1dB \\ G_{\text{Vout/Vduty}} &= G_1(dB) + G_{\text{PWM}}(dB) = 28.5dB \ (26.6) \\ G_{\text{Vout/Vin}} &= (D / \sqrt{K}) * N_s/N_p = 0.0468 \ (-26.6dB \ for \ the \ open-loop \ DC \ audio \ susceptibility) \\ F_{\text{Pl}} &= 2 / 2\pi C_{\text{out}} R_{\text{load}} = 312Hz \\ F_{z1} &= 1 / 2 \ \pi C_{\text{out}} ESR = 52kHz \end{split}$$

To verify the various gains, we open the loop and insert a DC source of 581mV, as previously shown in Figure 3. Then we ask SPICE to perform a .TF (Transfert Function) analysis:

.TF V(5) Vduty;

$$dV_{out}/dV_{duty}$$

open loop gain

.TF V(5) Vin;  $dV_{out}/dV_{in}$  open loop gain,

audio susceptibility

Once computed, the results are placed in the output file. In our application, the .TF statements gave 26.49051 and 0.04544, respectively. The open-loop characteristics of this Flyback operating in DCM were already depicted in Figure 4.

If the amplifier error exhibits a gain  $A_{\text{ErrAmp}}$ , and in the absence of a divider network (Figure 5f), the new closed loop parameters can be expressed as:

$$\begin{split} & dV_{\text{out}}/dV_{\text{in}} \!=\! (G_{\text{Vout/Vin}}) \, / \, (1 + A_{\text{ErrAmp}} G_{\text{Vout/Vduty}}) \\ & \text{closed loop audio susceptibility} \\ & \epsilon = \, V \text{ref} * [1 \, / \, (1 + A_{\text{ErrAmp}} G_{\text{Vout/Vduty}}) \, ] \\ & \text{static error} \end{split}$$

For instance, suppose that an error amplifier with a gain of 100 and a 15V reference voltage is used to close the previous SMPS. With the simulated parameters, the static error is evaluated at: 15\*1/(1+100\*26.49051)=5.66mV. The output voltage is then 14.99434V. If we now step the input voltage by 10V, the corresponding rise in output voltage will be:

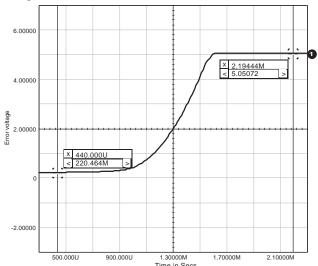

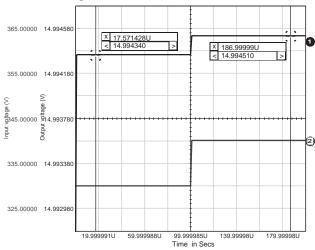

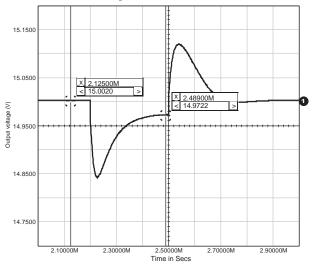

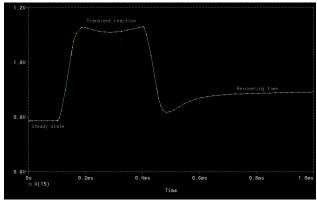

10\*0.04544 / (1 + 100\*26.49051) =  $171.5\mu V$ , which is 14.99451V. Figure 7b shows how SPICE reacts to this test.

Figure 7b

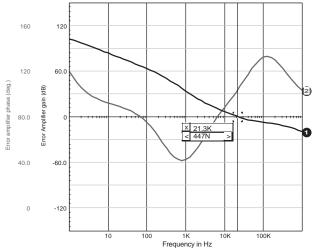

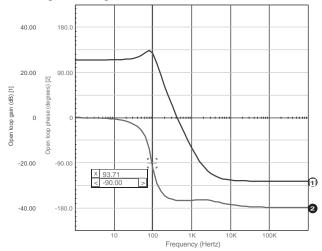

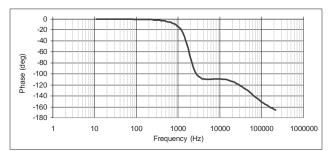

Once all of the modifications are done, the designer can easily tailor the error amplifier so that the SMPS fulfills his target criteria. In our example, the compensation network gives a 21kHz bandwidth (Figure 7c).

Figure 7c

#### New generation models

Intusoft has recently released a SPICE model library for Power Supply designers that includes new models that work in both DCM and CCM and can also be configured in current mode. The library also includes models for various PWM and PFC ICs. These SPICE3 compatible models have been developed by Steven Sandler of Analytical Engineering (Chandler, AZ) and are fully described in [5].

The models are represented by a single box in which the user enters the typical working parameters: Lp,  $F_{sw}$  etc. but also new parameters such as overall efficiency, propagation delay, and load resistance. By adding an external voltage source, you can configure the model the way you want to: voltage mode control, voltage mode control with feedforward, or current mode control with/without compensation ramp.

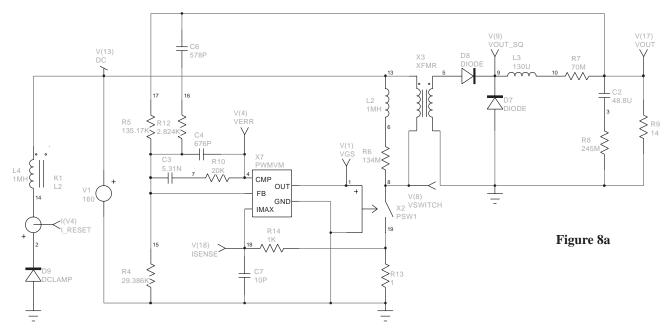

The Flyback model is the one of our main interests, and its symbol appears in Figure 8a with its associated parameters. The various operating modes are obtained by inserting an external voltage source in series with the VC input with the proper polarity, as shown in Figure 8a.

#### Flyback parameters:

L = primary coil, NC = current sense transformer turns ratio NP = output transformer turns ratio; F = operating frequency, EFF = efficiency

RB = current sense resistor; TS = current loop propagation delay

Figure 8a

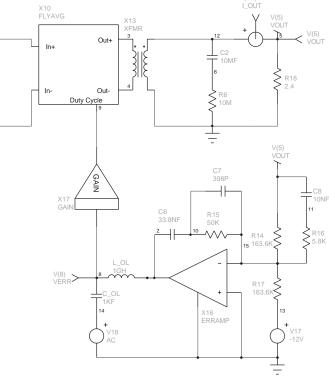

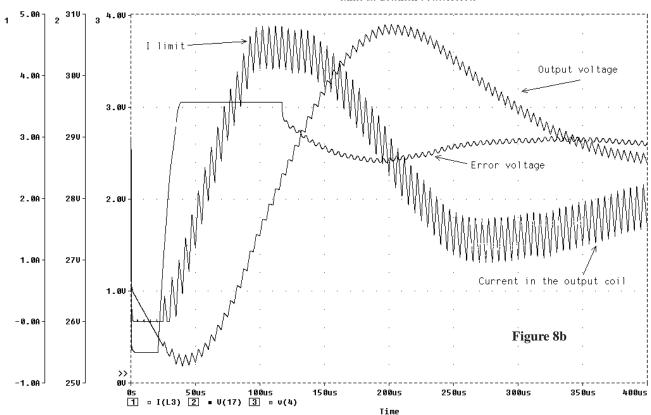

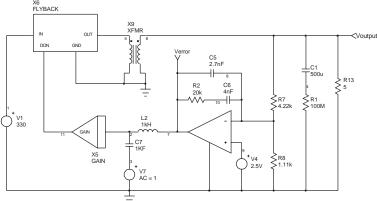

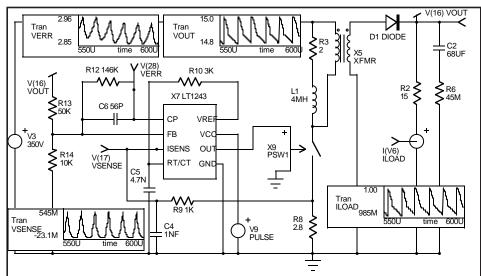

Figure 8b shows the same SMPS as the one we previously studied. The circuit is built with the Flyback model in direct duty cycle control, and the simplified error amplifier structure is replaced with an amplifier model like that which is shown in Figure 5c.

Figure 8b

The output is loaded by a current source whose purpose is to make the supply react to a sudden load increase, as shown in Figure 8c.

Figure 8c

At this stage, you can modify the error amplifier structure and modify the configuration until the SMPS behaves as required.

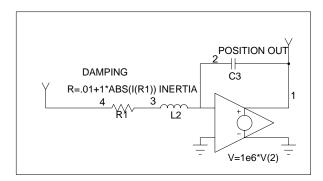

#### **Current Mode Control SMPS**

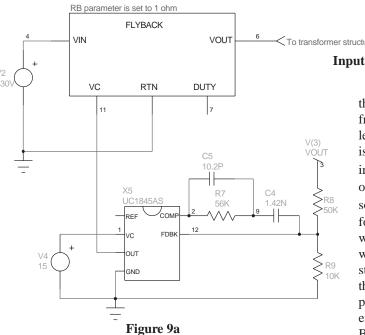

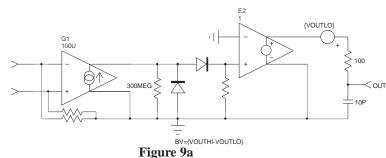

The Flyback model can be easily modified to toggle from one structure to another. Figure 9a shows the new arrangement of the current mode control without implementing any ramp compensation.

In our application, the internal RB, the current sense element, is set to  $1\Omega.$  The compensation network has been slightly modified in order to account for the different gain values. The  $G_{\mbox{\scriptsize Vout/Vduty}}$  gain now depends upon the current

control factor (K) which is set by the sense resistor and, if present, by the internal current gain and the current sense transformer ratio. The error amplifier is replaced with the real UC3845 amplifier which is available as a single SPICE model. Its output is clipped to 1V and the output of the internal error amplifier goes through a diode before it is divided by 3, just as it is built in the real part. You may easily add a compensation ramp, as Figure 8a describes, with a simple voltage-controlled source and the appropriate coefficient.

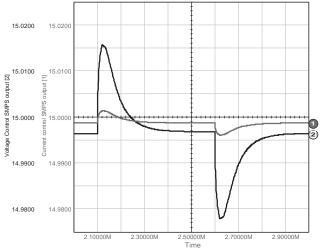

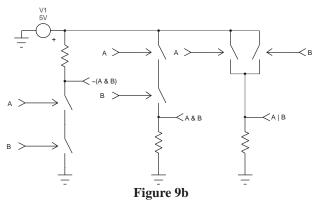

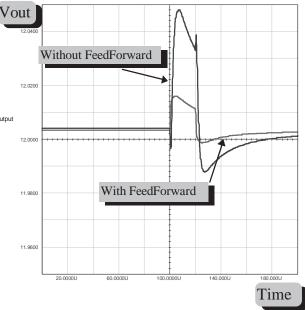

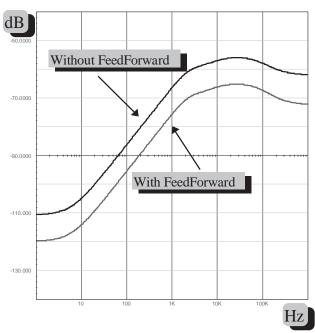

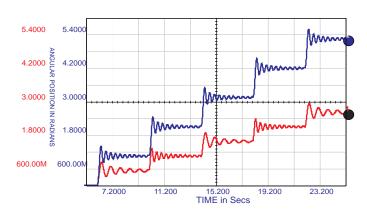

One of the features of the Current Control Mode is its inherent feedforward capability. Figure 9b compares the response to an input step of the previous direct duty cycle SMPS and its Current Mode Control version. The .TF statement gives a  $G_{\mbox{\scriptsize Vout/Vin}}$  of 0.0067, which is 17dB better than the equivalent direct duty cycle version.

Figure 9b

#### Input impedance of the power supply

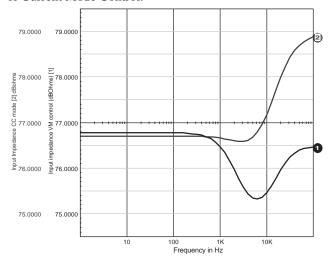

The input impedance has a direct impact on the overall stability when an EMI filter is connected in front of the supply. SPICE will help the designer to select an EMI structure without degrading the characteristics of the power supply. The DC value of the input impedance is easily calculated by:  $Z_{in} = V_{in}^2 \eta / P_{out}$ . (For our 85% efficiency, 15W SMPS operating on a 330V source, the impedance is  $6.17k\Omega$  or  $75.8dB\Omega$ ). Unfortunately, the input impedance is complex. It varies with the frequency and exhibits a negative peaking which is somewhat damped, depending on the SMPS structure. The EMI filter is primarily an LC network. If this network is loaded by a negative resistor whose value perfectly compensates the ohmic losses of the coil, any excitation of the LC network will make it oscillate. Because of the closed loop system, the dynamic impedance,  $dV_{in}/dI_{in}$  is negative. To avoid the previous situation, the designer should keep the input impedance,  $Z_{in}$ , well above the filter's output impedance  $Z_{out}$ . Current Control Mode Power Supplies are less sensitive to the input impedance peaking. When used in conjunc-

#### **SMPS** Design

tion with an EMI filter, these SMPS will be less sensitive to the negative resistance effect than their Voltage Mode counterparts. Figure 9c clearly shows the differences in the  $Z_{\rm in}$  variations depending on the SMPS topology: Voltage Mode or Current Mode Control.

Figure 9c

Once the EMI filter is selected, an excitation stimulus on the input or the load will immediately reveal any parasitic resonance, thus inviting the designer to modify its calculations.

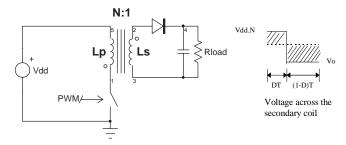

## The Flyback converter in continuous conduction mode

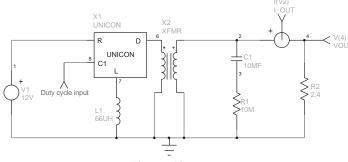

In [6], D. Caldwell showed in practical terms how to implement the PWM switch theory as described by V. Vorperian [4], but, unfortunately, did not give any application examples. The Unicon model is written in SPICE2 syntax and thus permits its use on various compatible platforms. It operates in both DCM and CCM. Figure 10 shows a continuous power supply which uses the Caldwell model. The SMPS operates in continuous mode and delivers 12V to a  $2.4\Omega$  resistive load. As the author stated in his article, you need to edit the UNICON netlist and modify the EDIS generator in order to account for the operating parameters: for a  $66\mu$ H coil associated with a 80kHz operating frequency, the last EDIS parameter equals 0.0947\*(T/2L).

Figure 10

The Flyback operating in the continuous voltage mode is always harder to stabilize because of its second order behavior, and also because of the presence of a Right Half-Plane (RHP) zero. The RHP zero moves with the operating parameters and the designer is forced to roll-off the gain so that the SMPS stays stable within its operating range. Once again, SPICE will ease the designer's task by providing all of the necessary investigation tools to cover the numerous situations encountered by the design in its future life.

Figure 11 depicts another Flyback converter structure, using a model introduced by Lloyd Dixon in [7]. The model was originally written in PSpice syntax (Microsim, Irvine, CA), but the use of arbitrary SPICE3 B sources can easily accomplish the same functions, as we'll describe later. The model works in both operating modes, CCM and DCM. In DCM, the model naturally accounts for the high-frequency Vorperian's pole and RHP zero. The compensation of the error amplifier takes into account the presence of the low frequency pole and zeros, as described below:

Figure 11

Operating parameters:

Reflected output voltage at the primary:  $V_r = V_{out} / (N_s/N_p) = 10.91V$ , neglecting the diode's voltage drop

$$\begin{split} &D_{\text{nom}} = V_{_{r}}/(V_{_{r}} + V_{_{in}}) = 0.476 \\ &L_{_{e}} = L_{_{p}}/(1\text{-}D_{\text{nom}})^{2} = 240.4 \mu\text{H} \\ &G_{\text{PWM}} = 1/2.5 = -7.96 dB \\ &G_{1}(dB) = V_{_{in}}/(1\text{-}D_{\text{nom}})^{2} = 32.8 dB \\ &G_{2}(dB) = 20LOG~(N_{_{s}}/N_{_{p}}) = 0.83 dB \\ &G_{\text{Vout/Vduty}} = G_{1}(dB) + G_{\text{PWM}}(dB) + G_{2}(dB) = 25.7 dB \\ &G_{\text{Vout/Vduty}} = D_{\text{nom}}/(1\text{-}D_{\text{nom}})*N_{_{s}}/N_{_{p}} = V_{_{o}}/V_{\text{in}} = 1 = 0 dB \\ &F_{p_{1}} = 1/2\pi N_{_{s}}/N_{_{p}}\sqrt{C_{\text{out}}}L_{_{e}} = 93.31 Hz \\ &F_{_{z1}} = 1/2\pi ESR*C_{_{out}} = 1.591 kHz \\ &F_{_{z2}} = R_{_{load}}/\left[(N_{_{s}}/N_{_{p}})^{2*}D_{_{nom}}L_{_{e}}2\pi\right] = 2.758 kHz~(Right~Half-Plane~zero) \end{split}$$

You could also use the V. Bello models, as already described in Figure 7a. To make the converter operate in continuous conduction mode, simply replace the PWMBBSD model with the PWMBST model, without modifying its internal node list. This block is also fully documented in the reference papers [3]. The coil is set to its nominal value ( $66\mu H$ ) and you can immediately run an AC analysis to obtain the plot of Figure 12. Nevertheless, the error amplifier compensation network which is shown in Figure 7a is no longer valid to stabilize the continuous SMPS. Figure 11 represents a possible solution.

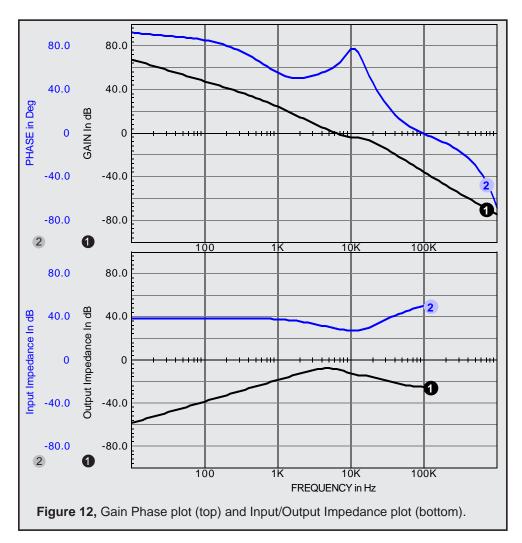

Figure 12

The -90° point corresponds to the -3dB cutoff of the second order system. Note that this value, and also the open-loop gain, are very close to the ones theoretically calculated. At  $F_{z1}$ , the slope becomes -1 with a boost in the phase plot.  $F_{z2}$  starts to act and because of its position in the right half plane, it induces a phase lag. The slope is now 0. This graphic immediately shows you where the various poles and zeros are located, and, by varying some key parameters, you can follow their respective displacements. The compensation network which has been calculated using the worst case conditions then becomes more straightforward.

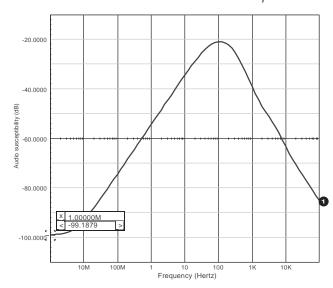

The closed loop audio susceptibility is easily evaluated by decreasing C\_OL and L\_OL to 1pF and by adding the AC 1 statement to the input source. Figure 13 shows how the supply behaves.

Figure 13

The open loop gain obtained by the .TF statement,  $G_{Vin/Vout}$  and  $G_{Vout/Vduty}$ , respectively, is 0.9983 and 18.503. The AOP of Figure 11 exhibits an open loop gain of 10k. But, as we previously stated, in the absence of a feedback resistor, the Vout/Verr gain becomes 5k. The DC audio closed loop susceptibility is then: 20LOG[0.9983/(1+18.503\*5000)] = -99.3dB

#### Limitations inherent to the continuous voltage mode

The error amplifier structure depicted in Figure 11 severely impairs the time response of the power supply in the presence of large output variations. The elements responsible for this behavior are the C7 and C8 capacitors which charge to large transient values when the error amplifier's output is pushed to its maximum. This phenomenon is described in details in [9]. To highlight this problem and eventually compensate it, simply replace the load by a PWL current source that simulates a large load step. Figure 14 represents the simulation result of the error amplifier's output and indicates the amount of time which is required in order to properly recover the output transient.

Figure 14

#### Using the models with different platforms

The use of a model can be extended to various SPICE compatible platforms as long as its syntax conforms to the Berkeley definition. For instance, the simple G, E or complex polynomial sources (POLY) allow the model to be used with different simulators. But if the designer adopts a proprietary syntax, he naturally reduces the implementation of his models among the remaining systems. Lloyd Dixon's model in [7] uses PSpice syntax to clamp the output voltage of some internal sources. This syntax is not SPICE3 compatible. If you would like to run the model with Intusoft's IsSpice or Cadence's Analog WorkBench (San-Jose, CA), you'll need to modify the syntax. One easy solution lies in working with arbitrary sources or B elements, since they accept in-line equations or implement If-Then-Else structures. As a first step, let's look at the following PSpice lines as they are written in Dixon's Flyavg model. The first is intended to limit the output variations of a generator within users-defined boundaries, and the second sets the value of the current generator:

If you try to run these lines using the previously referenced simulators, the internal parser will generate an error. The ED2 generator produces a voltage equal to the difference between nodes 11A and 11, but its output is clipped between 100MV and 1V. For IsSpice and AWB, these lines will look like this:

```

B_ED2 12 0 V = V(11A,11) < 100MV ? 100M :

+ V(11A,11) > 1 ? 1 : V(11A,11) ; IsSpice

B_ED2 12 0 V = IF ( V(11A,11) < 1, IF (V(11A,11) < 100M, + 100M, V(11A,11)),1) ; AWB

```

The Boolean style helps you to understand these lines: If the first condition V(11A,11) < 100MV is true, Then ED2=100MV, If the second condition V(11A,11) > 1V is true Then ED2 = 1V, Else (if any of the two previous conditions is met) ED2 = V(11A,11).

```

The G0 current generator can also be simply written as:

B_G0 4 3 I = V(9.8)*1000*V(12)/(V(11)+V(12))

; IsSpice and AWB

```

```

or, for a voltage source:

B_ED 4 3 V= V(9,8)*500*V(13)

; IsSpice and AWB

```

PSpice also has If-Then-Else conditions, and thus allows you to write logical expressions. For instance, suppose you want to build a perfect comparator whose output is the B1 voltage source, then the following lines illustrate how to make it with through the different syntax:

```

B1 OUT GND V = V(PLUS) > V(MINUS) ?

+ 5V : 10MV ; IsSpice (C syntax)

B1 OUT GND V= IF ( V(PLUS) > V(MINUS),

+ 5, 10M ) ; AWB

E_B1 OUT GND VALUE = { IF ( V(PLUS) + V(MINUS), 5V, 10MV ) } ; PSpice

```

Because of their perfect behavior, the B elements used in comparison functions often require a small RC circuit as an output interface to slow down their transitions. Fixed resistors between the inputs and ground may also be necessary in order to provide the simulator with a DC path in the presence of infinite Pspice input impedances. IsSpice implements the statement .OPTIONS RSHUNT=100MEG, which adds a DC path of  $100MEG\Omega$  to ground for all the nodes in the simulated circuit.

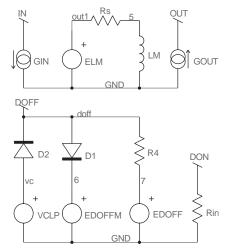

#### Modeling the Flyback converter, other solutions

Professor Sam Ben-Yaakov, from the Ben-Gurion University of the Negev (Israel), has developed a range of models for simulating numerous converter structures [10]. The Flyback model he created is of great interest for the designer since it works for both continuous and discontinuous modes. Another nice feature lies in its simplicity, making the simplifies the conversion from one simulator to another. Figure 15 shows its internal connections and associated sources. The full model is described in Listing 1.

$$\begin{split} & \text{GIN} = I(LM)*V(DON)/(V(DON)+V(DOFF)) \\ & \text{ELM} = V(IN)*V(DON)-V(OUT)*V(DOFF)/N \\ & \text{GOUT} = I(LM)*V(DOFF)/N/(V(DON)+V(DOFF)) \\ & \text{EDOFFM} = 1-V(DON)-9M \\ & \text{EDOFF} = 2*I(LM)*FSW*LM/V(DON)/V(IN)-V(DON) \\ \end{split}$$

Figure 15

Listing 1 describes a full functional netlist of the discontinuous converter of Figure 7a. The model accounts for the high frequency pole and the RHP zero highlighted

by Dr. Vorperian's work. These combined actions can be seen in Figure 16. These points are well above the switching frequency and, most of the time, they can be neglected by the designer. You should always keep in mind that any reference to and/or discussion of poles or zeros above 1/2 the switching frequency is purely fictitious. The poles and zeros in question (other than the first pole and ESR zero) will always shift toward high frequencies at which the average model does not hold. The Nyquist sampling theorem restricts our ability to deal with cases in which the modulation signal is above 1/2 the sampling (switching) frequency. Needless to say, from the engineering point of view, that the frequency response above 1/3 of the switching frequency is irrelevant.

Figure 16

If we take the operating parameters of the first discontinuous Flyback converter example, we can calculate the values of the VORPERIAN's pole and zero, as described in his paper [4]:

$$\begin{array}{lll} Sz_2 = R_f/M*(1+M)*L_p & Right \ Half-Plane \ Zero \\ Sp_2 = 2F_{sw}*[(1/D)/(1+1/M)]^2 & Second \ High \\ & Frequency \ Pole, \ D=0.33 \\ R_f = R_{load}/(N_s/N_p)^2 = 6k\Omega & Reflected \ load \ to \ the \\ & transformer's \ primary \\ M = V_{out}/(N_s/N_p)/V_{in} = 0.909 & Transfer \ Ratio \end{array}$$

The numerical application leads to:  $Fz_2 = 137.6$ kHz and  $Fp_2 = 66.3$ kHz.

If you do not want the model to account for the high-frequency pole and zero, you can, in discontinuous conduction mode, decrease the LM coil between nodes 5 and 8 to 1nH. You will then obtain a phase curve which is similar to the one in Figure 4.

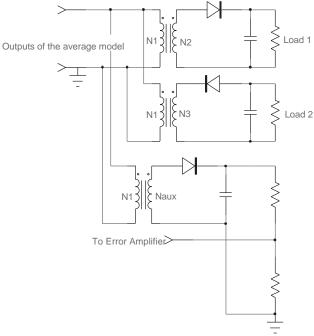

#### Primary regulated Flyback converters

The primary regulation is a feedback method in which the output level is sensed via an auxiliary winding, thus avoiding all galvanic isolation related problems. If the average models cannot highlight the regulation defaults associated with leakage inductances, they may ease your work when you tackle the stability discussion. That is to say, when

multiple outputs are implemented, all of the output networks (capacitors, loads etc.) have to be reflected back to the regulated winding with the corresponding turns ratios. Figure 17 shows how to modify the previous structures in order to implement primary regulation and perform fast and efficient AC analysis.

Figure 17

#### Conclusion

The lack of comprehensive articles upon the subject has made the SPICE approach a difficult stage for SMPS designers who are not used to the simulation philosophy. This article presents a step-by-step method to implement the available models for simulating your own Flyback structures on a SPICE platform. The proprietary libraries and the public domain models will allow you to easily simulate other kinds of topologies such as Buck or Forward converters. Power Factor Correction simulations with Boost structures may also be accomplished, as demonstrated in [3], [5], and [7].

#### References

- R. D. MIDDLEBROOK and S. CUK, "A general Unified Approach to Modeling Switching Converter Power Stages", IEEE PESC, 1976 Record, pp 18-34

- R. KELLER, "Closed Loop Testing and Computer Analysis Aid Design Of Control Systems", Electronic Design, November 22, 1978, pp 132-138

- V. BELLO, "Circuit Simulation of Switching Regulators Using HSPICE", META-SOFTWARE e-mail: DrVGB@AOL.COM

- V. VORPERIAN, "Simplified Analysis of PWM Converters Using The Model of The PWM Switch, Parts I (CCM) and II (DCM)", Transactions on Aerospace and Electronics Systems, Vol. 26, N°3, May 1990

- 5. S. SANDLER, "SMPS Simulations with SPICE3", McGraw Hill, e-mail: ssandler@aeng.COM

#### **SMPS** Design

- D. CALDWELL, "Techniques Let You Write General Purpose SPICE Models", EDN September 6, 1991

- L. DIXON, "SPICE Simulations of Switching Power Supply Performances", UNITRODE Power Supply Design Seminar, SEM-800, e-mail: 71045.1206@COMPUSERVE.COM

- Power Integration Data-Book, AN-6 and AN-8, "SPICE Modeling for Voltage-Mode Flyback Power Supplies" (DCM and CCM)

- 9. L. DIXON, "Closing the Feedback Loop, appendix A, B and C", UNITRODE Power Supply Design Seminar, SEM-500

- Sam BEN-YAAKOV, "Average Simulation of PWM Converters by Direct Implementation of Behavioral Relationships", IEEE Applied Power Electronics Conference (APEC'93), pp 510-516, e-mail: SBY@BGUEE.BGU.AC.IL

#### Acknowledgment

I have greatly appreciated the help of Pr. Sam Ben-Yaakov and Daniel Adar (Ben-Gurion University, Israel), Dr Vincent Bello, Lloyd Dixon (Unitrode) and Daniel Mitchell (Collins-Rockwell).

## **Listing 1:** Complete discontinuous Flyback converter with Sam Ben-Yaakov's model

```

***** SAM BEN-YAAKOV'S FLYBACK MODEL ******

SUBCKT FLYBACK DON IN OUT GND

PARAM FS=100K

; Switching frequency

.PARAM L=4M

; Primary coil

.PARAM N=1

; Internal transformer

BGIN IN GND I = I(VLM)*V(DON)/(V(DON)+V(DOFF))

* GIN IN GND VALUE = { I(VLM)*V(DON)/(V(DON)+V(DOFF)) }

BELM OUT1 GND V = V(IN)*V(DON)-V(OUT)*V(DOFF)/\{N\}

* ELM OUT1 GND VALUE = \{V(IN)*V(DON)-V(OUT)*V(DOFF)/\{N\}\}

RM OUT1 5 1M

LM 5 8 {L}

VLM 8 GND

BGOUT GND OUT I = I(VLM)*V(DOFF)/\{N\}/(V(DON)+V(DOFF))

*\ GOUT\ GND\ OUT\ VALUE = \{\ I(VLM)*V(DOFF)/\{N\}/(V(DON)+V(DOFF))\ \}

VCLP VC 0 9M

D2 VC DOFF DBREAK

D1 DOFF 6 DBREAK

R4 DOFF 7 10

BEDOFFM 6 GND V = 1-V(DON)-9M

* EDOFFM 6 GND VALUE = { 1-V(DON)-9M }

BEDOFF 7 GND V = 2*I(VLM)*{FS}*{L}/V(DON)/V(IN)-V(DON)

* EDOFF 7 GND VALUE = { 2*I(VLM)*{FS}*{L}/V(DON)/V(IN)-V(DON) }

.MODEL DBREAK D (TT=1N CJO=10P N=0.01)

ENDS FLYBACK

**** Perfect Transformer model *****

.SUBCKT TRANSFORMER 1 2 3 4

RP 1 2 1MEG

E 5 4 1 2 0.05

F 1 2 VM 0.05

RS 6 3 1U

VM 5 6

.ENDS TRANSFORMER

***** Error Amp. model *****

.SUBCKT ERRAMP 20 8 3 21

+ - OUT GND

RIN 20 8 8MEG

CP1 11 21 16.8P

E1 5 21 11 21 1

R9 5 2 5

D14 2 13 DMOD

ISINK 13 21 150U

Q1 21 13 16 QPMOD

ISOURCE 7 3 500U

D12 3 7 DMOD

D15 21 11 DCLAMP

G1 21 11 20 8 100U

V172125

V4 3 16 80M

RP1 11 21 316MEG

.MODEL QPMOD PNP

```

```

.MODEL DCLAMP D (RS=10 BV=2.8 IBV=0.01 TT=1N)

.MODEL DMOD D

.ENDS ERRAMP

**** PWM modulator Gain Model ****

SUBCKT PWMGAIN 12

E1 2 0 1 0 0.5882

ENDS PWMGAIN

**** Sam BEN-YAAKOV's model in Discontinuous mode ****

TRAN 1U 1000US

AC DEC 10 10HZ 1MEG

.PRINT AC V(6) VP(6) V(13) VP(13)

.PRINT TRAN V(6) V(13)

R1 4 0 45M

; Output Capacitor's ESR

C1 6 4 68U

; Output Capacitor

X8 11 1 5 0 FLYBACK

; Sam BEN-YAAKOV's model

X9 5 0 6 0 TRANSFORMER

; Output transformer

R8 6 8 50K

R9 8 0 10K

X11 2 11 PWMGAIN

; PWM modulator gain

X12 0 8 13 0 ERRAMP

; Error amplifier

; Output reference voltage

V6 9 0 -15V

R10 13 10 121K

; Erramp Compensation network

C5 10 8 657P

; Erramp Compensation network

C6 8 13 4.7P

; Erramp Compensation network

R12 9 8 50K

; Open loop coil, 1P for .TRAN, 1GH for .AC

L2 2 13 1GH

; Open loop capacitor, 1P for .TRAN 1kF for .AC

C7 2 3 1KF

V7 3 0 AC 1

: AC stimulus

* II 6 0 PWL 0 100M 100U 100M 101U 1A 500U 1A 501U 100M

; Output step response for .TRAN run

RL 6 0 15

; Nominal load for .AC run

V1 1 0 330

; Input voltage

END

```

#### A Tutorial Introduction to Simulating Current Mode Power Stages

Christophe BASSO, consultant, Sinard, France, e-mail: basso@esrf.fr February 1997

SPICE simulation of Current Mode Control (CMC) switch Mode Power Supplies (SMPS) is certainly not a new topic. A lot of people have contributed to make this domain affordable to the design engineer and nowadays EDA packages are shipped with comprehensive dedicated libraries. However, in lack of a tutorial documentation, the choice and the implementation of the models is not always obvious to the novice designer. This article will detail the utilization of 90's models developed around the PWM switch model and more recent ones included in the new INTUSOFT's IsSpice4 SMPS library package (San-Pedro, CA).

#### What kind of model do I need?

Depending on the analysis to be carried on, several choices are offered to the designer. The first one is called a Small-Signal Model (SSM). It assumes that the variations of concern (e.g. output or input voltages) are small around a steady-state DC operating point. In this case, second-order AC cross-products can be neglected and the model is linear around its operating point. The SSM is then usually employed for harmonic simulations where the AC transfer functions are of interest. Do not use a SSM to simulate a 100% transient load span, the result would be wrong since AC cross-products could no longer be negligible. Some SSM models can find their DC point alone, some not and the operating point must then be fed by the designer.

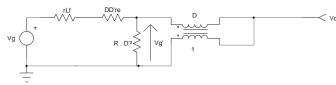

Vincent BELLO has been the first in the 80's to port MIDDLEBROOK's non-linear state-space average models to the SPICE domain [1]. In BELLO's models, the the user to visualize the effects of a 0 to 100% duty-cycle sweep. These large-signal models (LSM) are best suited for TRANSIENT runs.

#### Modeling SMPS, two distinct approaches

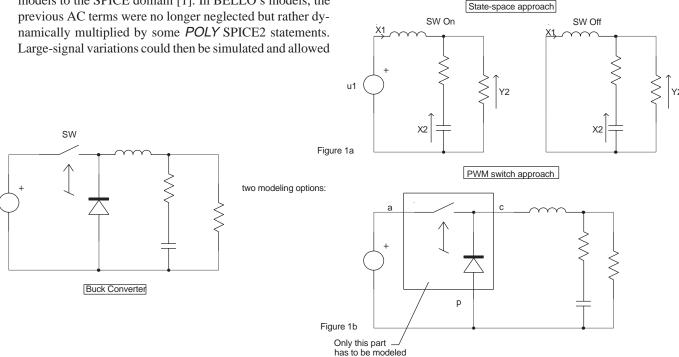

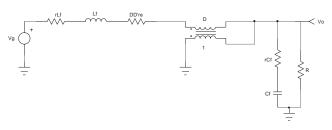

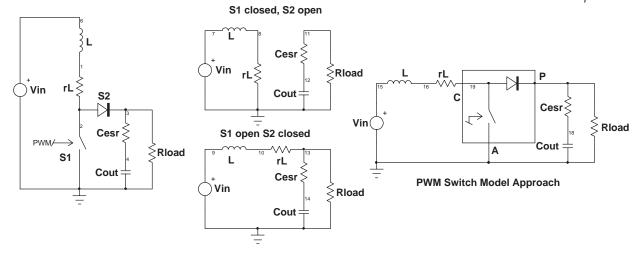

There are two ways to model a SMPS system. The first one is the well known state-space averaging (SSA) method introduced by R. D. MIDDLEBROOK in 1976 [2]. Without describing the process once more, one can state that SSA models the converter in its entire electrical form, as shown in figure 1a for a BUCK. In other words, the SSA process is carried over all the elements of the converter, including various in/out passive components. Depending on the converter structure, the process can be very long and complicated.

In 1986, Larry MEARES and Vatché VORPERIAN, from Virginia Polytechnic Institute (VPEC), developed the concept of the PWM switch model [3, 3a]. VORPERIAN wondered why not simply model the power switch alone, and then insert an equivalent model into the converter schematic, exactly the same way it is done when studying the transfer function of a bipolar amplifier (figure **1b**). With his method, VORPERIAN demonstrated among other results, that the flyback converter operating in discontinuous conduction mode (DCM) was still a second order system, affected by a high-frequency RHP zero.

Figure 1

Figure 2a Figure 2b

Since its introduction, the PWM Switch has not been the object of many publications in the specialized press and some designers might think that its use is only reserved to modeling experts. Because its implementation is easy and powerful, we will go through a quick example, but without entering into the details of its electrical origins.

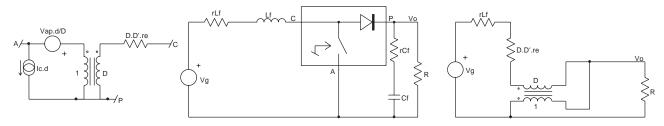

#### Calculating a transfer function with the PWM switch

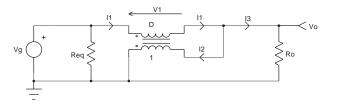

The PWM switch model operating in Continuous Conduction Mode (CCM) is presented in **figure 2a** and can be split into an AC and a DC part. Isolating one part and applying it to the converter under study, gives the designer an immediate insight on how the converter performs in the domain of concern. Reference [3]'s BOOST example appears in **figure 2b** that shows how to properly include the PWM model. If we first consider the DC operation, Lf shorted and Cf open, **figure 2c** appears (re = R // rCf and D'=1-D).

There are different approaches to solve this kind of circuit where the transformer is not commonly wired: the classical brute force, using nodal and loop equations or the soft approach that will consist to transform the schematics until a well known structure is found. Generally speaking, the first method usually leads to correct but abstruse results in which the action of a component inside the considered function is not obvious. Inversely, the soft method produces so-called low entropy expressions [4] and yields insight into the circuit under study.

Figure 3a

Figure 3b

Figure 2c

Let us adopt the second method, thus redrawing a simplified version of figure 2c, as depicted in **figure 3a**. We first mark the currents, keeping in mind that a current entering a winding by a dot leaves the coupled winding by the other dot, in the same direction.

The Vo/Vg transfer function is easily obtained after a few lines:

$$\label{eq:Vg-V1=V0} \begin{split} Vg - V1 &= Vo \\ V1 &= -Vo*D \\ Vg + Vo*D &= Vo \\ Vg &= Vo - Vo*D \text{ so Vo/V} \\ g &= 1 \ / \ (1\text{-D}) \text{ or } \underline{Vo/Vg = 1/D'} \ (1) \end{split}$$

The input impedance, or the way Ro is reflected across Vg (Req), is also simple to derive:

N1.I1 = N2.I2. Since I1 = Vg/Req, it is possible to write: N1 \* Vg/Req = N2 . I2. From KIRCHHOFF's law, I2 = I1 - I3, with I3 = Vo/Ro By definition, N1=D et N2=1 D\*Vg/Req = Vg/Req - Vo/Ro D\*Vg/Req = (Vg\*Ro - Req \* Vo) / (Req . Ro). Simplifying by Req :

D \* Vg = Vg - (Req \* Vo)/Ro Vg / Vo . (1 - D) = Req/Ro. From [1], Vg/Vo = 1-D,

so:  $Req = Ro * D^{2}(2)$

The I3/I1 ratio is important to feed the model with its DC operating points, as we will see later on. If Pin=Po, one can write: Vg. I1 = Vo . I3, so I1/I3 = Vo / Vg = 1 / D'. Back to VORPERIAN's model of figure 2b,

Ic = -I1 = -Io / D'.

With these simple formulas, **figure 3b** represents our DC BOOST where Ro has been reflected according to equation (2). We are in presence of a simple resistive divider whose output Vg' undergoes a 1/D' multiplier ratio (1). Thus, the DC Vo/Vg transfer function is really straightVo forward. So, after

$$\frac{Vo}{Vg} = \frac{1}{D'} \cdot \frac{1}{1 + \frac{rLf}{D'^2 \cdot R} + \frac{re \cdot D}{R \cdot D'}} = M$$

factoring the R\*D'2 term: (3)

Figure 4a

Figure 4b

The AC open-loop line to output transfer function will use the previous results to transform **figure 4a** to **figure 4b**'s drawing, where all the output elements (rCf and Cf) have been reflected to the other side of the transformer.

Figure 4b unveils a classical LC filter affected by its parasitic elements, once again followed by a 1/D' multiplier. Since we want to obtain the Vo/Vg transfer function but also the Zin Zout parameters of this circuit, a good method is to use matrix algebra. Matrix algebra is well suited for numerical computations on a computer and SPICE makes an extensive use of it. It is true that the symbolic answer given by a transfer matrix does not give the designer much insight of the circuit's operation. But one remarkable point is that once you found the matrix coefficients, the resulting transfer matrix contains, in one shot, all the parameters of interest (**figure 5b**). Further, if matrixes require a constant attention when do you manipulate them by hand, it becomes a child play when you use some mathematics programs such as Mathsoft's MathCAD (Cambridge, MA).

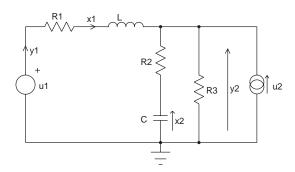

To solve figure 4b's problem, we draw a simplified schematic of the LC filter (**figure 5a**) where we put state and output variables.

Figure 5a

$$T(s) = \begin{bmatrix} \frac{Y1(s)}{U1(s)} & \frac{Y1(s)}{U2(s)} \\ \frac{Y2(s)}{U1(s)} & \frac{Y2(s)}{U2(s)} \end{bmatrix} T_{1,1} = Zin T_{2,1} = Vo/Vg T_{2,2} = Zout$$

Figure 5b

The generalized transfer function of a  $n^{th}$  order linear passive system is:  $M(s) = [M (sI-A)^{-1} B + N]$ , where A and M are the state coefficient matrixes, B and N the source coefficient matrixes [5]. The steps will be to write the state and output equations, ordered as follows:

#### State equations

$$\begin{split} &x1' \!\!\!=\! -\frac{1}{L} \!\! \left[ R1 \! + \! \frac{R2 \cdot R3}{(R2 + R3)} \right] \! \cdot \! x1 \! + \! \frac{1}{L} \! \cdot \! \left( \! \frac{R2}{R2 + R3} - 1 \! \right) \! \cdot \! x2 \! + \! \frac{1}{L} \! \cdot \! u1 - \frac{1}{L} \! \cdot \! \frac{R2 \cdot R3}{R2 + R3} \! \cdot \! u2 \\ &x2' \!\!\!=\! \frac{R3}{(R2 + R3) \cdot C} \! \cdot \! x1 \! - \! \frac{1}{C \cdot (R2 + R3)} \! \cdot \! x2 \! - \! \frac{R3}{C \cdot (R2 + R3)} \! \cdot \! u2 \end{split}$$

#### Output equations

Y1=x1

$$Y2=x1R3 \cdot \left(1-\frac{R3}{R2+R3}\right) + \frac{R3}{R2+R3} \cdot x2 + u2 \cdot R3 \cdot \left(1-\frac{R3}{R2+R3}\right)$$

The final results delivered by MathCAD are in a clear ordered form. Vo/Vg ratio is extracted from figure 5b's matrix transfer,  $T_{21}$ :

$$\frac{\text{Vo}}{\text{Vg}} \frac{1}{\text{D'}} \frac{\text{R3}}{\text{R1+ R3}} \cdot \frac{1 + \text{s} \cdot \text{C-R2}}{\text{s}^2 \cdot \text{L-C} \left( \frac{\text{R3+ R2}}{\text{R1+ R3}} \right) + \left[ \text{s} \cdot \frac{\text{L+ C- (R2 \cdot R3 + R3 \cdot R1 + R1 \cdot R2)}}{\text{R1+ R3}} \right] + 1$$

After replacing by the elements by figure 4b's values and putting the equation into a second order form, we extract the first zero  $s_{z1}$  and the tuning frequency  $\omega_{o}$ :

$$\frac{1}{\sqrt{L \cdot C}} \cdot \sqrt{\frac{R1 + R3}{R2 + R3}} = \frac{1}{\sqrt{L \cdot C}} \cdot \sqrt{\frac{rLf + re \cdot D \cdot D' + D^{2} \cdot R}{rCf + R}}$$

$$\omega_{z1} = 1 / R2 * C = 1 / rCf * Cf$$

$$s^{2*}L*C*(R2+R3)/R1+R3 = s^{2}/\omega_{z}^{2} \longrightarrow \omega_{z} =$$

Zin and Zo can be deducted the same way. To obtain the Vo/d AC transfer function, you can replace the PWM switch model by its small-signal equivalent and re-arrange the schematic until a known structure is found, exactly as we previously did. Discontinuous Conduction Mode (DCM) study would have required the use of the appropriate PWM switch model, but the principle remains the same.

#### SPICE simulations with the PWM switch model

Despite the fact that the PWM switch model was intended to be an alternative tool for teaching SMPS theory, the equivalent SPICE model lends itself very well to simu-

#### **SMPS** Design

lations. In his original form, the PWM switch model is only able to simulate an harmonic behavior. That is to say, you will have to provide the model with its DC operating points. For a BOOST operating in CCM, the DC parameters are shown in the box below. The INTUSOFT's IsSpice4 netlist of the PWM switch model in CCM is as follow:

#### **BOOST DC PARAMETERS:**

D={(VOUT-VIN)/VOUT}

VAP={-VOUT}

VAC={-VIN}

VCP={-VOUT+VIN}

IA={-((VOUT^2)/RL/VIN)\*D}

IP={-VOUT/RL}

IC={-VOUT/RL/(1-D)}

If we now simulate figure 2b's schematic, we obtain the well-known second order response of a BOOST converter operating in CCM.

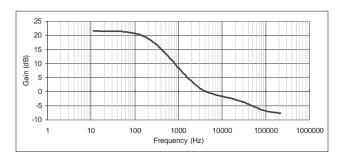

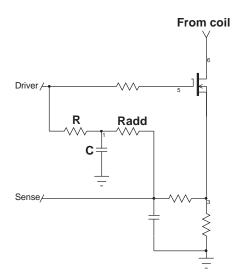

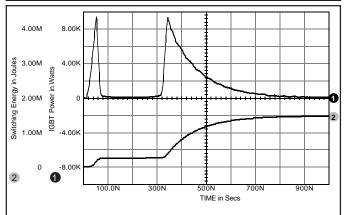

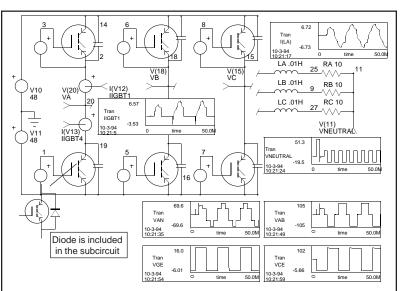

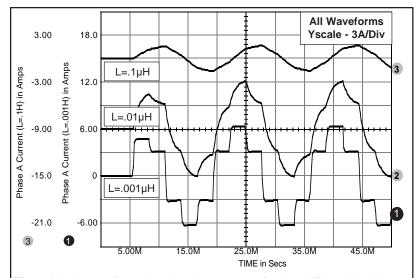

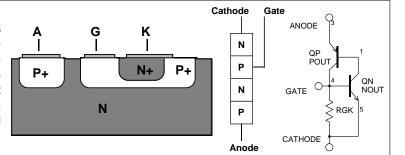

#### Current mode models

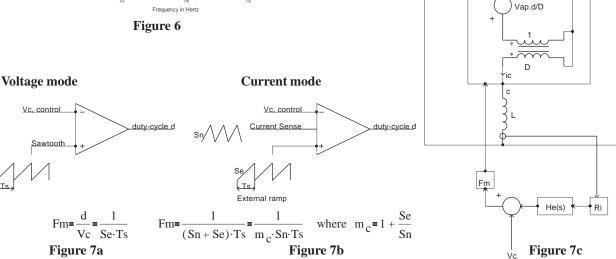

Numerous CMC models have been developed over the past decade. The first models suffered from their inability to predict the instabilities inherent to this kind of control. For instance, they were able to properly model the low frequency response of the CMC power stage, but the currentloop instability had to be addressed as a separate issue. In 1990, Raymond RIDLEY of VPEC, showed that a CMC power stage was best modeled by a third order polynomial form [6]. In his thesis, RIDLEY identified the current sampling action as being culprit of experimentally observed  $\rm F_{switching}/2$  sub-harmonic oscillations. Actually, a CMC differs from a voltage mode converter in the way the duty-cycle is generated. In **figure 7a**, the naturally sampled duty-cycle modulator is fed by an error voltage Vc and a reference sawtooth. This is classical voltage mode. Figure 7b depicts a current mode modulator where the current sense information is added, resulting in a different transfer function Fm for the Pulse Width Modulator section. Since the power stage was not affected by this change, RIDLEY built his model using the average PWM switch to which he added an internal current sampling loop. The new model is presented in **figure 7c**, for steady-state on/off inductor voltages. He(s) is the second order polynomial form RIDLEY found to represent the sampling process in the continuous time, Ri scales the current information (delivered by a simple resistor or via a transformer) and Fm models the duty-cycle generation, as explained in **figures 7a** (Ri=0) or **7b** (Ri $\neq$ 0). RIDLEY's model is universal since reducing Ri to 0 (or a very low value in IsSpice4) shadows the internal current loop and turn the model into voltage mode.

#### **Current mode instabilities**

A current mode controlled SMPS exhibits one low frequency pole,  $\omega_p$ , and two poles which are located at Fs/2. These poles move in relation to the duty cycle and the

PWM Switch mode

external compensation ramp, when present. The two high frequency poles present a Q that depends on the compensating ramp and the duty cycle. RIDLEY demonstrated that the Q becomes infinite at D=0.5 with no external ramp, confirming the inherent instability of a current mode SMPS which has a duty cycle greater than 0.5. Q and  $\omega_p$ , which are part of the  $V_{_{\rm O}}/V_{_{\rm c}}$  transfer function, are expressed as follows:

$$Q = \frac{1}{\pi \cdot (mc \cdot D' - 0.5)}$$

$$\omega_p = \frac{1}{CR} + \frac{Ts}{LC} \cdot (mc \cdot D' - 0.5)$$

where  $m_c = 1 + S_e / S_n$ .  $S_e$  is the external ramp slope,  $S_n$  is the inductor on-time slope. D' = 1 - D

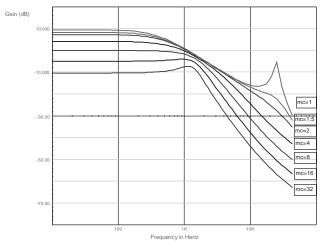

The presence of two high-frequency poles in the V<sub>0</sub>/V<sub>0</sub> transfer function is due to the sampling process of the inductance current. Actually, this process creates two RHP zeroes in the current loop which are responsible for the boost in gain at Fs/2 but also stress the phase lag at this point. If the gain margin is too low at this frequency, any perturbation in the current will make the system unstable since both voltage and current loops are embedded. You can fight the problem by providing the converter with an external compensation ramp. This will oppose the duty cycle action by lowering the current-loop DC gain and correspondingly increasing the phase margin at Fs/2, which will damp the high Q poles in the V<sub>2</sub>/V<sub>2</sub> transfer function. As other benefits of ramp compensation, RIDLEY showed that an external ramp whose slope is equal to 50% of the inductor downslope could nullify the audio susceptibility (mc=1.5). As more external ramp is added, the low frequency pole ω moves to higher frequencies while the double poles will be split into two distinct poles. The first one will move towards lower frequencies until it joins and combines with the first low frequency pole at  $\omega_{\rm p}$ . At this point, the converter behaves as if it is operating in voltage mode (mc=32, **figure 8c**).

#### CMC models and IsSpice4

In his thesis report, RIDLEY presented his models in a simple SPICE2 format, without any parameter passing capability. The following IsSpice4 netlist provide greater flexibility by providing full SPICE3 parameter passing for the CCM model. The DCM listing will not be printed here but can be obtained via e-mail to the author at basso@esrf.fr.

```

.SUBCKT PWMCCM 1 2 3 4 5 {RI=0.33 L=37.5U FS=50K RL=1 + D=0.45 VAP=11 VAC=6 IC=0.8 VP=2}

* A P C C' Control

.PARAM TS = {1/FS} ; Switching time

.PARAM PI = 3.14159 ; PI constant

.PARAM KF = {-(D*TS*RI/L)*(1-D/2)}

.PARAM KR = {((1-D)^2*TS*RI)/(2*L)}

**** PWM Switch model ****

BE2 7 1 V = V(17)*({VAP/D})

```

```

BGxf 7 2 I = I(Vxf) * {D}

BExf 9 2 V = V(7,2) * {D}

Vxf 9 3 0

**** He(s) Circuit ****

Hi 10 0 Vxf 1

C1 10 12 {TS/PI}

L1 12 13 {TS/PI}

C2 13 14 {TS/PI}

Re 14 15 -1.57

E1 15 0 12 0 -1E6

**** Summing gains ****

BEd 16 0 V = { V(1,4)*KF + V(4,2)*KR + V(15)*RI + V(5) }

**** Modulator Gain ****

BEFm 17 0 V = { V(16)*1/(VP+(VAC*TS*RI/L)) }

.ENDS

```

#### **BUCK DC parameters:**

BG1 1 2  $I = V(17) * \{IC\}$

```

\label{eq:continuous} \begin{split} D &= \{(VOUT/VIN)^*(RL+RS)/RL\}\;;\; DC\; duty\; cycle\; for\; continuous\; mode\\ D &= \{SQRT((M^2*8*L)/(((2-M)^2-M^2)*RL*(1/FS))))\}\;\\ &\quad;\; Discontinuous\; mode\\ VAP &= \{VIN\} \end{split}

```

```

VAP={VIN}

VAC={VIN-VOUT}

VCP={VOUT}

IC={VOUT/RL}

IA={(VOUT/RL)*M}

IP={IC-IA}

```

As for the PWM switch, you need to provide the model with DC operating points. BUCK DC parameters are given above. You will notice the presence of the C' connection in the model. This connection is intended to inject current information inside the model, as reference [6] thoroughly explains.

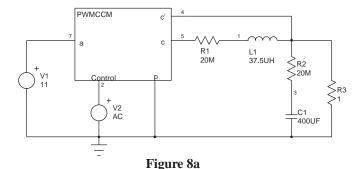

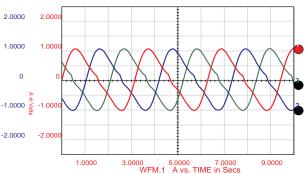

A simple BUCK converter operating at 50kHz will be simulated, according to **figure 8a**.

The simulation results of **figures 8c** and **8d** clearly

demonstrate the action of the compensation ramp upon the CMC BUCK converter. These curves have been automatically generated by IsSpice4 using its powerful Interactive Command Language in conjunction with the INTUSOFT's graphical investigation tool, IntuScope. For large mc (32), the converter's transfer function behaves like a classical voltage mode control system. Inversely, in lack of compensation ramp, the high Fs/2 Q will make the SMPS unstable in response to a transient step. The model would also let you investigate different transfer functions (audio susceptibility), Zin/Zout parameters and give an immediate insight of the compensation ramp effects.

#### **SMPS** Design

# Figure 8b Phases (deg) -45.00 -90.00 -135.0 -180.0 10 Frequency in Hertz

Figure 8c

#### New large-signal models

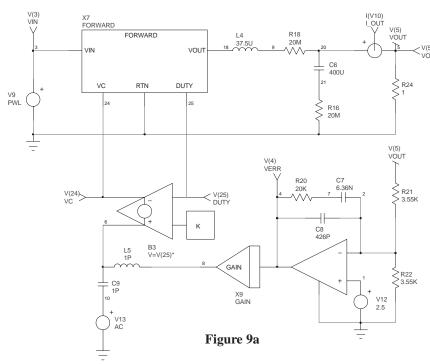

INTUSOFT has recently released its new SMPS library that contains numerous IsSpice4 models operating in switched or averaged mode. Among these novelties, the FLYAVG and FORWARD average models let you simulate any voltage/current mode converter and allow the testing to large steps. Reference [7] details the way the models were derived. As a simulation example, we will take figure 8a's BUCK converter to see how you can take profit of these new parts. **Figure 9a** depicts the electrical schematic whose netlist will be given to IsSpice4.

The FLYAVG model does not take into account the previous Fs/2 high frequency poles. But it is well suited to study the impact of the compensation ramp upon the overall characteristics. For instance, RIDLEY showed an nullified audio susceptibility for an external ramp whose slope equals 50% of the inductor downslope. To highlight this phenomenon, let us sweep the K coefficient which sets the amount of external compensation in figure 9a. IsSpice4's optimizer capability will ease the work by providing the adequate automation tool. You simply need to add the following line and run IsSpice4 to see multiple run results gathered upon a single graph (figure 9b): \*OPT RAMP=0.1 TO 0.15 STEP=5M.

Figure 9b

For low compensation ramps, the phase of the line-to-output transfer function is <u>negative</u>. It is clearly depicted by the lower curves where the sudden stepped-up input voltage engenders a negative output transient. As more ramp is injected, the output step diminishes until null audio susceptibility is obtained, providing the designer with the value of the optimum ramp (K=0.135).

#### Conclusion

Both small and large-signal models should help the designer to better understand the intricacies of CMC converters stability. The new INTUSOFT's SMPS library includes averaged but also popular switched models (e.g UC384X family), giving the designer all the tools he needs to develop rugged designs from the theoretical study (average models) to realistic simulations (switched models).

#### References

- V. BELLO, "Circuit Simulation of Switching Regulators Using HSPICE", META-SOFTWARE

(e-mail: DrVGB@AOL.COM)

- R. D. MIDDLEBROOK and S. CUK, "A general Unified Approach to Modeling Switching Converter Power Stages", IEEE PESC, 1976 Record, pp 18-34

- 3. Vatché VORPERIAN, "Simplified Analysis of PWM Converters Using The Model of The PWM Switch, Parts I (CCM) and II (DCM)", Transactions on Aerospace and Electronics Systems, Vol. 26, N°3, May 1990

- R. D. MIDDLBROOK, "Low-Entropy expressions: The key to Design-Oriented Analysis", IEEE Frontiers in Education, 21st Annual Conference, Purdue University, September 21-24, 1991;399-403

- 5. D. M. MITCHELL, "DC-DC Switching Regulators Analysis", distributed by e/j BLOOM Associates (71147.3274@compuserve.com).

- 6. R. B. RIDLEY, "A new small-signal model for current-mode control", PhD. dissertation, Virginia Polytechnic Institute and State University, 1990 (e-mail: RRIDLEY@AOL.COM) This document can be ordered from Ray RIDLEY's homepage: http://members.aol.com/ridleyeng/index.html

- S. M. SANDLER, "SMPS Simulation With SPICE3", McGraw-Hill, ISBN 0-07-913227-8 (e-mail: SSANDLER@AENG.COM)

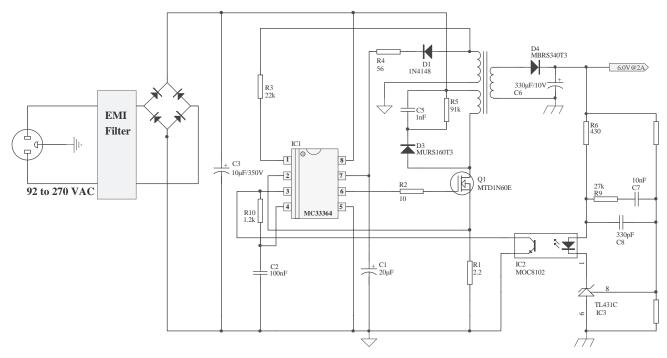

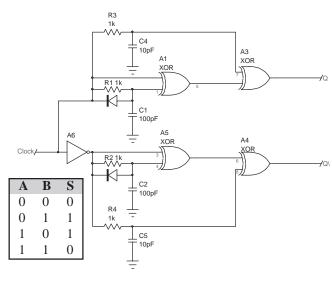

#### Write your own generic SPICE Power Supplies controller models

Christophe BASSO, e-mail: basso@esrf.fr

November 1996

Simulating the switching behavior of a Switch Mode Power Supply (SMPS) is not always an easy task. This is especially true if the designer wants to use an exact SPICE model for the Pulse Width Modulator (PWM) controller which will be used in the design. The PWM model may exist, but its syntax may be incompatible with your simulator. If the model has not been created, the debate over whether or not to do the simulation is closed! The solution that is proposed in this article consists of writing your own generic model of the PWM controller and then adapting its intrinsic parameters to comply with the real one you are using. Fixed frequency Current Control Mode (CCM) and Voltage Control Mode (VCM) models will be thoroughly covered in this article, as well as the model translation between different simulators.

#### The Berkeley B element, the standard behavior element

An efficient PWM model that is easy to model must include functions that are generic. For instance, it would not be clever to model an internal current comparator with the complete transistor architecture of a LM311 or a LM193. Fortunately, there is a simple in-line equation that can describe the perfect comparison function. By adding some passive elements to incorporate various effects (propagation delay, input offset voltage, etc.) we can achieve the functionality we need without sacrificing the simulation speed.

The non-linear controlled source, or B element, is part of Berkeley SPICE3, which was released to the public domain in 1986. Depending on the compatibility of your SPICE 3 simulator, the corresponding syntax may vary significantly. B elements can be linear or non-linear current or voltage sources. Some vendors have expanded the B element syntax to include BOOLEAN and IF-THEN-ELSE functions. For INTUSOFT's IsSpice4 (San Pedro, CA) and CADENCE's Analog WorkBench Spice Plus (San-Jose, CA), the writing of I or V math equations using B elements is the same because both are SPICE 3 compatible. For example, current/voltage generators whose current depends on various nodes can be expressed as:

B1 1 0 I = V(5,8)\*100\*V(10)/(V(8)+V(12)) ; IsSpice or AWB current source B2 2 0 V= V(9,8)\*500\*V(12) ; IsSpice or AWB voltage source

MICROSIM's PSpice (Irvine, CA) has departed from the Berkeley standard and uses a different syntax. PSpice modifies the standard calls for dependent voltage controlled sources (E and G elements). The equivalent PSpice examples are as follows: G1 1 0 VALUE = { V(5,8)\*100\*V(10)/(V(8)+V(12)) } ; PSpice current source E2 2 0 VALUE = { V(9,8)\*500\*V(12) } ; PSpice voltage source

#### Implement your logical operations

As stated in the above "paragraph, BOOLEAN and IF-THEN-ELSE expressions have become a part of most vendors' B elements. Their implementation also depends on the SPICE simulator. INTUSOFT exploits the concept of "binary" voltage, that is to say, a node value which is lower or higher than a user-defined threshold can be associated with 1 or 0. This threshold is driven by the keyword LTHRESH, whose value is set via a .OPTIONS line. Two other options, LONE and LZERO, will define the HI and LO electrical values which are delivered by a B element source when it is performing such BOOLEAN operations. A simple NAND equation between two nodes is simply expressed as:

BNAND 3 0 V=  $\sim$  ( V(1) & V(2) ) ;IsSpice complemented ( $\sim$ ) AND operation between V(1) and V(2)

Because the other SPICE simulators do not directly support this syntax, it would be much easier to adopt a simpler expression in order to simplify any further translations. If we pass the logical thresholds directly into the equation, we obtain the following IsSpice IF-THEN-ELSE statement:

BNAND 3 0 V= (V(1)>800M) & (V(2)>800M)? 0V: 5V In other words, IF V(1) is greater than 800mV AND V(2) is greater than 800mV, THEN V(3,0)=0V; ELSE V(3,0)=5V

Now the translation to AWB and PSpice syntax is more straightforward:

```

E_BNAND 3 0 VALUE = { IF ( (V(1)>800M) & + (V(2)>800M), 0V, 5V ) } ; PSpice NAND gate BNAND 3 0 V = IF ( (V(1)>800M) && + (V(2)>800M), 0, 5 ) ; AWB NAND gate

```

Note that the AWB parser does NOT accept suffixes for the passed numerical values and the && symbol is doubled as in the C language to distinguish a logical AND from a binary AND. The diversity in implementing the B elements is only bound by the user's imagination. What we have shown above is only a small part of the possibilities offered by Behavioral Modeling via the B element.

If your simulator does not support B element modeling, the situation becomes complex. Some examples on how to model the logical functions with SPICE2 syntax are given at the end of this article.

Here's an application example, a simple voltage limiter which limits the differential voltage of nodes 1 and 2 between 100mV and 1V:

```

E1 3 0 TABLE {V(1)-V(2)} 100M,100M 1,1 ; PSpice B1 3 0 V = IF ( V(1,2) < 1, IF (V(1,2) < 100M, 100M, + V(1,2)),1) ; AWB (No suffixes!) B1 3 0 V = V(1,2) < 100MV? 100M : V(1,2) > 1? + 1 : V(1,2) ; IsSpice

```

In other words,

IF V(1,2) is less than 100mV, THEN V(3,0)=100mV; ELSE IF V(1,2) is greater than 1V, THEN V(3,0)=1V, ELSE V(3,0)=V(1,2)

B elements switch in essentially a zero time span. This characteristic may create convergence problems on transitions associated with these perfect sources. We recommend that you tailor the output switching times in a more realistic manner. A simple RC network is suitable for this purpose. A perfect comparator which accounts for these conditions is given below. We have included it in a SUBCIRCUIT in order to highlight the philosophy of constructing your own models:

Now that we have reviewed the basics of generating in-line equations, let's dip into the nitty-gritty of a constant frequency CCM PWM controller.

#### Current mode controllers, a well known architecture

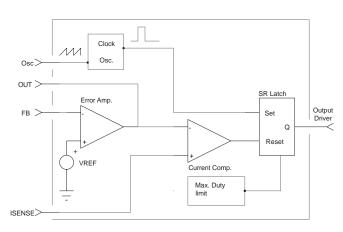

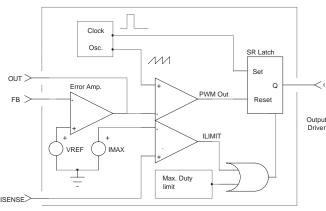

**Figure 1**, the internal circuitry of a generic single output CCM PWM controller.

Figure 1

The modelling of such a block consists of: a) defining <u>and</u> testing each subcircuit <u>individually</u>, and b) assembling all of these domino-like circuits to form the complete generic model. All individual blocks should be tested before they are used within larger models. Below are some recommendations that will ease your task:

- Draw the symbol of your generic model with your favorite schematic capture tool. Once this is done, you won't have to worry about incorrect pin connections (as you would if you were creating a SPICE netlist with a text editor). Internal subcircuit testing is simplified since you may then access the connection pins directly in the schematic model, and the pin passing process (from schematic to netlist) is performed automatically.

- Place comments on every pertinent line, either with a

"\*" in column one (for a complete line), or a ";"

immediately preceding a comment within a line. Also,

use different commented header names for each section

of code within the listing.

- Use descriptive names for the components you assemble in the subcircuit netlist, i.e. VCLOCK for a clock source, RDUM for a dummy load, etc.

- Use subcircuits whenever a function is called more than once. Even if the function is only called once, you can create a subcircuit and therefore simplify the netlist. This will also facilitate the writing of new models because the .SUBCKT functions are easily pasted into the netlist. Also, if required, the conversion process to another platform will be greatly simplified.

- Use realistic parameter values for primitive SPICE components such as the diode (D). These models may generate convergence problems since some of the default parameters are set to zero. For example,

MODEL DMOD D (TT=1N CJO=10P RS=100M)

- Use a main subcircuit pin number of up to 10 or 20 and use incremental decimal digit notation as you change the internal function. This is especially recommended for complex models in which the parent subcircuit may be large. Below is an arbitrary example, where nodes 7 through 19 are preserved in order to output test signals or add additional pins:

.SUBCKT EXAMPLE 1 2 3 4 5 6 \*\*\*\* MAIN CLOCK \*\*\*\* VCLOCK 20 21 PULSE : Main clock ICHARGE 22 24 10MA ; Current charge of capacitor C1 \*\*\*\* TRIGGER \*\*\*\* RTHRES 30 33 10K : Threshold high CDEL 33 38 10NF ; Propagation delay \*\*\*\* COMPARATOR \*\*\*\* RINP 40 42 10K ; Input resistor RFEED 45 49 120K ; Feedback resistor .ENDS EXAMPLE

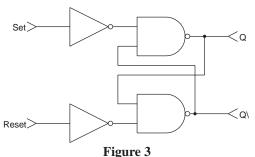

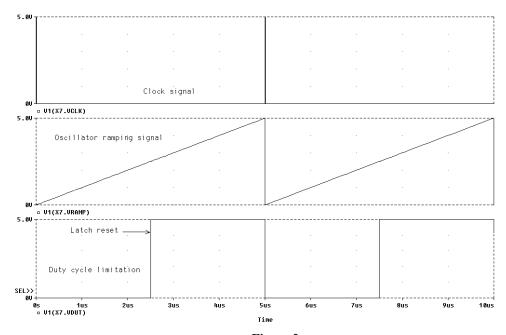

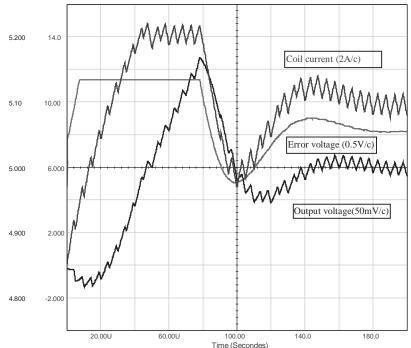

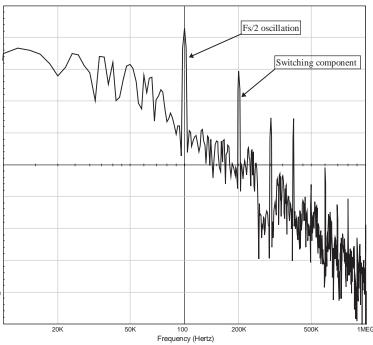

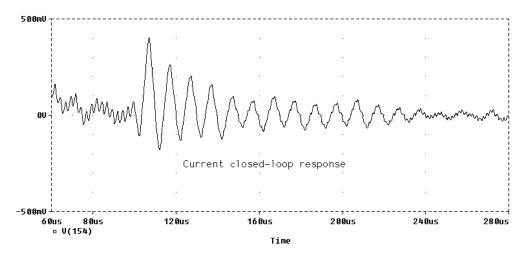

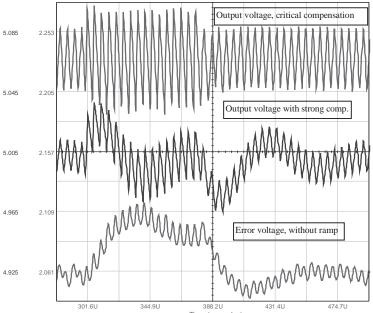

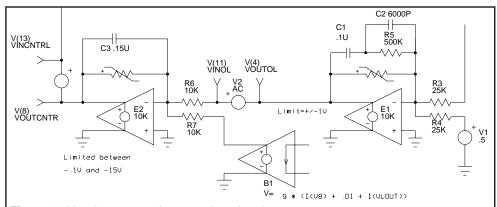

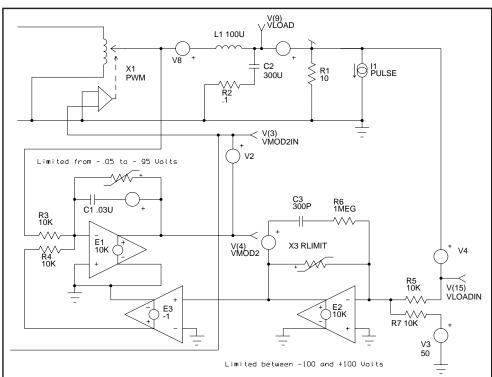

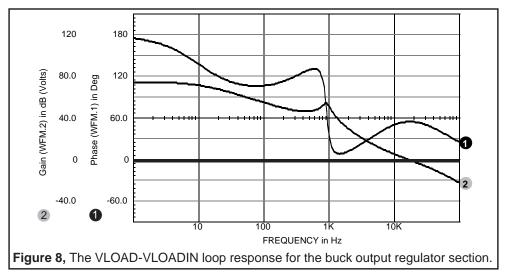

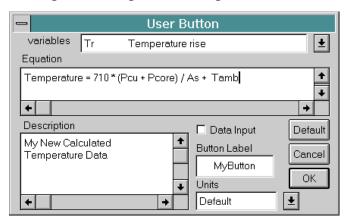

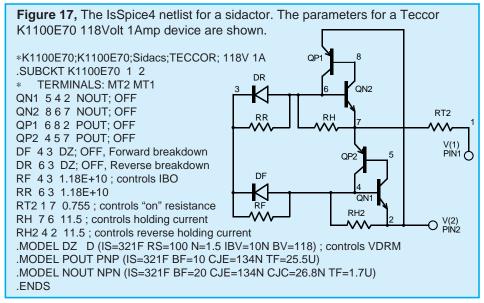

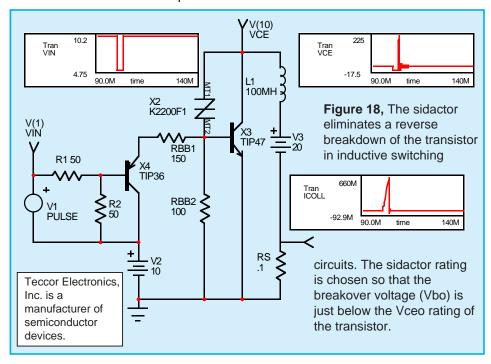

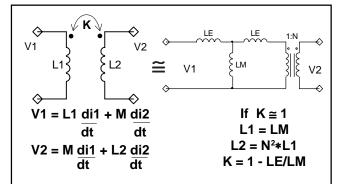

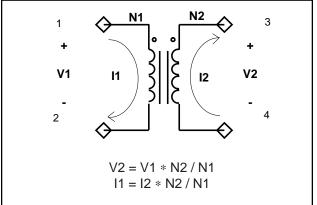

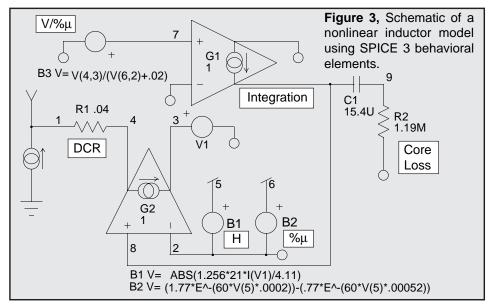

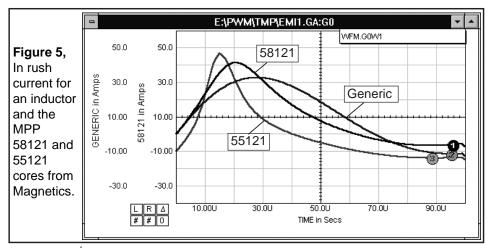

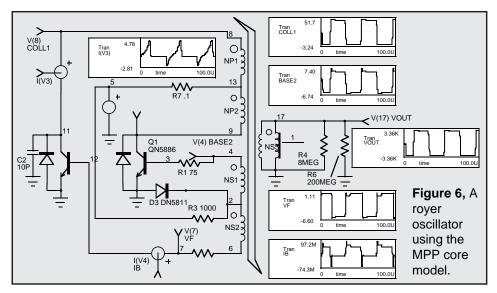

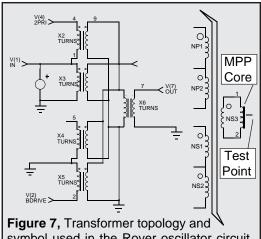

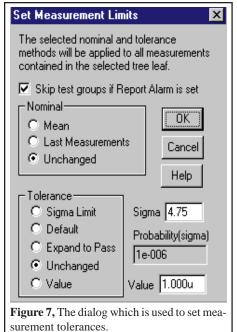

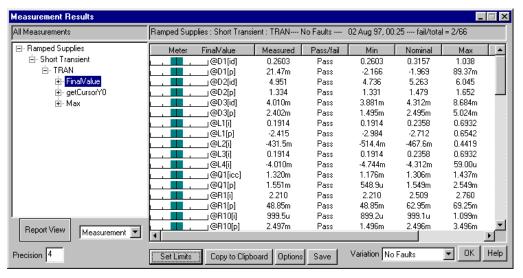

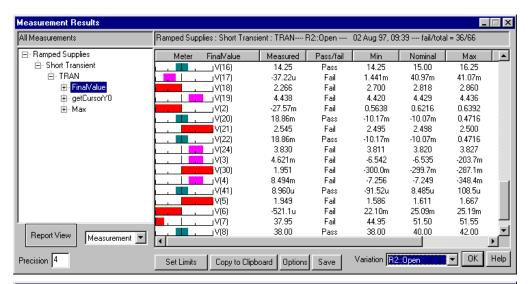

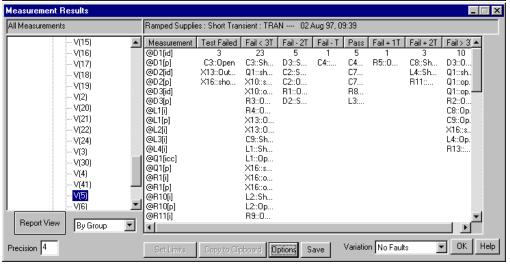

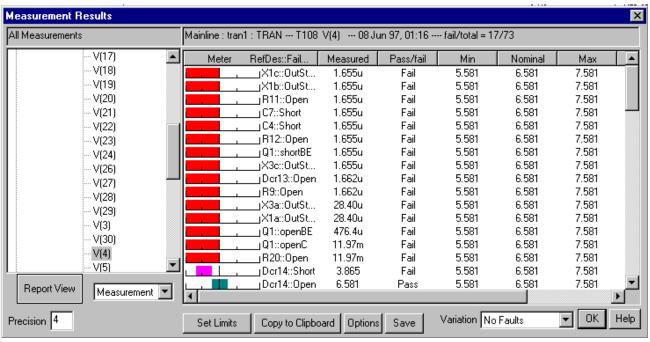

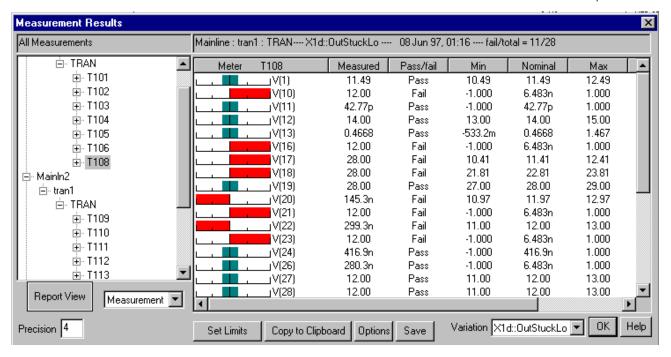

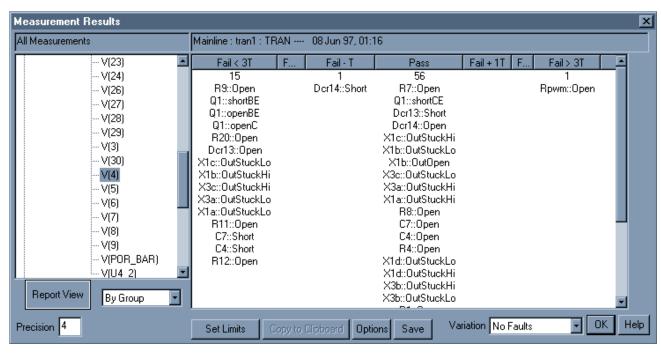

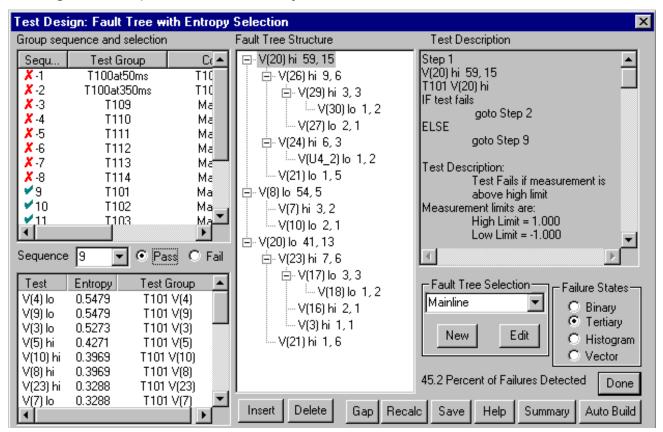

#### Writing the model step by step