# **IEEE Power Electronics Society NEWSLETTER**

### ISSN 1054-7231

## President's Message

A primary goal of the IEEE is to globally share knowledge about electrical and information technologies and sciences. This clearly is also a primary interest of PELS, and an important reason to become a member. PELS is a leader in publishing the latest results and technical developments within its scope. But meeting the goal to share knowledge goes far beyond just disseminating research results. It must also include continuing, life-

long education for our members. This is particularly important to practicing engineers. PELS is committed to expanding and enhancing continuing ed op-

portunities such as the distinguished lecturer program, available to all chapters, and through tutorials and seminars. Our conference tutorials have always provided an excellent selection of current and interesting educational topics. APEC provides as impressive an array of "professional seminars," as any conference I know. PESC and INTELEC also offer an excellent selection of tutorials on timely subjects at each conference. I want to encourage our chapters to develop their own tutorials catering to local members. Not only is this an excellent service to members, but proceeds can be used for other important chapter functions.

Attendance at tutorials, however, is often not possible for many members, especially those who are only peripherally interested in a general area. I would like to see more papers of a tutorial nature submitted and accepted in our conferences. This would serve two purposes. First, there seems to be a consistent desire among conference attendees to have more papers of a "practical, applied, or industrial" nature. Tutorial papers most often fit this bill, and will make our conference paper sessions even more attractive. Furthermore, tutorial papers allow people recently interested in a topic to get up to speed in areas too new to be included in other texts. Secondly, IEEE conference proceedings and papers are often the easiest and lowest cost publications which all members can access from libraries or purchase. Continued on page 9

#### April 2001

# INTELEC<sup>®</sup> 2001 Coming to Scotland in October

The 23<sup>rd</sup> International Telecommunications Energy Conference (INTELEC) will be held 14-18 October 2001, in Edinburgh, Scotland, UK. Over 120 technical papers and workshops will cover telecomm power and cooling issues including DC power systems, UPS systems, batteries, distribution power and AC power systems. Powering and cooling issues will include telephony, cable, mobile and office. The conference theme for 2001 is "No Power, No Service, No Revenue."

INTELEC has increasingly attracted middle to senior managers from all over the world and now represents an unparalleled opportunity to meet and discuss power and cooling trend developments with other leading players and service providers. The event will be chaired by John Parsons, BT. The IEEE Power Electronics Society (see <u>http:// Continued on page 2</u>

#### Continued on page

# APEC<sup>®</sup> 2001 Sets New Attendance Records

APEC 2001, the most comprehensive conference addressing "applied" power electronics, was held March 4-8 at the Disneyland Hotel in Anaheim CA. Attendees had the opportunity to attend 15 professional education seminars, 31 multi-speaker technical sessions, 12 vendor application seminars, three RAP Sessions, the Exhibit Hall, the 15th annual Micro Mouse compe-

tition, and our Wednesday evening banquet held in the Disneyland Theme Park. The true test of the strength of any conference is attendee support during an economic downturn.

With the NASDAQ falling 60% from it's record high of one year ago, travel restrictions were imposed on some of our Fortune 100 companies. Yet in spite of disappointing Wall Street results, predicted heavy rain, and temporary shutdown of major northeast airports due to a snowstorm, APEC 2001 set new records for technical session attendance (736), total attendance (2275) and exhibitor participation (820)! *Continued on page 3*

# Plans Finalize for PESC<sup>®</sup> 2001 in Vancouver

June 17-21 is approaching rapidly and we are eagerly looking forward to welcoming you to Vancouver then for PESC 2001. Conference registration and accommodation reservations are available on the PESC 2001 website at <u>www.conferences.ubc.ca/</u> <u>pesc2001</u>. You will be able to access the Internet and your e-mail provider at no cost from computers in the Woodward IRC Building. Full details will be available in your on-site registration package. For the best selection of accommodation on the University of British Columbia campus, we urge you to make your reservation soon.

Approximately 600 digests were submitted for PESC 2001. That maintains the recordbreaking submission level established last year in Ireland, and it both indicates consistently high

interest in PESC and provides high-quality technical content. PESC obviously generates substantial interest in both Europe and North America. About 375 (62 %) of the digests have been accepted for presentation, and as a new departure for PESC, 150 of these will be presented as posters in the ex-*Continued on page 9*

#### In This Issue

| President's Message 1                             |

|---------------------------------------------------|

| INTELEC <sup>®</sup> '01 Preview 1                |

| PESC® '01 Final Plans 1                           |

| APEC <sup>®</sup> '01 Recap 1                     |

| Quicker News Delivery 2                           |

| PESC® Call for Site Proposals 2                   |

| European Liaison 2                                |

| Automotive Workshop Report                        |

| Education Activities 3                            |

| PESC <sup>®</sup> '01 Flyer 4                     |

| Oh Danny Boy: the Story Behind 4                  |

| Tricks of Trade <sup>®</sup> : Solar Cell Model 5 |

| APEC® '02 Call for Papers 6                       |

| AdCom Meeting Minutes Summary . 7                 |

| COBEP '01 Call for Papers 8                       |

| ELECO '01 Call for Papers 10                      |

| Award Presentations 11                            |

| IEMDC '01 Preview 11                              |

| Meetings of Interest 12                           |

|                                                   |

## **Quicker News Delivery**

The Power Electronics Society News*letter* is available on the internet in electronic PDF format much sooner than hardcopies can be printed, labeled, and delivered by postal mail. To receive email notification when the newsletter is posted on the PELS server, go to http://www.pels.org/Mailing/ MailForm.html and add your name to the notification service list.

# **Book Reviews**

This issue has no book review because none were submitted. Please send the editor a short prioritized list of outstanding technical books that you would be willing to review and share with your colleagues.

#### **IEEE Power Electronics Society** Officers

Thomas Habetler, President Dean Patterson, V. P., Operations F. Dong Tan, V. P., Meetings Steven B. Leeb, Treasurer

#### http://www.pels.org

The IEEE Power Electronics Society Newsletter (ISSN 1054-7231) is published quarterly by the IEEE Power Electronics Society of the Institute of Electrical and Electronics Engineers, Inc. Headquarters: 3 Park Avenue, 17th Floor, NY 10016-5997. \$1.00 per member per year (included in Society fee) for each member of the Power Electronics Society. Postmaster: Send address changes to IEEE POWER ELECTRON-ICS SOCIETY NEWSLETTER, IEEE 445 Hoes Lane, Piscataway, NJ 08855-1331.

News items should be sent to: Gene Wester, Editor, PELS Newsletter, Jet Propulsion Laboratory, M/S 303-300, 4800 Oak Grove Drive, Pasadena, CA 91109-8099, USA; TEL: +1 818 354 3489; FAX: +1 818 393 4272; EMAIL: gwester@jpl.nasa.gov. Deadlines for copy are March 15, June 15, September 15 and December 15. Submission of items by email in plaintext format is preferred. Plain-text (straight ASCII) submissions on 3.5" diskettes are welcome, and should be accompanied by a backup printout. Fax submissions are acceptable, but are least desirable. Full-page calls for papers and announcements of PELS-sponsored conferences are welcome and should be sent as both high-quality hard copy and RTF format file.

The editor gratefully acknowledges the Jet Propulsion Laboratory for significant support of his editorial activities.

©2001 IEEE. Permission to copy without fee all or part of any material without a copyright notice is granted provided that the copies are not made or distributed for direct commercial advantage, and the title of the publication and its date appear on each copy. To copy material with a copyright notice requires special permission. Please direct all inquiries or requests to the IEEE Intellectual Property Rights Manager, TEL: +1 732 562 3966, FAX: +1 732 981 8062, EMAIL: copyrights@ieee.org

Periodicals Postage paid at New York NY.and at additional mailing offices. PRINTED IN THE U.S.A.

# Call for PESC<sup>®</sup> 2006 and **2007 Site Proposals**

The location of PESC 2006 will be decided at PESC 2001 in Vancouver. In keeping with tradition, the 2006 conference would be held normally at a location in the Far East/Australia (IEEE Region 10), and the 2007 conference would be held normally in North America/South America (Regions 1-7 or 9).

A proposal outline for 2006 should be submitted to the PESC Steering Committee via the PELS coordinator Bob Myers <body><body><body>bodybyMay31, 2001. The proposal should include: local conference facilities, name of proposed General Chair, and outline of budget. Each proposer for 2006 should plan to attend the PESC Steering Committee in Vancouver on Sunday June 17, 2001 and make a short presentation.

We are also interested in preliminary proposals for 2007. Further information may be obtained from the undersigned.

Prof. W.G. Hurlev Chair, PESC Steering Committee National University of Ireland Galway, Ireland Email: ger.hurley@niugalway.ie Phone: +353-91-512092 and 750493 or +353-91-524411 (switchboard) Fax: +353-91-750591 and 750588

#### **INTELEC 2001**

from pg 1 /www.pels.org) is a Technical Co-sponsor of INTELEC 2001.

INTELEC 2001 will be held at the Edinburgh International Conference Centre (EICC), an award winning conference venue, located in the heart of Edinburgh. The large exhibition will be held in the purpose-built air-conditioned exhibition hall of the Centre which offers easy access for exhibitors.

Edinburgh, the capital of Scotland, is world famous for it's castle and arts festival and has recently been awarded World Heritage Status. Scotland's attractions include the spectacular scenery, famous golf courses, Baronial Halls, whisky distilleries and tartan weaving. The conference centre itself is located within walking distance of a wide range of hotels, Princes Street with its superb shops, the ancient Castle and the Royal Mile in the Mediaeval old town.

Edinburgh International Airport is less than 20 minutes from the city centre and provides superb access to a worldwide network of flights. Rapid rail services to London and other UK cities, plus an excellent

### **European Liaison**

Effective January 1, Rik W. De Doncker became the European Liaison for PELS. The European Liaison serves as the interface between PELS and the European power electronics societies (mainly ESPC, EPE), universities, industry and potential authors for Society conferences. As member of the

EPE Executive Council. VDE and Past Chairman of the German Joint IAS-PELS Chapter, R. De Doncker is in a excellent position to explore stronger international cooperations between PELS, with

its IEEE sister societies (i.e. IAS, IES and PES), and European assocations and societies. It is anticipated that cooperations will ultimately lead to improved quality of our products, e.g. conferences. Motivation is guaranteed, as R. De Doncker will organize our very own PESC conference in the year 2004 in Aachen, Germany!

Rik W. De Doncker RWTH-Aachen ISEA Jaegerstrasse 17-19 D-52066 Aachen, Germany Tel.: +49 241 80 6920 Fax.: +49 241 67 505 Email: dedoncker@ieee.org

motorway system, provide easy access for travelers from any destination.

Each year more companions attend INTELEC. Companions and delegates will be offered a stimulating programme of visits including trips to the Borders, Royal Yacht Brittania, a whisky distillery, some castles, and the Kingdom of Fife.

Early indicators suggest that the conference will be a resounding success. Over 250 abstracts have been received, and all of the exhibition area has been sold. The ten main corporate sponsorships are all taken, although there are still some other sponsorship opportunities. The provisional programme will be available in July. To receive a copy, please register your interest with the INTELEC Secretariat below.

### **INTELEC** Secretariat

IEE Conference and Exhibition Services Savoy Place London UK, WC2R 0BL Tel: + 44 (0)20 7344 5472 Fax: +44 (0)20 7240 8830 Email: intelec@iee.org.uk http://conferences.iee.org/ INTELEC2001/

## Automotive Power Electronics Workshop Report

The Workshop on Power Electronics in Transportation, WPET 2000, was held December 5-6, 2000 at the Hilton Novi in Novi, Michigan. The 2000 workshop addressed the topic 42V Power Systems for the Next 100 Years and was sponsored by IEEE Power Electronics Society and IEEE Southeastern Michigan Section in cooperation with the Society of Automotive Engineers (SAE) and the MIT/Industry Consortium on Advanced Automotive Electrical/Electronic Components and Systems.

WPET 2000 was the 6<sup>th</sup> biennial workshop focusing on the power requirements of vehicles. The need for a higher voltage for the automotive primary power supply system has gained prominence within the last few years. WPET 2000 provided a focus specifically on the 42 V systems and components that are being pursued from industry consortiums, standards organizations, individual suppliers and vehicle manufacturers.

The two-day technical program was divided into five sessions: Infrastructure Issues and Architecture, Energy Management/ Conversion I & II, Semiconductors and Packaging, and 42V Subsystems. In addition to the fourteen papers that were presented, two panel discussions addressed the topics "Is 42V the real answer for increasing power demands in vehicles?" and "How will 42V systems impact semiconductors?"

The Keynote Luncheon Speaker was Dr. David Cole, the former Director of the Office for the Study of Automotive (OSAT) of the University of Michigan's Transportation Research Institute.

The workshop's focus and goal of attracting a limited but dedicated number of participants provided an informal environment conducive to interaction between presenters and attendees. While progress is being made towards a 42V standard, several challenges must be solved to have future vehicles capable of handling a 42V power bus.

Did you know ... that depending on the vehicle, every 10A of electric load reduces the fuel economy by 0.3 to 0.5 miles per gallon?

Randy Frank Chair, PELS Automotive Power Electronics Committee Email: <u>RandR118@aol.com</u>

### **Educational Activities**

I am very excited with the appointment to serve IEEE PELS as Educational Activities Committee Chair. It is my responsibility to work out with our members activities like development and review of proposals for educational programs, such as tutorials, seminars and short courses. It is also required in this position to provide liaison with IEEE and other professional educational organizations and staffs.

Power electronics is a key national need, essential for economic well being and security. Consequently, prospective students and the public at large need to be aware of the techno-

logical importance of power electronics by investing in new initiatives to promote the communication of technical information.

I come from an interdisciplinary educational background. I taught at the Department of Mechatronics at the University of Sao Paulo, Brazil, for several years. Now I am with Colorado School of Mines, Golden, Colorado, where their main mission is to provide a multidisciplinary education and research regimen at the intersection of traditional engineering, educating students for undertaking an Engineering Systems background. Power electronics has always fascinated me because it is the enabling technology that bonds such objectives to the industrial applications needs.

Serving now as IEEE PELS Educational Chair I want to emphasize the integration of power electronics educators, students and industry groups in valuable educational approaches. Such challenge can only be accomplished if you give me your feedback in how to further improve our policies and guidelines !

If you want to contribute in promoting videos based on your tutorials, publish tutorial summaries on this newsletter and make educational articles and self-study materials available in our web site, please send me an e-mail with your proposal and thoughts.

Marcelo Godoy Simoes Associate Professor Colorado School of Mines 1500 Illinois St. Golden, CO 80401-1887 Tel: +1 303 384-2350 Email: <u>msimoes@mines.edu</u>

### **APEC 2001**

#### from page 1

According to several longtime attendees, APEC 2001 was the "best ever," it provided "fantastic audio/visual equipment" to clearly see the materials being presented, and "everything worked." What the attendee does not see is the behind-the-scenes effort by our conference management, conference committee, and local hotel staff to anticipate every possible scenario and have a contingency plan in place. One example was the decision to expand the number of booths for our exhibitors. Our initial floor plan provided 132 booth spaces for this year's conference. Due to strong exhibitor demand, our conference management team and exhibits chairman John Bassett expanded the lavout to include 148 booths, 43 more than APEC 2000. Even with some cancellations we were successful in selling every booth space, setting another conference record. When you consider the current economy and our 10th consecutive year of selling out the exhibit hall, you can appreciate the "return on investment" which every exhibitor realizes from their participation at the APEC conference and exposition.

To monitor our performance with the exhibition aspect of APEC, three prizes were given out in our Tuesday evening drawings contingent on the response to a six-question survey. We continue to look for the "voice of the customer" with respect to our goal of continuous improvement in every aspect of APEC.

As one of the judges selected in counting the votes on questions relating to the best booth, best giveaway and happiest sales person, I can report that the ballot of one of our annual attendees contained manual punches, hanging chads and dimples. To protect the privacy of this individual, I will not give out Art's last name! Blue ribbons were given out and the ballot results were as follows: IR was selected for having the best booth, and Intersil was voted as having both the best giveaway (illuminating, clear, hard rubber balls) and happiest sales person. Three prizes were awarded for filling out the survey. Third prize, a Palm Pilot, was won by Gim Soon Wan, and second prize, a portable Panasonic DVD player, was won by Dennis Stephens. Doug McIlvoy, won first prize, a Compag 12XL300 Notebook Computer. In reality, considering the unlimited "free" food and beverages served in the exhibit hall, we were all winners.

The APEC conference is an annual gathering where academic and industry leaders demonstrate the true benefits of *Continued on page 7*

# **CONFERENCE ANNOUNCEMENT**

32<sup>nd</sup> Annual

# Power Electronics Specialists Conference June 17-21, 2001

# Vancouver, BC, Canada

http://www.conferences.ubc.ca/pesc2001

**PESC**<sup>®</sup> provides an international forum for power-electronics experts to present and discuss papers and new ideas on the latest advances and forward-looking topics in this fast-evolving field.

- Technical program consists of 379 papers (229 oral and 150 poster presentations)

- Six Professional Education Tutorials

- 🛠 NEW 🛠 Industrial Exhibits

- $rac{1}{3}$  NEW  $rac{1}{3}$  Poster sessions with 150 poster presentations

- 🕆 NEW 🖈 Special Student Session with Cash Prizes

- 🖈 NEW 🌣 Student "Wall Crawl" Design Competition with Cash Prizes

- · Active social program for participants and guests, featuring regional tours, music, art, and food

- Presentations of the Newell, Richard M. Bass, and Distinguished Service Awards

For additional information see the related article in this issue, visit the website given above, or contact the Secretariat.

PESC 2001 Secretariat UBC Conference Centre 5961 Student Union Boulevard Vancouver, BC, Canada V6T 2C9 Telephone: +1 604 822 1050 Facsimile: +1 604 822 1069 Email: <u>PESC2001@housing.ubc.ca</u>

#### PESC is sponsored by the IEEE Power Electronics Society

# *Oh Danny Boy*: the Story Behind the Performance

Some have suggested that it was a bit bold for an Australian to stand up and sing a very famous Irish song in Ireland. There's a story behind my performance of *Danny Boy* at PESC 00 in Galway, Ireland (see photograph in the October 2000 issue of the *IEEE PELS Newsletter*).

I first met Gerry Hurley at PESC 89 in Milwaukee. We met again at PESC '90 in San Antonio Texas, and decided to have a Guinness together in an Irish Tavern in the Hyatt hotel in San Antonio (a true mix of cultures).

There was a pianist there offering to play for anybody who was game to stand up

and sing, a sort of live Karaoke, but it was all Irish songs. After a few Guinness's, and some urging (René Spee was also there as I remember) I weakened, and did "Danny Boy".

Somebody came up to our table just after and asked what part of Ireland I came from. I replied "I'm not Irish, but my manager, (indicating Gerry Hurley), is". From that time on he's been my "manager", and has got me to sing in a few other Irish pubs in a few other part of the world.

He booked me for the Galway gig as soon as he was appointed general Chair PESC 2000. Thus it was an obligation. I strung him on, saying "probably not", "is the band any good?" "I don't have the words" etc. He wasn't sure I was going to do it until I actually stood up and did it. It was really an acknowledgement of a very good friend, to thank him for his long-term support, and for his excellent conference organization.

Now I'm thinking of what odd performance I can lean on him to do when he come to PESC '02 in Cairns. Anybody got any suggestions?

> Dean Patterson Research Professor, Electrical Engineering University of South Carolina Columbia SC 29208 Ph: (803)777-7362 Fax: (803) 777-8045 Email: patterson@ieee.org

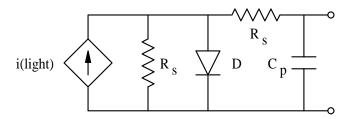

# Tricks of the Trade: A Simple Solar Cell Model®

One of the most important "tricks" in control system design is knowing how to model a system or device with just enough complexity but not too much. Does the model have enough detail to actually work? Does it really need to take absolutely everything into account? It is very difficult to determine how much detail is needed, especially since the overall behavior can depend on internal details.

Alternative energy sources such as solar cells or fuel cells can

be very complex to model. For a solar cell, a full physical model must account for the quantum efficiency as photons of certain wavelengths split hole-electron pairs and lead to output current. Light intensity, wavelength, and temperature effects all require detailed model information. Even the cell capacitance is a nonlinear function of a wide range of parameters.

For the purposes of power conversion, the internal physics are much less important. For example, in an outdoor-mounted panel, light intensity can be used with little regard for wavelength details (presumably sunlight is "white enough" to either work or not). A panel should be used to produce the maximum possible energy, so only at the maximum point is the capacitance really relevant. There are internal leakages and drops. In the end, a very simple circuit model, shown in Fig. 1, will support almost all the details we might need to design a power converter for a solar cell. This circuit is based on tests of a 10 cm full-wafer silicon crystal solar cell. The current source is approximately a linear function of intensity (the value is about 3.1 A under "standard one sun" conditions). The diode represents the physical behavior of the cell itself as a P-N junction. The capacitor (which I should have chosen based on lab ac measurements) reflects the depletion capacitance of this large structure at nominal output voltage of about 0.5 V. The model does give a correct picture of how current splits in parallel and series connections. It also gives a good model for losses, and gives excellent insight into how the solar cell will function in a converter. I often use many of these models in series to represent a complete panel.

Figure 1. Solar cell model for power conversion.

The most common types of fuel cells, as it turns out, show rather similar behavior. In a fuel cell, the possible output current is a function of fuel flow. A fuel cell shows a current-limiting behavior just like a solar cell, although at a slightly higher voltage. The biggest distinction is in the dynamics. In a solar cell, the internal current changes almost instantly when the light intensity changes. Fuel cells have much higher capacitance because of large surface area, and follow changes to the input energy source much more slowly. There are internal pumps and compressors to regulate pressure, and all the equipment requires many seconds to come to steady state. This kind of behavior can be modeled as a slow time constant between the fuel flow command and the internal current source. By analogy to a solar cell, this is equivalent to the internal current changing slowly over several seconds when the illumination changes. We have modeled such behavior with a slow R-C time constant at the control terminals of the current source. Even though these models are extremely simple, they support the key design needs of a power electronic system.

A PSPICE netlist is given for convenience.

| SOLAR CELL MODEL AND TEST CIRCUIT<br><sup>*</sup> P. T. Krein, 2001<br><sup>*</sup> Includes both a circuit model and a current-source test of<br><sup>*</sup> a silicon solar cell, 10 cm size.<br><sup>*</sup> Set up for temperature and illumination steps for testing.<br><sup>*</sup> For these cells, the nominal output current is about 3 A.<br><sup>*</sup> The internal source is slightly higher (resistive drops.)<br><sup>*</sup><br>param imax=3.1<br>.step temp list 0 20 40 60 80<br><sup>*</sup> The internal current is approximately a linear function of<br><sup>*</sup> White light illumination intensity.<br><sup>*</sup> .step param imax 0.775 3.1 0.775<br>.tran 10ms 4s 0 10m<br><sup>*</sup> Here is the circuit model. Node 99 is the output.<br><sup>*</sup> Variables: isun — the photon-produced internal current<br><sup>*</sup> rsun — parallel leakage resistance<br><sup>*</sup> rs — output series resistance drop<br><sup>*</sup> dsun — the internal diode that limits voltage.<br><sup>*</sup> cparallel — the inherent parallel capacitance of a<br><sup>*</sup> 10 cm diode<br>isun 0 97 dc {imax}<br>rsun 97 0 10<br>rs 99 98 0.5<br>cparallel 90 100n<br>dsun 97 0 dio<br>vsense 97 98 dc 0<br>.model dio D(Is=2n Rs=0.001)<br><sup>*</sup> Now, impose an external load current ramp to get the voltage<br><sup>*</sup> vs. current trace. Notice that when the current exceeds the<br><sup>*</sup> internal value, it will drive the voltage to extreme negative values.<br>itest 99 0 pwl(0 0 4 4)<br><sup>*</sup> To see the curves, plot v(97). Limit the vertical scale to (0,1).<br><sup>*</sup> The horizontal scale can be read in amps since the test current<br><sup>*</sup> has a slope of 1 A/s.<br>.end | C C                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>*The internal source is slightly higher (resistive drops.)</li> <li>*</li> <li>.param imax=3.1</li> <li>.step temp list 0 20 40 60 80</li> <li>*The internal current is approximately a linear function of</li> <li>*white light illumination intensity.</li> <li>*.step param imax 0.775 3.1 0.775</li> <li>.tran 10ms 4s 0 10m</li> <li>*Here is the circuit model. Node 99 is the output.</li> <li>*Variables: isun — the photon-produced internal current</li> <li>* rsun — parallel leakage resistance</li> <li>* rs — output series resistance drop</li> <li>* dsun — the internal diode that limits voltage.</li> <li>* cparallel — the inherent parallel capacitance of a</li> <li>* 10 cm diode</li> <li>isun 0 97 dc {imax}</li> <li>rsun 97 0 10</li> <li>rs 99 98 0.5</li> <li>cparallel 99 0 100n</li> <li>dsun 97 0 dio</li> <li>vsense 97 98 dc 0</li> <li>.model dio D(Is=2n Rs=0.001)</li> <li>*Now, impose an external load current ramp to get the voltage</li> <li>*vs. current trace. Notice that when the current exceeds the</li> <li>*internal value, it will drive the voltage to extreme negative values.</li> <li>itest 99 0 pwl(0 0 4 4)</li> <li>*To see the curves, plot v(97). Limit the vertical scale to (0,1).</li> <li>*The horizontal scale can be read in amps since the test current</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                     | *P. T. Krein, 2001<br>*Includes both a circuit model and a current-source test of<br>*a silicon solar cell, 10 cm size.<br>*Set up for temperature and illumination steps for testing. |

| <ul> <li>step temp list 0 20 40 60 80</li> <li>*The internal current is approximately a linear function of</li> <li>*white light illumination intensity.</li> <li>*.step param imax 0.775 3.1 0.775</li> <li>tran 10ms 4s 0 10m</li> <li>*Here is the circuit model. Node 99 is the output.</li> <li>*Variables: isun — the photon-produced internal current</li> <li>* rsun — parallel leakage resistance</li> <li>* rs — output series resistance drop</li> <li>* dsun — the internal diode that limits voltage.</li> <li>* cparallel — the inherent parallel capacitance of a</li> <li>* 10 cm diode</li> <li>isun 0 97 dc {imax}</li> <li>rsun 97 0 10</li> <li>rs 99 98 0.5</li> <li>cparallel 99 0 100n</li> <li>dsun 97 0 dio</li> <li>vsense 97 98 dc 0</li> <li>model dio D(Is=2n Rs=0.001)</li> <li>*Now, impose an external load current ramp to get the voltage</li> <li>*vs. current trace. Notice that when the current exceeds the</li> <li>*internal value, it will drive the voltage to extreme negative values.</li> <li>itest 99 0 pwl(0 0 4 4)</li> <li>*To see the curves, plot v(97). Limit the vertical scale to (0,1).</li> <li>*The horizontal scale can be read in amps since the test current</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                        |

| <ul> <li>*The internal current is approximately a linear function of</li> <li>*white light illumination intensity.</li> <li>*.step param imax 0.775 3.1 0.775</li> <li>tran 10ms 4s 0 10m</li> <li>*Here is the circuit model. Node 99 is the output.</li> <li>*Variables: isun — the photon-produced internal current</li> <li>* rsun — parallel leakage resistance</li> <li>* rs — output series resistance drop</li> <li>* dsun — the internal diode that limits voltage.</li> <li>* cparallel — the inherent parallel capacitance of a</li> <li>* 10 cm diode</li> <li>isun 0 97 dc {imax}</li> <li>rsun 97 0 10</li> <li>rs 99 98 0.5</li> <li>cparallel 99 0 100n</li> <li>dsun 97 0 dio</li> <li>vsense 97 98 dc 0</li> <li>.model dio D(Is=2n Rs=0.001)</li> <li>*Now, impose an external load current ramp to get the voltage</li> <li>*vs. current trace. Notice that when the current exceeds the</li> <li>*internal value, it will drive the voltage to extreme negative values.</li> <li>itest 99 0 pwl(0 0 4 4)</li> <li>*To see the curves, plot v(97). Limit the vertical scale to (0,1).</li> <li>*The horizontal scale can be read in amps since the test current</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                        |

| <ul> <li>*white light illumination intensity.</li> <li>*.step param imax 0.775 3.1 0.775</li> <li>tran 10ms 4s 0 10m</li> <li>*Here is the circuit model. Node 99 is the output.</li> <li>*Variables: isun — the photon-produced internal current</li> <li>* rsun — parallel leakage resistance</li> <li>* rs — output series resistance drop</li> <li>* dsun — the internal diode that limits voltage.</li> <li>* cparallel — the inherent parallel capacitance of a</li> <li>* 10 cm diode</li> <li>isun 0 97 dc {imax}</li> <li>rsun 97 0 10</li> <li>rs 99 98 0.5</li> <li>cparallel 99 0 100n</li> <li>dsun 97 0 dio</li> <li>vsense 97 98 dc 0</li> <li>.model dio D(Is=2n Rs=0.001)</li> <li>*Now, impose an external load current ramp to get the voltage</li> <li>*vs. current trace. Notice that when the current exceeds the</li> <li>*internal value, it will drive the voltage to extreme negative values.</li> <li>itest 99 0 pwl(0 0 4 4)</li> <li>*To see the curves, plot v(97). Limit the vertical scale to (0,1).</li> <li>*The horizontal scale can be read in amps since the test current</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                        |

| <ul> <li>*.step param imax 0.775 3.1 0.775</li> <li>tran 10ms 4s 0 10m</li> <li>*Here is the circuit model. Node 99 is the output.</li> <li>*Variables: isun — the photon-produced internal current</li> <li>* rsun — parallel leakage resistance</li> <li>* rs — output series resistance drop</li> <li>* dsun — the internal diode that limits voltage.</li> <li>* cparallel — the inherent parallel capacitance of a</li> <li>* 10 cm diode</li> <li>isun 0 97 dc {imax}</li> <li>rsun 97 0 10</li> <li>rs 99 98 0.5</li> <li>cparallel 99 0 100n</li> <li>dsun 97 0 dio</li> <li>vsense 97 98 dc 0</li> <li>.model dio D(Is=2n Rs=0.001)</li> <li>*Now, impose an external load current ramp to get the voltage</li> <li>*vs. current trace. Notice that when the current exceeds the</li> <li>*internal value, it will drive the voltage to extreme negative values.</li> <li>itest 99 0 pwl(0 0 4 4)</li> <li>*To see the curves, plot v(97). Limit the vertical scale to (0,1).</li> <li>*The horizontal scale can be read in amps since the test current</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                        |

| <ul> <li>*Here is the circuit model. Node 99 is the output.</li> <li>*Variables: isun — the photon-produced internal current</li> <li>* rsun — parallel leakage resistance</li> <li>* ns — output series resistance drop</li> <li>* dsun — the internal diode that limits voltage.</li> <li>* cparallel — the inherent parallel capacitance of a</li> <li>* 10 cm diode</li> <li>isun 0 97 dc {imax}</li> <li>rsun 97 0 10</li> <li>rs 99 98 0.5</li> <li>cparallel 99 0 100n</li> <li>dsun 97 0 dio</li> <li>vsense 97 98 dc 0</li> <li>.model dio D(Is=2n Rs=0.001)</li> <li>*Now, impose an external load current ramp to get the voltage</li> <li>*vs. current trace. Notice that when the current exceeds the</li> <li>*internal value, it will drive the voltage to extreme negative values.</li> <li>itest 99 0 pwl(0 0 4 4)</li> <li>*To see the curves, plot v(97). Limit the vertical scale to (0,1).</li> <li>*The horizontal scale can be read in amps since the test current</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                        |

| <ul> <li>*Variables: isun — the photon-produced internal current</li> <li>* rsun — parallel leakage resistance</li> <li>* rs — output series resistance drop</li> <li>* dsun — the internal diode that limits voltage.</li> <li>* cparallel — the inherent parallel capacitance of a</li> <li>* 10 cm diode</li> <li>isun 0 97 dc {imax}</li> <li>rsun 97 0 10</li> <li>rs 99 98 0.5</li> <li>cparallel 99 0 100n</li> <li>dsun 97 0 dio</li> <li>vsense 97 98 dc 0</li> <li>.model dio D(Is=2n Rs=0.001)</li> <li>*Now, impose an external load current ramp to get the voltage</li> <li>*vs. current trace. Notice that when the current exceeds the</li> <li>*internal value, it will drive the voltage to extreme negative values.</li> <li>itest 99 0 pwl(0 0 4 4)</li> <li>*To see the curves, plot v(97). Limit the vertical scale to (0,1).</li> <li>*The horizontal scale can be read in amps since the test current</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                        |

| <ul> <li>rsun — parallel leakage resistance</li> <li>rs — output series resistance drop</li> <li>dsun — the internal diode that limits voltage.</li> <li>cparallel — the inherent parallel capacitance of a</li> <li>10 cm diode</li> <li>isun 0 97 dc {imax}</li> <li>rsun 97 0 10</li> <li>rs 99 98 0.5</li> <li>cparallel 99 0 100n</li> <li>dsun 97 0 dio</li> <li>vsense 97 98 dc 0</li> <li>model dio D(Is=2n Rs=0.001)</li> <li>*Now, impose an external load current ramp to get the voltage</li> <li>*vs. current trace. Notice that when the current exceeds the</li> <li>*internal value, it will drive the voltage to extreme negative values.</li> <li>itest 99 0 pwl(0 0 4 4)</li> <li>*To see the curves, plot v(97). Limit the vertical scale to (0,1).</li> <li>*The horizontal scale can be read in amps since the test current</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                        |

| <ul> <li>rs — output series resistance drop</li> <li>dsun — the internal diode that limits voltage.</li> <li>cparallel — the inherent parallel capacitance of a</li> <li>10 cm diode</li> <li>isun 0 97 dc {imax}</li> <li>rsun 97 0 10</li> <li>rs 99 98 0.5</li> <li>cparallel 99 0 100n</li> <li>dsun 97 0 dio</li> <li>vsense 97 98 dc 0</li> <li>.model dio D(Is=2n Rs=0.001)</li> <li>*Now, impose an external load current ramp to get the voltage</li> <li>*vs. current trace. Notice that when the current exceeds the</li> <li>*internal value, it will drive the voltage to extreme negative values.</li> <li>itest 99 0 pwl(0 0 4 4)</li> <li>*To see the curves, plot v(97). Limit the vertical scale to (0,1).</li> <li>*The horizontal scale can be read in amps since the test current</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                        |

| <ul> <li>dsun — the internal diode that limits voltage.</li> <li>cparallel — the inherent parallel capacitance of a</li> <li>10 cm diode</li> <li>isun 0 97 dc {imax}</li> <li>rsun 97 0 10</li> <li>rs 99 98 0.5</li> <li>cparallel 99 0 100n</li> <li>dsun 97 0 dio</li> <li>vsense 97 98 dc 0</li> <li>.model dio D(Is=2n Rs=0.001)</li> <li>*Now, impose an external load current ramp to get the voltage</li> <li>*vs. current trace. Notice that when the current exceeds the</li> <li>*internal value, it will drive the voltage to extreme negative values.</li> <li>itest 99 0 pwl(0 0 4 4)</li> <li>*To see the curves, plot v(97). Limit the vertical scale to (0,1).</li> <li>*The horizontal scale can be read in amps since the test current</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                        |

| <ul> <li>* 10 cm diode</li> <li>isun 0 97 dc {imax}</li> <li>rsun 97 0 10</li> <li>rs 99 98 0.5</li> <li>cparallel 99 0 100n</li> <li>dsun 97 0 dio</li> <li>vsense 97 98 dc 0</li> <li>.model dio D(Is=2n Rs=0.001)</li> <li>*Now, impose an external load current ramp to get the voltage</li> <li>*vs. current trace. Notice that when the current exceeds the</li> <li>*internal value, it will drive the voltage to extreme negative values.</li> <li>itest 99 0 pwl(0 0 4 4)</li> <li>*To see the curves, plot v(97). Limit the vertical scale to (0,1).</li> <li>*The horizontal scale can be read in amps since the test current</li> <li>*has a slope of 1 A/s.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                        |

| isun 0 97 dc {imax}<br>rsun 97 0 10<br>rs 99 98 0.5<br>cparallel 99 0 100n<br>dsun 97 0 dio<br>vsense 97 98 dc 0<br>.model dio D(Is=2n Rs=0.001)<br>*Now, impose an external load current ramp to get the voltage<br>*vs. current trace. Notice that when the current exceeds the<br>*internal value, it will drive the voltage to extreme negative values.<br>itest 99 0 pwl(0 0 4 4)<br>*To see the curves, plot v(97). Limit the vertical scale to (0,1).<br>*The horizontal scale can be read in amps since the test current<br>*has a slope of 1 A/s.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                        |

| rsun 97 0 10<br>rs 99 98 0.5<br>cparallel 99 0 100n<br>dsun 97 0 dio<br>vsense 97 98 dc 0<br>.model dio D(Is=2n Rs=0.001)<br>*Now, impose an external load current ramp to get the voltage<br>*vs. current trace. Notice that when the current exceeds the<br>*internal value, it will drive the voltage to extreme negative values.<br>itest 99 0 pwl(0 0 4 4)<br>*To see the curves, plot v(97). Limit the vertical scale to (0,1).<br>*The horizontal scale can be read in amps since the test current<br>*has a slope of 1 A/s.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                        |

| rs 99 98 0.5<br>cparallel 99 0 100n<br>dsun 97 0 dio<br>vsense 97 98 dc 0<br>.model dio D(Is=2n Rs=0.001)<br>*Now, impose an external load current ramp to get the voltage<br>*vs. current trace. Notice that when the current exceeds the<br>*internal value, it will drive the voltage to extreme negative values.<br>itest 99 0 pwl(0 0 4 4)<br>*To see the curves, plot v(97). Limit the vertical scale to (0,1).<br>*The horizontal scale can be read in amps since the test current<br>*has a slope of 1 A/s.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                        |

| cparallel 99 0 100n<br>dsun 97 0 dio<br>vsense 97 98 dc 0<br>.model dio D(Is=2n Rs=0.001)<br>*Now, impose an external load current ramp to get the voltage<br>*vs. current trace. Notice that when the current exceeds the<br>*internal value, it will drive the voltage to extreme negative values.<br>itest 99 0 pwl(0 0 4 4)<br>*To see the curves, plot v(97). Limit the vertical scale to (0,1).<br>*The horizontal scale can be read in amps since the test current<br>*has a slope of 1 A/s.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                        |

| ysense 97 98 dc 0<br>.model dio D(Is=2n Rs=0.001)<br>*Now, impose an external load current ramp to get the voltage<br>*vs. current trace. Notice that when the current exceeds the<br>*internal value, it will drive the voltage to extreme negative values.<br>itest 99 0 pwl(0 0 4 4)<br>*To see the curves, plot v(97). Limit the vertical scale to (0,1).<br>*The horizontal scale can be read in amps since the test current<br>*has a slope of 1 A/s.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                        |

| <ul> <li>.model dio D(Is=2n Rs=0.001)</li> <li>*Now, impose an external load current ramp to get the voltage</li> <li>*vs. current trace. Notice that when the current exceeds the</li> <li>*internal value, it will drive the voltage to extreme negative values.</li> <li>itest 99 0 pwl(0 0 4 4)</li> <li>*To see the curves, plot v(97). Limit the vertical scale to (0,1).</li> <li>*The horizontal scale can be read in amps since the test current</li> <li>*has a slope of 1 A/s.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                                                                                                                                                                      |

| *Now, impose an external load current ramp to get the voltage<br>*vs. current trace. Notice that when the current exceeds the<br>*internal value, it will drive the voltage to extreme negative values.<br>itest 99 0 pwl(0 0 4 4)<br>*To see the curves, plot v(97). Limit the vertical scale to (0,1).<br>*The horizontal scale can be read in amps since the test current<br>*has a slope of 1 A/s.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | vsense 97 98 dc 0                                                                                                                                                                      |

| <ul> <li>*vs. current trace. Notice that when the current exceeds the</li> <li>*internal value, it will drive the voltage to extreme negative values.</li> <li>itest 99 0 pwl(0 0 4 4)</li> <li>*To see the curves, plot v(97). Limit the vertical scale to (0,1).</li> <li>*The horizontal scale can be read in amps since the test current</li> <li>*has a slope of 1 A/s.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                        |

| <ul> <li>*internal value, it will drive the voltage to extreme negative values.</li> <li>itest 99 0 pwl(0 0 4 4)</li> <li>*To see the curves, plot v(97). Limit the vertical scale to (0,1).</li> <li>*The horizontal scale can be read in amps since the test current</li> <li>*has a slope of 1 A/s.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                        |

| itest 99 0 pwl(0 0 4 4)<br>*To see the curves, plot v(97). Limit the vertical scale to (0,1).<br>*The horizontal scale can be read in amps since the test current<br>*has a slope of 1 A/s.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                        |

| *To see the curves, plot v(97). Limit the vertical scale to (0,1).<br>*The horizontal scale can be read in amps since the test current<br>*has a slope of 1 A/s.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0 0                                                                                                                                                                                    |

| *has a slope of 1 A/s.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | •                                                                                                                                                                                      |

| .ena                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •                                                                                                                                                                                      |