Overview of Quality and Reliability Issues in the National Technology Roadmap for Semiconductors SEMATECH and the SEMATECH logo are registered service marks of SEMATECH, Inc.

Product names and company names used in this publication are for identification purposes only and may be trademarks or service marks of their respective companies

# Overview of Quality and Reliability Issues in the National Technology Roadmap for Semiconductors

Technology Transfer # 98013448A-TR SEMATECH January 30, 1998

| Abstract: | This document is an update to the 1994 Quality and Reliability Roadmap issued in support of the   |

|-----------|---------------------------------------------------------------------------------------------------|

|           | 1994 National Technology Roadmap for Semiconductors. This report revisits the challenges,         |

|           | constraints, priorities, and research needs pertaining to quality and reliability issues. It also |

|           | provides key project proposals that must be implemented to address concerns about reliability     |

|           | attainment and defect learning. An expanded section on test-to-test, diagnostics, and failure     |

|           | analysis; an edited version of the Product Analysis Forum Roadmap; and an appendix containing a   |

|           | draft report highlighting reliability issues is included.                                         |

- **Keywords:** Design, Failure Analysis, Packaging, Quality Management, Reliability, Reliability Modeling, Silicon

- Authors: Dino Barpoulis

- Approvals:Alex Oscilowski, Director, Advanced Technology<br/>Dan McGowan, Technical Information Transfer Team Leader

# **Table of Contents**

| 1 | EXECUTIVE SUMMARY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                                                                                             |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| 2 | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                                                                             |

| 3 | ROADMAP OVERVIEW: QUALITY AND RELIABILITY ISSUES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2                                                                                             |

| 4 | OVERVIEW OF SILICON TECHNOLOGY RELIABILITY CONSTRAINTS.         4.1 Reliability of Gate Dielectrics.         4.2 Electromigration         4.3 Electrostatic Discharge         4.4 Multilevel Metal/Dielectric Integrity.         4.5 Hot Carrier Injection (HCI).         4.6 Wafer Charging/Antenna Effects/Ultra-Thin Oxides         4.7 Increase in Max Tj         4.8 Soft Error/Single-Event Upsets.         4.9 Defectivity, Cleanliness         4.10 Noise Margin/Coupling         4.11 Latch-up         4.12 Leakage Isolation         4.13 Tools for Reliability Checking         4.14 Package Induced Failures.         4.15 Cost Effective Reliability and Qualification.         4.16 Mixed Signal Requirements for Transistor Matching         4.17 Performance/Power/Reliability Tradeoffs         4.18 Key Project Proposals | 5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>12<br>12<br>12<br>12<br>13<br>13<br>13<br>13<br>13 |

| 5 | <ul> <li>IC PACKAGING TECHNOLOGY ISSUES/CONSTRAINTS</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 19<br>19<br>21<br>22<br>23<br>24                                                              |

|   | 5.8 Modeling for Age, Wearout, and Correlation to Environmental Stress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                               |

| 6 | <ul> <li>SILICON DESIGN TECHNOLOGY CONSTRAINTS</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 27<br>28<br>28<br>28<br>29<br>29<br>30                                                        |

|    |            | Section Draft                                                                                                                             | 49 |

|----|------------|-------------------------------------------------------------------------------------------------------------------------------------------|----|

| AF | PEN        | DIX National Technology Roadmap for Semiconductors Reliability Focus                                                                      |    |

|    | 8.8        | Conclusion                                                                                                                                | 45 |

|    | 8.7        | Future Activities                                                                                                                         |    |

|    | 0 -        | 8.6.1 Significance of the National Roadmap to the FA Community                                                                            |    |

|    | 8.6        | Discussion                                                                                                                                |    |

|    | 0 -        | 8.5.5 Root Cause Determination                                                                                                            |    |

|    |            | 8.5.4 Physical/Chemical Characterization                                                                                                  |    |

|    |            | 8.5.3 Sample Preparation/ Defect Tracing                                                                                                  |    |

|    |            | 8.5.2 Localize/Characterize Faults.                                                                                                       |    |

|    |            | 8.5.1 Assure Failure Validity                                                                                                             |    |

|    | 8.5        | Failure Analysis as a Process                                                                                                             |    |

|    | 8.4<br>8.5 | Roadmap Generation Process                                                                                                                |    |

|    | 8.3<br>8.4 | Purpose and Scope                                                                                                                         |    |

|    |            |                                                                                                                                           |    |

|    | 8.2        | Introduction                                                                                                                              |    |

| 0  | 8.1        | Summary                                                                                                                                   |    |

| 8  | DDC        | DDUCT ANALYSIS FORUM ROADMAP                                                                                                              |    |

|    |            | 7.2.15 Constraint #15: Room Temperature Test                                                                                              |    |

|    |            | 7.2.14 Constraint #14: Product Tracking                                                                                                   |    |

|    |            | 7.2.13 Constraint #13: Interface Requirements                                                                                             |    |

|    |            | 7.2.12 Constraint #12: Thermal, Noise, and Power Requirements                                                                             |    |

|    |            | 7.2.11 Constraint #11: Handling Large Test Programs                                                                                       |    |

|    |            | 7.2.10 Constraint #10: Cost Of Test                                                                                                       |    |

|    |            | <ul><li>7.2.9 Constraint #9: Delay Fault Testing</li></ul>                                                                                |    |

|    |            | 7.2.8 Constraint #8: Test Vector Generation                                                                                               |    |

|    |            | 7.2.7 Constraint #7: Tester Precision                                                                                                     | 36 |

|    |            | <ul><li>7.2.6 Constraint #6: Stuck Fault Coverage</li></ul>                                                                               |    |

|    |            | 7.2.5 Constraint #5: I <sub>DDQ</sub> Required                                                                                            |    |

|    |            | 7.2.4 Constraint #4: Self Test                                                                                                            |    |

|    |            | <ul><li>7.2.3 Constraint #3: Application versus Test Program Correlation</li></ul>                                                        |    |

|    |            | <ul><li>7.2.1 Constraint #1: Diagnosability and Fandre Finarysis.</li><li>7.2.2 Constraint #2: Test Coverage and Known Good Die</li></ul> |    |

|    |            | 7.2.1 Constraint #1: Diagnosability and Failure Analysis Technology Constraints                                                           |    |

|    | 7.1        | Discussion of Test, Diagnostics, and Failure Analysis Technology Constraints                                                              |    |

| /  | 7.1        | ST, DIAGNOSTICS, AND FAILURE ANALYSIS TECHNOLOGY CONSTRAINTS.<br>Introduction                                                             |    |

| 7  | TES        | T DIAGNOSTICS AND FAILURE ANALYSIS TECHNOLOGY CONSTRAINTS                                                                                 | 22 |

|    |            | 6.2.15 Constraint #15: Cost Effectiveness                                                                                                 |    |

|    |            | 6.2.14 Constraint #14: Decoupling Capacitors                                                                                              |    |

|    |            | 6.2.13 Constraint #13: Intradie, Interdie Variation                                                                                       |    |

|    |            | 6.2.12 Constraint #12: Soft Error Rate                                                                                                    |    |

|    |            | 6.2.11 Constraint #11: Routing for Maximum Reliability for Large Blocks                                                                   |    |

|    |            | 6.2.10 Constraint #10: Design for At-Speed Test                                                                                           |    |

|    |            | 6.2.9 Constraint #9: Low Voltage                                                                                                          |    |

|    |            | 6.2.8 Constraint #8: ESD 4KV Minimum                                                                                                      |    |

|    |            | 6.2.7 Constraint #7: Die level Burn-in                                                                                                    | 30 |

# List of Figures

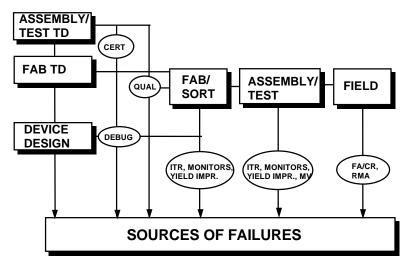

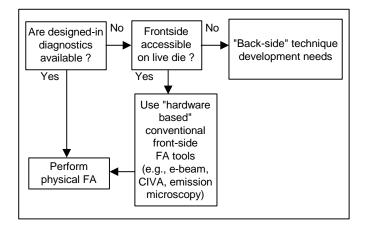

| Figure 1 | Sources of Failures in Relation to Device Life Cycle | 40 |

|----------|------------------------------------------------------|----|

| Figure 2 | Flip Chip FA Flow                                    | 43 |

# List of Tables

| Table 1  | Prioritization of Reliability Related Technology Constraints (Year 2000<br>Projection) | 4    |

|----------|----------------------------------------------------------------------------------------|------|

| Table 2  | Effects of Charging on Ultrathin Oxides                                                | . 10 |

| Table 3  | Project Overview: Reliability Of Thin Oxides in Direct Tunneling Regime                | . 15 |

| Table 4  | Project Overview: CAD Reliability Assessment Tools for Electromigration                | . 18 |

| Table 5  | Prioritized Matrix of Silicon Design Technology Constraints                            | . 28 |

| Table 6  | Key Failure Analysis Drivers Extracted from the Roadmap                                | . 42 |

| Table 7  | Year 2000 Base Customer Expectations                                                   | . 46 |

| Table 8  | Base Customer Expectations at 85C                                                      | . 47 |

| Table 9  | Q&R Learning/Customer Expectancy                                                       | . 48 |

| Table 10 | Overall Technology Requirements                                                        | . 51 |

| Table 11 | Potential Solutions                                                                    | . 52 |

| Table 12 | Difficult Challenges                                                                   | . 54 |

# Acknowledgements

SEMATECH wishes to thank the following persons and organizations for their contributions to this document and the work leading up to it:

### **Reliability Technology Advisory Board**

| Advanced Micro Devices | Richard Blish, senior MTS, Reliability Engineering                                                                                               |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | Kola Olasupo, section manager, Q&R Engineering                                                                                                   |

| Digital Equipment      | Bob Deysher, group quality manager                                                                                                               |

| Hewlett-Packard        | Dennis Eaton, reliability manager                                                                                                                |

| IBM                    | Bharat Bhargava                                                                                                                                  |

|                        | George Prokop                                                                                                                                    |

|                        | Hugh Sweeney, manager, Memory and Special QA                                                                                                     |

| Intel                  | Steve Huber, Assembly TD, Q&R manager                                                                                                            |

|                        | Jose Maiz, QA Program manager                                                                                                                    |

| Lucent                 | Carl Peridier, IC reliability engineer                                                                                                           |

| Motorola               | Nick Lycoudes, Reliability Engineering manager                                                                                                   |

| National Semiconductor | Josip Huljev, Director, Corporate Reliability and SEMATECH Quality Council sponsor                                                               |

| Rockwell               | James Pau, Reliability and F/A manager                                                                                                           |

| Texas Instruments      | Julie England, VP Semicondluctor Group and Quality Council sponsor                                                                               |

|                        | Don Denton, Director, Reliability Services                                                                                                       |

|                        | Gail Heinen, Sr. technical staff member                                                                                                          |

|                        | Joe McPherson, TI Fellow                                                                                                                         |

|                        | Tim Rost, Productization Reliability manager                                                                                                     |

| SEMATECH               | P.K. Vasudev, Acting co-director, Strategic Technology Office<br>Chi Shih Chang (IBM), senior technologist                                       |

| Consultant             |                                                                                                                                                  |

|                        | Dino Barpoulis, co-chair, Quality Council                                                                                                        |

|                        | oratories and Semiconductor Research Corporation                                                                                                 |

| Livermore              | Mike Fluss, deputy director                                                                                                                      |

| Los Alamos             | Galen Straub, group leader                                                                                                                       |

| NIST                   | Harry Schafft, physicist                                                                                                                         |

| Sandia                 | Ted Dellin, Reliability Technology Program Manager<br>Paul Dressendorfer, Multi-Chip Applications Manager<br>Jerry Soden, Senior Technical Staff |

| SRC                    | Bill Atkins, Director of Interconnect Sciences<br>Jim Freedman, Vice President                                                                   |

|                                            | Analysis Forum                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Intel                                      | Richard Clark, Silicon Debug Laboratory manager                                                                                                                                                                                                                                                                                                                                               |

| IBM                                        | Dave Vallett, advisory engineer                                                                                                                                                                                                                                                                                                                                                               |

|                                            | RTAB Subgroups                                                                                                                                                                                                                                                                                                                                                                                |

| Silicon                                    |                                                                                                                                                                                                                                                                                                                                                                                               |

| Packaging                                  | Jose Maiz, leader (Intel), Bill Atkins (SRC), Bob Deysher (DEC),<br>Joe McPherson (TI), James Pau (Rockwell), Tappan Pramanik<br>(NSC),, Galen Straub (Los Alamos), Ted Dellin (Sandia), Kola<br>Olasupo (AMD), Carl Peridier (Lucent), Harry Schafft (NIST)<br>Don Denton, leader (TI), Richard Blish (AMD), Ron Bracken<br>(SRC), Dennis Eaton (HP), Gail Heinen (TI), Steve Huber (Intel), |

| Design                                     | John Jackson (NSC), Nick Lycoudes (Motorola)<br>Josip Huljev leader (NSC), leader Keith Burgess (TI) Wonjae<br>Kang (Intel) Allen Righter (Sandia), Charles Smith (IBM)                                                                                                                                                                                                                       |

| Test, Diagnostics, and<br>Failure Analysis | Dino Barpoulis, leader (consultant), Richard Clark (Intel), Nick<br>Lycoudes (Motorola), Jerry Soden (Sandia), Hugh Sweeney (IBM),<br>Dave Vallett (IBM)                                                                                                                                                                                                                                      |

Additional thanks also are due to the following persons for assistance in preparing the *Product Analysis Forum Roadmap* that appears within this document:

| Sudhakar M. Kudva, Intel Corp.                | Bob Ash, Motorola                                  |

|-----------------------------------------------|----------------------------------------------------|

| Richard Clark, Digital Equipment corp.        | Joseph Serpiello, American Telephone and Telegraph |

| Dave Vallett, International Business Machines | Ken Huffman, SEMATECH                              |

| Ted Hasegawa, National Semiconductor Corp.    | Larry Wagner, Texas Instruments                    |

| Glen Gilfeather, Advanced Micro Devices       | Matt Thayer, Advanced Micro Devices                |

| Seshu Pabbisetty, Texas Instruments           | Saeed Kazmi, Advanced Micro Devices                |

| Robert Shreeve, Hewlett-Packard               | Dick Ross, International Business Machines         |

Technology Transfer # 98013448A-TR

### **1 EXECUTIVE SUMMARY**

This document is an update to the 1994 *Quality and Reliability Roadmap* (Q&R Roadmap) that was issued in support of the 1994 *National Technology Roadmap for Semiconductors* (National Roadmap). This report revisits the challenges, constraints, priorities, and research needs pertaining to Q&R issues. It also introduces key project proposals that must be implemented to address concerns over reliability attainment and defect learning.

Key findings in this report include the following:

- Outlooks vary on what it will take to satisfy customers in the year 2000 for quality and reliability.

- Continued stretching of existing processes and rapid introduction of significantly changed materials illustrate the need for a new reliability strategy. This should include new projects and funding to establish understanding of mechanisms of failure, models, incorporation of models into the design systems; and metrics for reliability defects in process and test as part of the equipment cost of ownership (COO).

- Scaling of reliability models with the projected changes in technology described by the National Roadmap is an issue that presents several excellent research opportunities.

- Customer application requirements in more severe environments continue to escalate the need for improved electrostatic discharge (ESD) protection. The technology direction of more wiring per chip and increased pad and pin counts raises the question of when limits on ESD will be reached.

- Serious gaps exist in TCAD and CAD tools for product designs that do not adequately simulate the effects of failure mechanisms. Exploration is needed in the development of methodologies for TCAD and CAD tools to allow determination of performance (i.e., electromigration).

- Worldwide demand continues to drive faster, lighter, smaller, cost-effective systems for packaging ICs. Current approaches eliminate a packaging level through chip-to-board connection or smaller chip scale packaging. These pose two general issues: reliability expectations in customer use environments and tools for package reliability analysis.

Emphasis on defect learning will be found in this update through an expanded section on test-totest, diagnostics, and failure analysis and inclusion of an edited version of the *Product Analysis Forum Roadmap*. Also, reliability issues are highlighted in a draft report in the appendix.

### 2 INTRODUCTION

In the 1994 issue of the Q&R Roadmap, significant challenges in reliability technology were explored and reliability was scaled overall against yield learning. To meet the 5X level of reliability improvement expected by customers between 1994 and 1998, defect density (defects/chip) learning must be accelerated beyond the 3.9X projected, with required yields of 95% compared to the 84% yields planned. The significance of the challenge in defect density learning is illustrated by considering the high resistive contact via defect by itself. Current designs number contact vias in the tens of millions, with that number scaled upwards in the strategic time frame. Even if the current reliability levels are retained (notwithstanding the

extrapolated 1.0–0.1 failure units [FITs] in the strategic time frame) as future reliability requirements, there can be no room for high resistive contact via defects. The via process must be perfect to meet yield, reliability, and cost objectives. This challenge stretches existing process capabilities and is compounded by additional challenges and opportunities raised by the introduction of new materials and processes. An adjunct group was formed by the Reliability Technical Advisory Board (RTAB) during this update period to tackle the challenge of electrical overstress (EOS)/ESD. Formation of an ESD benchmark/standards group is anticipated in 1997.

# **3 ROADMAP OVERVIEW: QUALITY AND RELIABILITY ISSUES**

A key issue carried forward from the 1994 Q&R Roadmap is the shortfall in defect density learning for yield, compared to improvements expected by customers in quality and reliability from 1992–1998. Outlooks vary on what it will take to satisfy year 2000 customers for quality and reliability (see Table 7 and Table 9). Some believe customer expectations for quality and reliability can be achieved by maintaining the current levels in test escapes (shipped product quality level [SPQL]) early life (EL), and end of life (EOL) failure rates at year-end 2000. Others project continued reduction in meeting the customer's challenge of 1.0–0.1 FITs in the strategic time frame. What is evident is that the projections made in 1994 for 1997 have been achieved in test escapes and EOL, but not in EL reliability. Indeed, for EL the learning curve has flattened out, with no improvement between 1992 and 1997.

Whether continued learning to 1.0–0.1 FITs or no further learning to meet customer satisfaction in quality and reliability is accepted as the objective, either expectation will be difficult to achieve with the continued stretching of existing processes and the rapid introduction of the most significant change in material set that the industry has seen (Cu, Low k dielectrics, oxi-nitride gates, etc.). A new reliability strategy, projects, and funding will be needed to establish understanding of mechanisms of failure, models, incorporation of models into the design systems, and metrics for reliability defects in process and test as part of the equipment COO.

An example of a particular defect type, contact/interlevel vias, illustrates how complexity will place extreme requirements on process perfection. Already, this process must achieve tens of millions of vias per chip without high interface resistance to meet yield, quality, and reliability objectives. This problem is compounded by limitations in testability, diagnosability, and failure analysis for process and design learning. That is why the test section in the 1994 Q&R Roadmap has been expanded here to include test, diagnostics, and failure analysis roadmaps.

Scaling of reliability models with the projected changes in technology described by the National Roadmap presents several excellent research opportunities. The National Roadmap shows gate oxides decreasing to 4.5 nm in 1998 and to 3.4 nm in 2004, with fields increasing in excess of 5.0 MV/cm. Susceptibility to gate dielectric breakdown will increase, and the gate conduction mechanism will change from Fowler-Nordhiem tunneling to direct tunneling when gate oxide thickness falls below 35–40 Å. There is a strong need to understand the reliability implications of these changes to assess the true cost of making them.

Customer application requirements in more severe environments continue to escalate the need for improved ESD protection. The technology direction of more wiring per chip and increased pad and pin counts raises the question of when limits on ESD will be reached. No method of comparative measurement is in place for the industry other than the existing Human Body Model

(HBM), Charged Device Model (CDM), and Machine Model (MM). The industry needs a standard for comparative measurement, metrics, and models that fit within a technology family.

Serious gaps exist in technology computer-aided design (TCAD) and CAD tools for product designs that do not adequately simulate the effects of failure mechanisms. Exploration is needed in the development of methodologies for TCAD and CAD tools to allow determination of performance (i.e., electromigration). Several university R&D programs funded through Semiconductor Research Corporation (SRC) show considerable promise for establishing the physical and electrical behavioral models needed. These programs must be brought to fruition and integrated with design systems that can be deployed commercially.

Worldwide demand continues to drive faster, lighter, smaller, cost-effective systems for packaging ICs. Current approaches eliminate a packaging level through chip-to-board connection or smaller chip scale packaging. These pose two general issues: reliability expectations in customer use environments and tools for package reliability analysis.

Research projects are proposed to address the opportunities of top reliability issues.

### 4 OVERVIEW OF SILICON TECHNOLOGY RELIABILITY CONSTRAINTS

Future silicon reliability constraints will be driven by technology scaling, process complexity, new material introductions, device demands and customer requirements. Technology scaling will impact reliability by increasing electric fields across dielectrics as well as increasing stresses on all elements of the structure. Process complexity will increase the risk of damage to circuits, raising the risk of latent damage. New materials are planned to improve performance, but their behaviors have not been adequately characterized and modeled. Future designs require more performance, resulting in increased temperatures and reduced reliability margins. Finally, customers are demanding improved performance and functionality without compromising quality and reliability.

The challenge will be to model and predict silicon reliability concurrently with the increase in process complexity, rapid technology scaling, new material introduction, while assuring customers that product requirements are being met. Ideally, reliability scaling models, similar to technology scaling models, should be developed and verified.

Table 1 describes the significant silicon reliability constraints that must be addressed. Of major importance to the industry are the following:

- Gate dielectric reliability

- Electromigration

- Electrostatic discharge

- Multilevel interconnects

- Hot carrier injection

- Antenna, wafer charging effects

- Junction temperature increase

- Soft error/single event upset

This list is incomplete, and other items identified in this report also require appropriate attention. It is key that the industry identify, characterize, and control potential failure mechanisms so that reliable products can be manufactured and delivered to customers.

|                                                      | Silicon                |    |    |    |    |    |       |    |    |     |

|------------------------------------------------------|------------------------|----|----|----|----|----|-------|----|----|-----|

|                                                      | A B C D E F G H I Tota |    |    |    |    |    | Total |    |    |     |

| Gate Dielectric Reliability                          | 1                      | 4  | 1  | 3  | 5  | 1  | 1     | 5  | 4  | 25  |

| Electromigration                                     | 5                      | 5  | 3  | 6  | 6  | 5  | 3     | 13 | 1  | 47  |

| ESD                                                  | 6                      | 6  | 8  | 2  | 8  | 3  | 5     | 9  | 2  | 49  |

| Multi Level Metal/Dielectric Integrity               | 12                     | 8  | 10 | 5  | 1  | 10 | 2     | 3  | 8  | 59  |

| Hot Carriers                                         | 9                      | 1  | 2  | 8  | 12 | 6  | 4     | 11 | 7  | 60  |

| Defectivity, Cleanliness                             | 4                      | 9  | 4  | 1  | 15 | 7  | 13    | 1  | 12 | 66  |

| Wafer Charging/Antenna Effects/Ultra<br>Thin Oxides  | 2                      | 17 | 15 | 16 | 4  | 2  | 7     | 2  | 3  | 68  |

| Noise Margin/Coupling                                | 13                     | 2  | 5  | 4  | 7  | 9  | 14    | 12 | 6  | 72  |

| Latch-up                                             | 15                     | 7  | 9  | 10 | 13 | 4  | 6     | 4  | 11 | 79  |

| Leakage Isolation                                    | 8                      | 14 | 6  | 11 | 10 | 11 | 9     | 10 | 15 | 94  |

| Tools for Reliability Checking                       | 3                      | 12 | 17 | 17 | 9  | 8  | 12    | 7  | 9  | 94  |

| Pkg. Induced Failures                                | 14                     | 13 | 14 | 15 | 3  | 15 | 10    | 8  | 10 | 102 |

| Soft Error (Single Error Upset)                      | 11                     | 16 | 16 | 13 | 2  | 14 | 16    | 14 | 5  | 107 |

| Cost Effective Reliability &<br>Qualification        | 7                      | 11 | 7  | 14 | 14 | 17 | 8     | 17 | 13 | 108 |

| Mixed Signal Requirements for<br>Transistor Matching | 17                     | 15 | 13 | 2  | 16 | 12 | 11    | 6  | 17 | 109 |

| Perf./Power/Reliability Trade-offs                   | 10                     | 10 | 11 | 7  | 11 | 16 | 15    | 15 | 16 | 111 |

| Increasing Max. Tj                                   | 16                     | 3  | 12 | 9  | 17 | 13 | 17    | 16 | 14 | 117 |

| Table 1 | Prioritization of Reliability Related Technology Constraints (Year 2000 |

|---------|-------------------------------------------------------------------------|

|         | Projection)                                                             |

1 = Highest Priority

#### 4.1 Reliability of Gate Dielectrics

#### **Problem Statement**

The susceptibility to gate dielectric breakdown will increase because of the following:

- 1. Thinning of the dielectric

- 2. Small increases (after correcting for band bending) in the gate electric field

- 3. Increase in the gate area/die (especially if large decoupling capacitors are needed)

- 4. Increased sensitivity to post-gate processing

Furthermore, as the gate oxide thickness is scaled below  $\sim$ 50 Å, the gate conduction mechanism will change from Fowler-Nordhiem tunneling to direct tunneling. This could impact, positively or negatively, the reliability of the gate dielectrics.

#### **Key Issues**

These issues include the following:

- 1. Measuring time-dependent dielectric breakdown (TDDB) requires large sample sizes, yet may not measure the failure mechanism that occurs during normal device operation. AC measurement capabilities are very limited. Without statistically valid, meaningful characterization, it will be difficult to address the other key issues.

- 2. There is still uncertainty about the model for field acceleration of dielectric breakdown under DC biases. Modeling of high frequency effects is less developed. Validated physical and statistical models are required to predict reliability and to design screens.

- 3. The transition to direct tunneling could introduce new failure modes. Scaled technologies will have less tolerance for drifts in transistor parameters.

- 4. Gate dielectric reliability will be increasingly sensitive to the complete process flow, not just to the gate oxidation step.

- 5. Other issues include diffusion through the dielectric from the p-channel poly gates and accurately accounting for band bending in determining the electric field in the dielectric.

#### **Research Needs**

These needs are as follows:

- 1. Understand and control the impact of post-gate processing on gate oxide reliability.

- 2. Develop rapid methods of qualifying gate dielectrics.

- 3. Increase the use of TCAD tools.

- 4. Develop practical methods to do statistically valid characterization gate oxide reliability that accurately reflect the performance of real devices.

- 5. Characterize the impact of direct tunneling on dielectric breakdown and investigate if any new failure modes (e.g., instabilities) are introduced.

- 6. Develop predictive DC and AC models for gate oxide reliability.

# 4.2 Electromigration

### **Problem Statement**

Present and planned reductions of metal-interconnect dimensions are reducing and making more uncertain the margin for error in designing and manufacturing metal interconnects of adequate reliability. Significant efforts are needed to optimize and measure reliability performance.

### **Key Issues**

Materials engineering and building-in reliability approaches are required to optimize existing and developing aluminum-based metallization systems and associated processes and materials. The approaches involve methods to understand and utilize the interactions of the constituent materials, processing materials, processes, thermal history, and processing equipment. They require methods to identify and control aspects that affect interconnect reliability in, for example, the design of the metal system and the design and operation of the processes and processing equipment used to deposit and treat the metal and associated interlayer-dielectric films.

Gaps and deficiencies exist in the tool set for measuring reliability of interconnects, e.g., in evaluating vias, characterizing the effect of pulsed-current stresses, and characterizing susceptibility to stress voiding. Gaps also exist in characterizing the early reliability of the interconnect system. To help fill these gaps requires a better understanding of the effect of accelerated stress conditions on the metal system so that more accurate estimates can be made of the actual acceleration of stress test, and assurances given that the conditions of the stress test are related to use conditions.

Copper-based metallizations offer the advantages of lower resistivity and higher potential resistance to electromigration if processing problems can be overcome. The decision to use such metallizations will depend partly on how well aluminum-based systems can continue to be optimized. Work is needed first to solve problems related to copper deposition, containment, and integration with adjacent materials.

# **Research Needs**

These needs include the following:

- 1. Develop materials engineering and building-in reliability approaches.

- 2. Identify and control parameters of the deposition process that affect metal film quality, e.g., film temperature, material purity, and substrate texture.

- 3. Develop reliability models for aluminum-based vias.

- 4. Develop measurement (standard) methods and structures for characterizing reliability of vias, susceptibility to stress voiding, pulsed-current stresses, and early reliability of metal systems.

- 5. Assess the impact of copper interconnect and its potential resistance to electromigration.

# 4.3 Electrostatic Discharge

# **Problem Statement**

The continued Human Body Model requirement on ESD robustness of >2KV, the Machine Model requirement of >200V, and the Charged Device Model of >1KV will constrain the ability to scale to smaller geometries and to operate devices at lower voltages. New protection circuit

# SEMATECH

designs must account for process technology variations and design rel cases to different fabrication facilities. Additionally, with increasing pad counts and higher density circuits, space available for effective ESD will be at a premium.

#### **Key Issues**

Silicon technology strongly influences ESD capability. Designs that function well in one technology do not necessarily show similar performance in newer submicron processes. Circuit elements must withstand heating effects, sink large amounts of current, and remain undamaged by high electric fields.

Key process parameters that influence ESD performance must be identified and characterized. It is critical that transistor engineering understand the impact on junction profiles and spacing for ESD and other wearout mechanisms such as hot carriers. As gate oxide thicknesses are reduced, it is important that dielectric breakdown voltages are not exceeded before ESD devices turn on.

Unfortunately, the implementation of ESD protection is iterative. Capability of the process is characterized on test structures that provide design guides for protection circuitry. This approach, which relies on empirical results rather than using accurate simulation tools, does not allow for robust technology development.

Also limiting ESD issues has been the lack of consensual standards and test methods. Differences in tester capabilities and their calibration can result in different ESD threshold voltage values. Test methods also influence results, based on which combination of pins is selected for ESD testing.

#### **Research Needs**

These include the following:

- 1. Develop predictive methods that can be used to evaluate the impact of technology variation on the effectiveness of ESD circuits.

- 2. Develop better models and methods for predicting robustness of circuits under different test methods (HBM, MM, CDM) and the correlation between these techniques.

- 3. Develop methodology and design for circuits in submicron technologies that must operate in multivoltage environments.

- 4. Develop specifications for test equipment capability and calibration standards.

### 4.4 Multilevel Metal/Dielectric Integrity

#### **Problem Statement**

Aggressive scaling and increased performance requirements of semiconductor devices are producing the following results:

- 1. An increased number of metal interconnect layers will impose additional constraints to the selection of materials and their integration.

- 2. Smaller via/interconnect line feature sizes, often involving many different materials and interfaces within a 1µm3, will aggravate interface problems.

- 3. New materials such as Low k dielectrics and low resistance metals to achieve the projected performance targets are unlisted.

#### Technology Transfer # 98013448A-TR

4. Increased die sizes and novel assembly options such as C4 may result in increased mechanical and thermal stresses.

#### **Key Issues**

Key issues include the following:

- 1. The impact of a high mechanical stress environments on the performance and reliability of silicon semiconductor devices.

- 2. The reliability of new dielectrics and low resistance metals as interconnects.

#### **Research Needs**

Research needs are as follows:

- 1. Improved experimental and modeling techniques for materials characterization (thin film mechanical properties and interface adhesion strengths) in the micron/submicron regime, including in and around vias.

- 2. Improved modeling of metal migration/void formation under thermomechanical stresses and thermomechanical/electromigration combined stresses.

- 3. Reliability of new dielectrics, low resistance metals under thermomechanical and current/voltage environments.

- 4. Improved experimental and modeling techniques to evaluate the intrinsic properties of packaging materials and their adhesion/interface properties among themselves and to the silicon die.

- 5. Modeling capability for the assembled package/silicon system, with focus on large die and advanced packaging methods, such as C4.

- 6. Basic understanding of thin film knowledge and its measurement.

# 4.5 Hot Carrier Injection (HCI)

### **Problem Statement**

Aggressive performance requirements of MOS devices will require continual channel-length reduction and improved source-drain engineering. Even with simultaneous reduction in power supply voltages as devices scale down, hot carrier effect is most pronounced with the reduction of channel length and thinning of gate dielectric. Hot carrier effect can impact both device design and technology development as it lowers device current drive and thus limits device speed performance. Further, scaled technology will be sensitive to small drift in parameters.

### **Key Issues**

Key issues are as follows:

1. Accurate hot carrier degradation modeling and simulations are critical, since overestimation of this effect can put unnecessary constraints on device design and prevent it from realizing its maximum speed potential, whereas underestimation of this effect can jeopardize device long-term reliability. Accurate modeling is essential to correlate wafer-level hot carrier reliability testing with actual operating conditions in order to optimize device performance without reducing device reliability.

2. The conventional Isub(max) measurement techniques are not sufficient. A unified, industrywide, built-in reliability approach is needed. If the impact of HCI-induced degradation is first observed during process development and product qualification, it will be too late. This information must be built into design libraries. Additionally, an industry-wide accepted technique is needed.

### **Research Needs**

These needs include the following:

- 1. Correlate wafer level-hot carrier reliability testing with actual deep submicron device operating conditions at low power supply voltages (2.5 volts and below).

- 2. Establish common AC requirements for HCI.

- 3. Develop simulation models to account for the combined effects of, and coupling among, various hot carrier degradation mechanisms. (Should a new figure of merit be established?)

- 4. Establish design and processing rules and guidelines for hot carriers, with pertinent software tools to validate and check for adherence to these rules and guidelines.

- 5. The effect of HCI degradation on sub-0.3 μm PMOS devices over operating condition is becoming pronounced. As such, better understanding of HCI model for PMOS devices are needed.

### 4.6 Wafer Charging/Antenna Effects/Ultra-Thin Oxides

#### **Problem Statement**

Gate oxide and transistor scaling will require a better understanding and a reduction of the effects of process-induced charging damage. High power and high density plasmas, with the effects of such schemes as magnetic confinement, will only enhance the charging issue. Common processing steps such as plasma enhanced deposition, etching, ashing, and implantation may become significant contributors to wafer charging.

### **Key Issues**

The charging concern is driven by two primary issues:

1. *Processing Issue*: Thin oxides are expected to be less tolerant to wafer charging. For example, if the poly (or contacting metal) charges to the point where the field in the gate oxide reaches 10 Mv/cm, severe damage can occur to the gate oxide. Table 2 indicates how ultrathin oxides will become less tolerant to charging.

| Тох   | Charging Voltage Required to<br>Produce Severe Damage to Gate Oxide |

|-------|---------------------------------------------------------------------|

| 200 Å | 20 V                                                                |

| 120 Å | 12 V                                                                |

| 90 Å  | 9 V                                                                 |

| 60 Å  | 6 V                                                                 |

| 45 Å  | >4.5 V (1998-Roadmap)                                               |

| 35 Å  | >3.5 V (2004 Roadmap)                                               |

#### Table 2Effects of Charging on Ultrathin Oxides

2. Design Issue: The widely used design scheme for antenna protection (diode protection) is rapidly becoming ineffective. When the antenna ratio (area of thick-oxide/area of thin gate oxide) exceeds a critical value (~ 100/1), the designer must tie the gate to a diode for protection. The diode provides full protection (independent of polarity of charging) only if the diode in parallel with the gate oxide can break down before the 10 Mv/cm across the oxide is reached. For diodes that break down at 10 V, the diode can provide protection only for oxides >100 Å. Thus, for certain process steps, standard diode protection may not be sufficient protection for <100 Å gate oxides.</p>

### **Research Needs**

Research needs are as follows:

- 1. In situ equipment charging monitoring techniques

- 2. Novel charge neutralization techniques

- 3. Novel antenna protection design schemes

- 4. Magnetic confinement of plasmas (need for better understanding of physics)

- 5. Neutral beam etching (etch rate versus charging tradeoffs)

- 6. Uniformity of plasma etching versus charging tendency

# 4.7 Increase in Max Tj

### **Problem Statement**

Current 100 MHz devices are expected to generate about 9 W at 3.3 V operating voltage. For a 150 MHz device, one would expect about 12.5 W at 3.3 V. If the operating voltage is lowered to about 2.5 V, generated power is effectively lowered to about 10.0 W, which still is higher than the previous generation (100 MHz at 3.3 V) by 1.0 W. Thus, one has a faster part at lower voltage while generating the same amount of power as the prior generation. With future technologies (projecting to year 2000), the number of transistors and frequencies will scale up, and both will induce increased power consumption; only voltage will be scaled down. Will voltage be reduced fast enough to control power consumption? No, judging by the simple example above, which did not even include an increase in the number of transistors.

### **Key Issues**

Key issues are as follows:

- 1. Power generated will scale up faster with frequency than operating voltage can/will be reduced.

- 2. An increase in power means increased in Tj max. Device characteristics definitely would be impacted, as would diode breakdown voltages and (in the worst case) maybe even latch sensitivity. Designers would have to design the part over a wider temperature range.

- 3. Much more efficient thermal modules would be needed for power dissipation.

### **Research Needs**

Research needs are as follows:

- 1. Research in chip/package manufacturing/design

- 2. Exploration of the use of finite element analysis to determine heat flow path in multilevel metallization structures

- 3. Study of the effect of increasing layer of metallization on Tj max, and the effect of self-induced heating of upper layers of metallization on electromigration

# 4.8 Soft Error/Single-Event Upsets

#### **Problem Statement**

The downward scaling of the power supply is expected to continue to be driven by improvements in the performance/power ratio. The susceptibility of memory circuits and internal microprocessor caches to single-event upsets/software errors is expected to increase dramatically with decreased Vcc.

### **Key Issues**

Key issues include memory and logic considerations are as follows:

- 1. Memory devices depend on storing a charge in the cell during the writing operation sufficient to be reliably detected during the reading (sensing) operation. It is well known that ionization-producing charged particles such as alpha particles (emitted from trace amounts of uranium and thorium found in the ultra-large-scale integration [ULSI] or packaging materials) can induce charge loss in the cell (data state upset). More recently, it has been shown that cosmic rays (the high energy neutron component) can have a similar effect on memories. The latter mechanism is difficult to prevent and may enhance the need for error correction.

- 2. Although error detection/correction is common in memory systems, it may impose significant performance and/or density penalties for caches in microprocessors. Furthermore, aggressive scaling of Vcc, along with dramatic reductions in capacitance needed for very high speed logic operation, raise the question of the single-event upset/software error susceptibility of logic circuits.

Research needs are as follows:

- 1. Improved detection capability for ionizing particle emissions from ULSI and packaging materials. Detection capability of at least 0.001 alpha/cm2\*hr is needed.

- 2. Improved physics understanding of soft error/soft error upset (SE/SEU) due to cosmic rays, modeling of such physics, and ideas for device hardness

- 3. Development of appropriate cosmic ray measurement techniques for acceleration factor determination

- 4. Improved methodologies for both accelerated and non-accelerated measurement of the SEU/SE susceptibility of memory and logic circuits

- 5. Development of efficient simulators to model SE/SEU and evaluate the susceptibility of specific circuits

- 6. Design (non-error correction) solutions for SE/SEU upsets

- 7. Materials solutions for SE/SEU upsets

### 4.9 Defectivity, Cleanliness

#### **Problem Statement**

Clean processes are key to developing and maintaining process control. They are critical to ensuring that wearout phenomena do not significantly occur during the useful life of the component and that defect densities are at acceptable levels. The projections for increased density, increased die size, and customer expectations of reduced reliability fallout all require an accelerated reduction in defect density.

### 4.10 Noise Margin/Coupling

### **Problem Statement**

The reduction in the power supply, together with tighter timing requirements (performance improvement) and increased noise deriving from switching very high currents are expected to severely limit noise margins. Capacitive coupling between adjacent nodes also can have severe yield or reliability implications. Examples are signal crosstalk and device stressing at voltages that exceed the power supply.

### 4.11 Latch-up

### **Problem Statement**

Scaling requirements commonly result in increased immunity to latch-up. The high increase in the on-chip currents involved may result in increased parasitic resistance voltage drops or increased impact ionization currents, potentially compromising latch-up immunity.

### 4.12 Leakage Isolation

### **Problem Statement**

Attempts to reduce transistor leakage currents in the subthreshold regions can be effected by silicon reliability mechanisms such as HCI. In particular, changes in parameters such as drain

# SEMATECH

current in off state (Idoff) need to be modeled and understood in terms of carrier trapping and interface trap generation.

# 4.13 Tools for Reliability Checking

### **Problem Statement**

Tools based on modeling of failure mechanisms such as HCI, electromigration (EM), TDDB, etc., should be available for reliable use of future CMOS transistors and interconnect schemes. Rapid identification is required for situations where use conditions exceed reliable operation.

# 4.14 Package Induced Failures

### **Problem Statement**

Mechanical and thermal stresses due to coefficient of thermal expansion (CTE) mismatches between mold compounds and silicon can impact chip functionality and performance. Appropriate mechanical models need to be developed to account for interactions between the package and silicon.

# 4.15 Cost Effective Reliability and Qualification

# **Problem Statement**

Rapid introduction of new technologies is increasing time pressure on qualifying processes that meet reliability requirements. Given the higher cost of manufacturing at this introduction phase, material costs (especially in finished die form) contribute significantly to the overall cost of qualification. New methodologies and approaches need to be developed that not only reduce overall qualification costs, but also meet timelines for technology introduction.

# 4.16 Mixed Signal Requirements for Transistor Matching

### **Problem Statement**

The required mix signal output is dependent on multiple transistors being matched with the appropriate characteristics. Models should be developed that accurately predict output behaviors based on nonlinear transistor characteristics.

# 4.17 Performance/Power/Reliability Tradeoffs

### **Problem Statement**

At a constant voltage, performance increases at the expense of increased power and reduced reliability. Tools should be developed to help assess potential process changes in terms of transistors and interconnect performance, chip power dissipation (and temperature increase), and increased contribution of failure mechanisms (e.g., HCI, TDDB, latch-up, etc.) to overall chip reliability.

# 4.18 Key Project Proposals

# **Project Summary**

Project Name: Reliability Of Thin Oxides in Direct Tunneling Regime

### Technology Transfer # 98013448A-TR

Project No.: TBD

Thrust: TBD

ST & Sandia Project Leaders: TBD

### Summary of Problem and Alignment with the National Roadmap

The National Roadmap shows that the thickness of gate oxides will decrease to 4.5 nm in 1998 and to 3.4 nm in 2004, with sustained electric field increasing to over 5.0 MV/cm. Both requirements will lead to failure regimes (direct tunneling will be first) of which little is known. Therefore, there is a strong need to study the reliability implications so that the true cost of making these changes can be predicted.

# Approach

To meet the need for predicative reliability models in these new failure regimes, this project will address the following:

- Industry will produce side-by-side capacitors (with different areas), transistors and standard evaluation circuits with oxide thickness between 6 and 3 nm.

- Sandia National Laboratories will characterize the defect level, wafer-level reliability (WLR) and long-term TDDB, transistor stability and HCI.

- Sandia will develop a statistical model and a field acceleration model from the data.

- Industry will perform life tests on corresponding standard evaluation circuits (SEC), and results will be compared with the test structure data.

# Project Objectives and Benefits

These are as follows:

- Identification of any new failure models, or discontinuities in existing failure modes, resulting from the transition from direct substrate to gate tunneling

- Fast, meaningful, standardized methods to qualify the reliability of thin oxide processes

- Predictive oxide reliability models that will allow maximizing performance by confidently reducing reliability safety margins

- Ability to benchmark oxide reliability

| Objective                                                                    | Task                                                                                             | <b>Performance Metrics</b>                                                                               | Deliverables                                                                  | Due                    | \$K |

|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------|-----|

| 1.<br>Characterization of<br>thin oxide<br>capacitors                        | 1. Industry<br>supplies capacitors<br>with multiple<br>thickness                                 | Capacitor with oxide thickness<br>of 6 nm, 4.5 nm, and 3.4 nm                                            | SEMATECH<br>companies supply<br>capacitors                                    | +6 mo<br>from<br>start |     |

|                                                                              | 2. Characterization<br>at Sandia of<br>supported<br>capacitors                                   | <ol> <li>CV, V Ramp, TDDB<br/>measurements</li> <li>Failure analysis of failed<br/>capacitors</li> </ol> | Sandia documents<br>results                                                   | +12<br>mo              |     |

|                                                                              | 3. Data analyzed by Sandia                                                                       | <ol> <li>Gate current vs. field</li> <li>TDDB distribution</li> <li>WLR to TDDB</li> </ol>               | Sandia documents results                                                      | +15<br>mo              |     |

| 2.<br>Transistor<br>reliability                                              | 1. Industry<br>supplies transistors<br>splits processed<br>with capacitors                       | Transistors with different oxide thickness                                                               | Capacitors/<br>transistors<br>manufactured by<br>SEMATECH<br>member companies | +6 mo                  |     |

|                                                                              | 2. Sandia performs<br>pre-stress<br>transistors<br>characterization                              | <ol> <li>Transistor characterized</li> <li>DC stressing of transistors</li> </ol>                        | Sandia documents<br>transistor<br>characterization                            | +12<br>mo              |     |

| 3.<br>Industry evaluation<br>of long term<br>reliability of<br>corresponding | 1. Process SEC on<br>same wafers with<br>transistors and<br>capacitors                           | SEC circuits with different oxide thickness                                                              | Industry processes<br>SEC                                                     | +13<br>mo              |     |

| Standard<br>Evaluation Circuit                                               | 2. Do long-term<br>life test                                                                     | Test circuits                                                                                            | Document results                                                              |                        |     |

|                                                                              | 3. Failure analysis on all failures                                                              | Failure modes identified on circuits                                                                     | Document results                                                              | +24<br>mo              |     |

|                                                                              | 4. Correlate with<br>failure rates and<br>failure types fund<br>in transistors and<br>capacitors | Correlated SEC data with capacitor and transistor data                                                   | Document<br>correlation                                                       | +24<br>mo              |     |

|                                                                              |                                                                                                  |                                                                                                          |                                                                               | +24<br>mo              |     |

Table 3Project Overview: Reliability Of Thin Oxides in Direct Tunneling Regime

| Objective                                                                                | Task                                                                                                      | Performance Metrics                   | Deliverables                                                         | Due                    | \$K |  |  |  |

|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------------|------------------------|-----|--|--|--|

| 4.<br>Developing<br>predictive models                                                    | 1. Modeling of<br>gate current<br>leakage                                                                 | Gate current model developed          | Document gate<br>current leakage<br>models                           | +30<br>mo              |     |  |  |  |

|                                                                                          | <ul><li>2. Modeling of<br/>TDDB</li><li>3. Modeling of<br/>HCI and transistor<br/>instabilities</li></ul> | TDDB model developed                  | Document TDDB<br>model<br>Document HCI<br>model                      | +30<br>mo<br>+30<br>mo |     |  |  |  |

| 5.<br>Development of<br>rapid standardized<br>thin oxide<br>reliability<br>qualification | 1. Specification of test structures                                                                       | Test structure designed               | Document details of<br>oxide reliability test<br>structures          | +36<br>mo              |     |  |  |  |

|                                                                                          | 2. Specification of test method                                                                           | Test method developed                 | Document test<br>methods of oxide<br>reliability rest<br>structures  | +36<br>mo              |     |  |  |  |

|                                                                                          | 3. Specification of data analysis                                                                         | Data analysis procedures<br>developed | Document data<br>analysis procedures<br>for oxide test<br>structures | +36<br>mo              |     |  |  |  |

| Universities, suppliers, partners and dependencies: \$1050K total                        |                                                                                                           |                                       |                                                                      |                        |     |  |  |  |

#### **Project Summary**

Ratification date: 1995 SETEC (EDSC) statement of work (SOW)

Rev. date: N/A

Project Name: CAD Reliability Assessment Tools for Electromigration

Project No.: TBD

Thrust: TBD

SEMATECH & Sandia Project Leaders: TBD

#### Summary of Problem and Alignment with National Roadmap

There are serious gaps in CAD tools for product design because they do not adequately simulate the effects of failure mechanisms. As a result, product designs cannot be evaluated adequately and optimized for electrical and reliability performance. Needed are tools to simulate and evaluate the impact of design on changes in the electrical performance of the product due to the effects of failure mechanisms that occur with product use.

#### Approach

Develop/evaluate methodologies for CAD tools to determine the implications of circuit-design selections on the timewise degradation of product performance. Calculate electrical performance changes with time of circuit units (considered individually and in interaction with others) and of the product. Accomplish this by using predicted resistance increases with time of interconnect lines and vias in circuit units considering 1) current-densities expected for currents required by the circuit and linewidths selected and 2) calculated operating temperature, which includes the effects of joule heating in the circuit element and in other metal levels.

#### Project Objectives and Benefits

Objectives:

- 1. Develop and validate both AC and DC electromigration models

- 2. Develop methodologies for evaluating context-specific designs rules sensitive to the effects of DC and AC electromigration models

- 3. Standardize tools to include reliability considerations in product designs

- 4. Save costs by developing designs that optimize product performance and reliability

| Objective                                                                                                                                                     | Task | <b>Performance Metrics</b> | Deliverables | Due | \$K |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------|--------------|-----|-----|--|--|

| 1. Develop and<br>validate both AC<br>and DC<br>electromigration<br>models                                                                                    |      |                            |              |     |     |  |  |

| 2. Develop<br>methodologies for<br>evaluating context-<br>specific designs<br>rules sensitive to<br>the effects of DC<br>and AC<br>electromigration<br>models |      |                            |              |     |     |  |  |

| 3. Standardize<br>tools for including<br>reliability<br>considerations in<br>product designs                                                                  |      |                            |              |     |     |  |  |

| 4. Save costs by<br>through ability to<br>develop designs<br>that optimize<br>product<br>performance and<br>reliability                                       |      |                            |              |     |     |  |  |

| Universities, Suppliers, partners and dependencies: Total:                                                                                                    |      |                            |              |     |     |  |  |

Table 4

Project Overview: CAD Reliability Assessment Tools for Electromigration

### 5 IC PACKAGING TECHNOLOGY ISSUES/CONSTRAINTS

### 5.1 Introduction

Worldwide demand will continue for electronics systems that perform a variety of functions, such as information management, telecommunication, control, etc. Emphasis will accelerate on faster, smaller, lighter and especially cost-effective systems to perform these functions.